# DESIGN, ANALYSIS, AND MODELING OF FERROELECTRIC FIELD EFFECT TRANSISTOR

Thesis submitted for the award of the degree

of

## **DOCTOR OF PHILOSOPHY**

by

Snehlata Yadav

(Roll No. 2K19/PHDEC/03)

Under the supervision of

Prof. Rajeshwari Pandey

and

Dr. Sonam Rewari

**Department of Electronics & Communication Engineering**

## **DELHI TECHNOLOGICAL UNIVERSITY**

(Formerly Delhi College of Engineering)

Shahbad Daulatpur, Bawana Road, Delhi-110042, India

## Certificate

This is to certify that the thesis entitled "Design, Analysis, and Modeling of Ferroelectric Field Effect Transistor" being submitted by Ms. Snehlata Yadav (2K19/PHDEC/03) for the award of the degree of Doctor of Philosophy in the Department of Electronics and Communication Engineering, Delhi Technological University, Delhi, is the record of student's own work carried out by her under our supervision. The contents of this research work have not been submitted in part or fully to any other institute or university for the award of any degree.

#### Date:

Dr. Sonam Rewari

Department of Electronics and Communication Engineering Delhi Technological University Delhi-110042, India Prof. Rajeshwari Pandey

Department of Electronics and Communication Engineering Delhi Technological University Delhi-110042, India

# Acknowledgement

In the presence of the **Almighty**, all doubts fade and true wisdom shines. As I embark on this thesis journey, I humbly acknowledge and seek the grace of my Lord for His divine guidance, strength, and blessings.

I would like to begin by extending my heartfelt appreciation and admiration to **Prof. Rajeshwari Pandey**, my esteemed supervisor, who graciously agreed to guide me as a Ph.D. student and provided unwavering support throughout every phase of this research endeavour. Her humane and warm personal approach in all aspects, have given me the strength to carry out this research work on a steady and smooth course. She has consistently been a genuine source of inspiration for me, and I have always admired her as someone to learn from. I humbly acknowledge lifetime gratitude to her.

I also want to express my high regard to my co-supervisor, **Dr. Sonam Rewari** whose guidance, technical expertise, and constant efforts have been invaluable throughout this study and have made this an inspiring experience for me. Her persistent and tireless dedication has made it possible to complete the thesis work. I am highly thankful that I had the opportunity of working under her guidance. I have also learned invaluable life lessons from her, which I aspire to carry beyond my doctoral research. From the core of my heart, I offer my deepest thanks to her and always feel immensely blessed to have her by my side.

A special word of mention for my senior faculties, **Prof. Neeta Pandey**, and **Prof. Dinesh Kumar** from whom I received positive support and suggestions all the time.

I am also thankful to my **DRC** members for their patient listening, and valuable feedback throughout the process. I would like to thank the Department of Electronics and Communication Engineering, DTU Delhi, for providing the facilities and financial support in

the completion of my thesis work. I also recognize the very helpful and warm nature of all the non-teaching faculty of the department.

Without seniors and friends like Parveen Rani, Ajishek Raj, Suryakant Shukla, Kamakshi Rautela, Bhawna Sharma, Nikhil Singh, Rahul Kumar, Anu, Ankit, Akanksha, Aapurva Kaul, Shivani Yadav, Dhruv Sharma, Roli Kushwaha and Shikha it would have become very difficult to cope-up with the ups and downs faced during the last four years. I am grateful to them for providing me with moral support during the entire course of my research work.

I would also like to extend my gratitude to my long-time steadfast friends, **Shradhya Singh**, **Tawseef Ahmad**, **Manu Singh**, **Asma**, and **Mehran Manzoor**, whose unwavering friendship and support have been an invaluable source of strength and companionship throughout my journey. Their constant support has made the journey smooth and filled with opportunities, even during times when it seemed distant and challenging.

I want to express my heartfelt regard to my family members which includes my parents Mr. Prem Prakash Yadav and Mrs. Sushila Yadav, my sisters Anju Yadav and Ranju Yadav, my brothers Satya Yadav and Gyan Yadav for their unconditional love, utmost care, endless sacrifice, ceaseless support, and wholehearted blessing throughout. I wish to acknowledge the love and support of my father-in-law Mr. Subhash Yadav and mother-in-law Mrs. Durgavati Yadav.

I could not end this note without a special mention of thanks to my loving husband **Mr. Pawan**Yadav for his constant support and encouragement. He always believed in me and motivated me to do my best. I gratefully acknowledge the unwavering strength he has bestowed upon me, standing firmly by my side through every obstacle and triumph, offering support and resilience during both difficult and joyous times.

Snehlata Yadav

# **Table of Contents**

| Certificate                                             | i    |

|---------------------------------------------------------|------|

| Acknowledgment                                          | ii   |

| List of figures                                         | viii |

| List of Tables                                          | xiii |

| List of Symbols                                         | xiv  |

| List of Abbreviations                                   | xvi  |

| 1 Introduction                                          | 1    |

| 1.1 Evolution of MOSFET                                 | 1    |

| 1.2 MOSFET Scaling and Challenges                       | 2    |

| 1.3 Device Architectures to Overcome Scaling Challenges | 5    |

| 1.3.1 Multigate MOSFETs                                 | 5    |

| 1.3.1.1 Double Gate MOSFET                              | 5    |

| 1.3.1.2 FinFET                                          | 6    |

| 1.3.2 Junctionless Transistor                           | 7    |

| 1.3.3 Junctionless Accumulation Mode FET                | 8    |

| 1.3.4 Steep Subthreshold Slope Devices                  | 9    |

| 1.3.4.1 Tunnel FET (TFET)                               | 10   |

| 1.3.4.2 Impact Ionization MOS (IMOS)                    | 11   |

| 1.3.4.3 Ferroelectric based Negative Capacitance FET    | 12   |

| 1.4 Motivation                                          | 13   |

|   | 1.5 Thesis Outline                                                              | .14 |

|---|---------------------------------------------------------------------------------|-----|

| 2 | Literature Review                                                               | .17 |

|   | 2.1 Overview                                                                    | .17 |

|   | 2.2 The Concept of Ferroelectric Negative Capacitance                           | .17 |

|   | 2.2.1 Negative capacitance: Definition                                          | .17 |

|   | 2.2.2 Realization of Negative Capacitance through ferroelectric material        | .18 |

|   | 2.2.3 Landau Theory of Negative Capacitance                                     | .19 |

|   | 2.3 NCFET: Steep Switching                                                      | .20 |

|   | 2.4 Literature Review                                                           | .21 |

|   | 2.5 Research Gaps                                                               | .30 |

|   | 2.6 Research Objectives                                                         | .30 |

| 3 | Single Gate Junctionless Accumulation Mode Ferroelectric FET: Simulation Study. | .31 |

|   | 3.1 Introduction                                                                | .32 |

|   | 3.2 Existing Device Topologies                                                  | .34 |

|   | 3.2.1 JAM Structure                                                             | .34 |

|   | 3.2.2 Ferroelectric FET                                                         | .35 |

|   | 3.3 Proposed Structure & Simulation Parameters                                  | .35 |

|   | 3.4 Device fabrication and calibration                                          | .38 |

|   | 3.4.1 Need for fabrication                                                      | .38 |

|   | 3.4.2 Proposed fabrication details                                              | .38 |

|   | 3.5 Results & Discussions                                                       | .40 |

| 3.5.1 Analog/RF performance parameters                                               |

|--------------------------------------------------------------------------------------|

| 3.5.3 Temperature variation on DC parameters53                                       |

| 3.6 Summary                                                                          |

| 4 Double Gate Junctionless Accumulation Mode Ferroelectric FET: Analytical Study 57  |

| 4.1. Introduction58                                                                  |

| 4.2 Existing Device Topologies59                                                     |

| 4.2.1 Double Gate structure59                                                        |

| 4.2.2 Junctionless Ferroelectric FET                                                 |

| 4.2. Device Structure & Simulation                                                   |

| 4.3. Calibration & Fabrication Feasibility62                                         |

| 4.4. Model65                                                                         |

| 4.4.1. Surface potential & threshold voltage65                                       |

| 4.4.2. Drain current model69                                                         |

| 4.4.3. Gain, transconductance & subthreshold swing70                                 |

| 4.5. Model Validation & Discussion71                                                 |

| 4.5.1 Impact of ferroelectric thickness and channel thickness on device parameters71 |

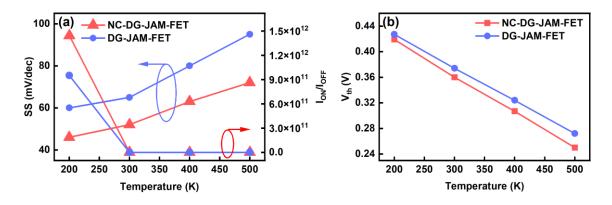

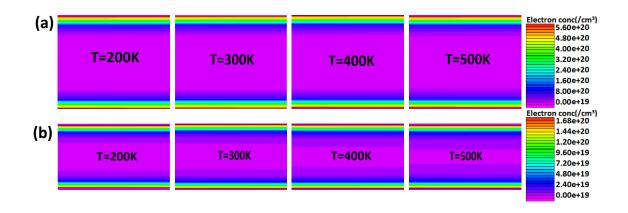

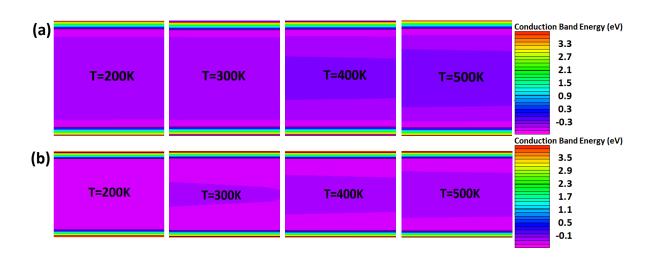

| 4.5.2. Temperature Analysis of double gate JAM-FET with and without ferroelectric79  |

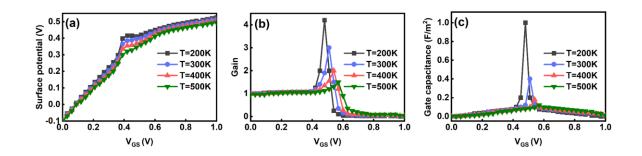

| 4.5.3. Analytical results showing the effects of temperature on NC-DG-JAM-FET82      |

| 4.6. Summary84                                                                       |

| 5 Double Gate Ferroelectric FET for Biosensing Application86                         |

| 5.1 Introduction                                                                     |

| Bibliography                                                            | 105 |

|-------------------------------------------------------------------------|-----|

| Publications                                                            | 104 |

| 6.2 Future Scope                                                        | 103 |

| 6.1 Summary of Thesis Work                                              | 101 |

| 6 Conclusions and Future Scope                                          | 101 |

| 5.5. Summary                                                            | 100 |

| 5.4.2. Impact of biomolecule concentration on DC-NC-JAM-FET:            | 97  |

| 5.4.1. DC-NC-JAM-FET as a Bio-sensing Device for different biomolecules | 93  |

| 5.4. Results and Discussion                                             | 93  |

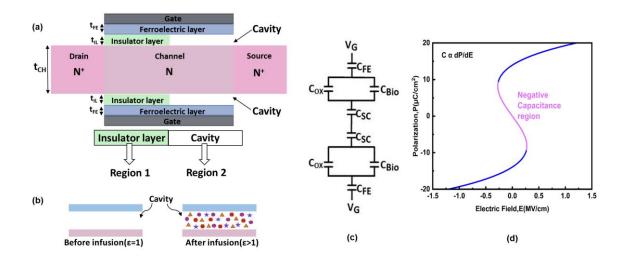

| 5.3. Analytical Model Formulation                                       | 91  |

| 5.2. Device Architecture and Simulation                                 | 89  |

# **List of figures**

| Fig. 1.1 Scaling Trend of MOSFET                                                              | 2      |

|-----------------------------------------------------------------------------------------------|--------|

| Fig. 1.2 Drain Induced Barrier Lowering (DIBL)                                                | 3      |

| Fig. 1.3 Hot Carrier Effects                                                                  | 3      |

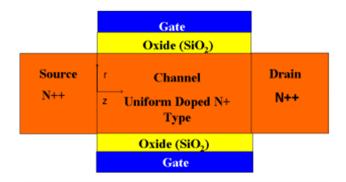

| Fig. 1.4 Structure of Double Gate MOSFET (a) Symmetric and (b) Asymmetric                     | 5      |

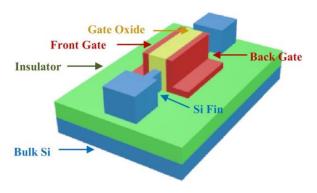

| Fig. 1.5 Schematic 3D view of FinFET                                                          | 6      |

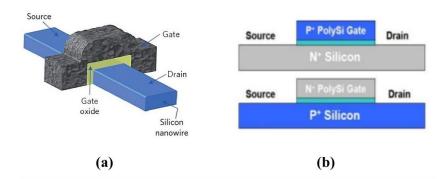

| Fig. 1.6 Junctionless Transistor (a) 3-D view (b) 2-D cross sectional view                    | 7      |

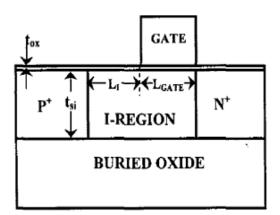

| Fig. 1.7 Schematic structure of Junctionless Accumulation Mode FET                            | 8      |

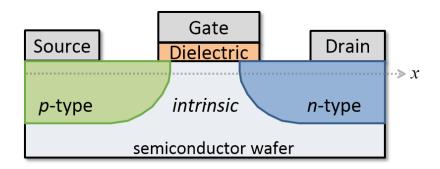

| Fig. 1.8 Basic structure of Tunnel FET.                                                       | 10     |

| Fig. 1.9 Basic structure of an N-channel IMOS                                                 | 11     |

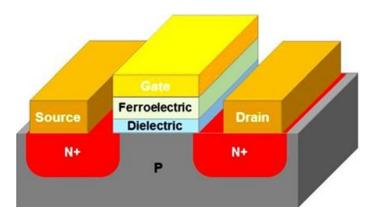

| Fig. 1.10 Schematic structure of a Ferroelectric Negative Capacitance FET                     | 12     |

| Fig. 2.1 Charge-voltage and energy landscapes of (a) Positive capacitor and (b) Neg           | gative |

| capacitor                                                                                     | 18     |

| Fig. 2.2 The energy double well diagram of a ferroelectric material. The area under the d     | ashed  |

| region represents negative capacitance region                                                 | 18     |

| Fig. 2.3 Polarization characteristics of a ferroelectric material according to Landau theor   | y20    |

| Fig. 2.4 (a) Ferroelectric material based negative capacitance FET (b) equivalent capacitance | itance |

| model                                                                                         | 21     |

| Fig. 3.1 A schematic representation of JAM-FE-FET                                             | 35     |

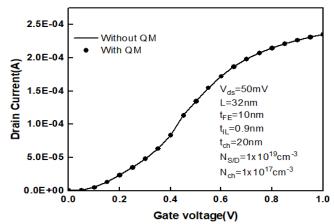

| Fig. 3.2 The effect of the Quantum Model (QM) on the drain current                            | 38     |

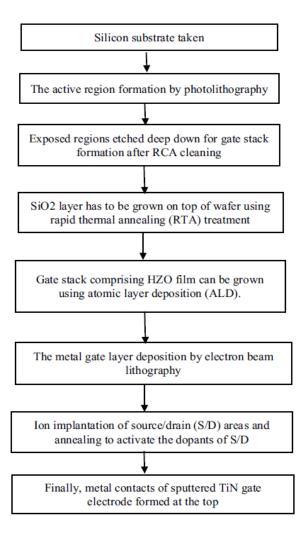

| Fig. 3.3 Fabrication flowchart of proposed JAM-FE-FET                                         | 39     |

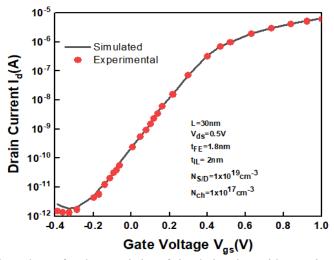

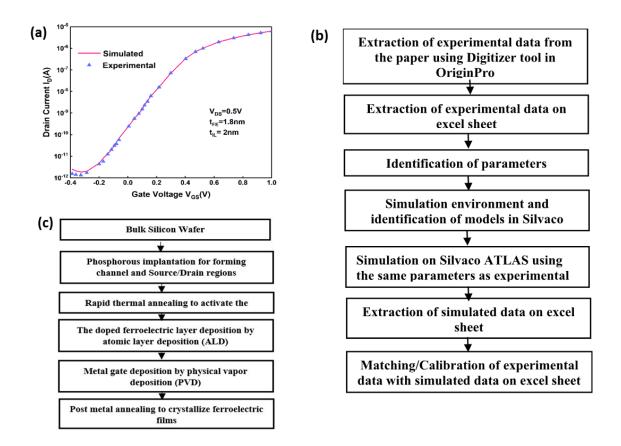

| Fig. 3.4 Calibrated transfer characteristics of simulation data with experimental data [147].40                             |

|-----------------------------------------------------------------------------------------------------------------------------|

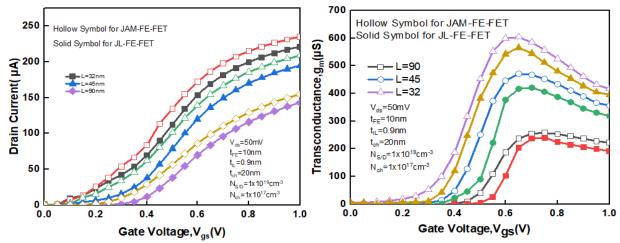

| Fig. 3.5. (a) Drain current variation with $V_{gs}$ (b) Transconductance variation with $V_{gs}$ 41                         |

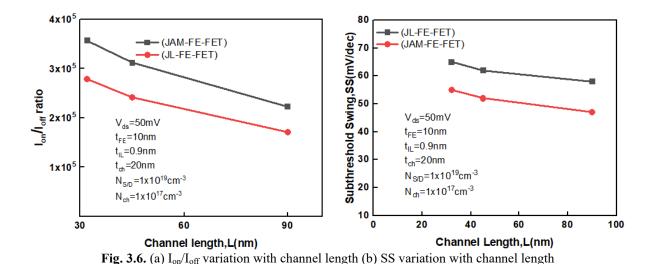

| Fig. 3.6. (a) I <sub>on</sub> /I <sub>off</sub> variation with channel length (b) SS variation with channel length41        |

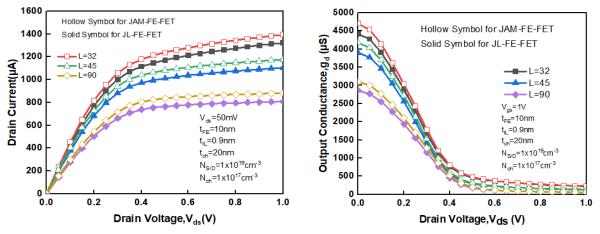

| Fig. 3.7. (a) Drain current variation with $V_{ds}$ (b) Output conductance variation with $V_{ds}$ 43                       |

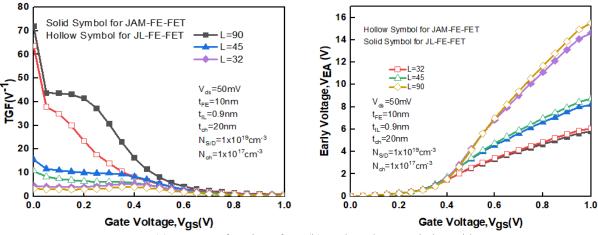

| Fig. 3.8. (a) TGF as a function of $V_{gs}$ (b) Early Voltage variation with $V_{gs}$ 44                                    |

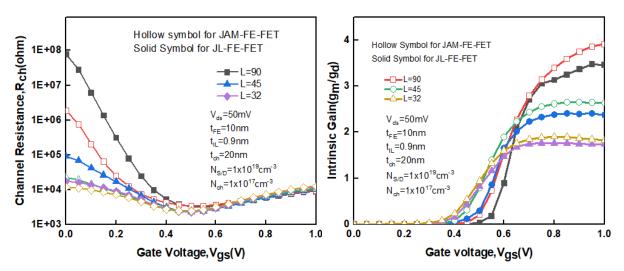

| Fig. 3.9. (a) Channel resistance variation with $V_{gs}$ (b) Intrinsic gain variation with $V_{gs}$ 45                      |

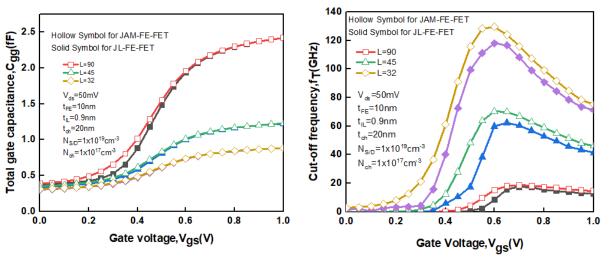

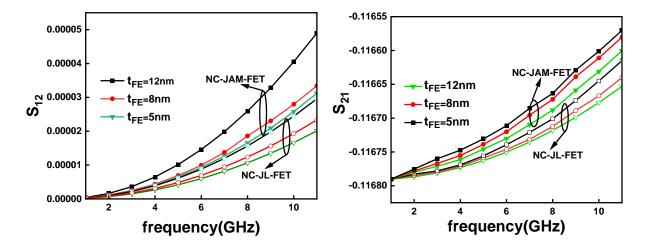

| Fig. 3.10. (a) $C_{GG}$ variation with $V_{gs}$ (b) $f_T$ variation with $V_{gs}$                                           |

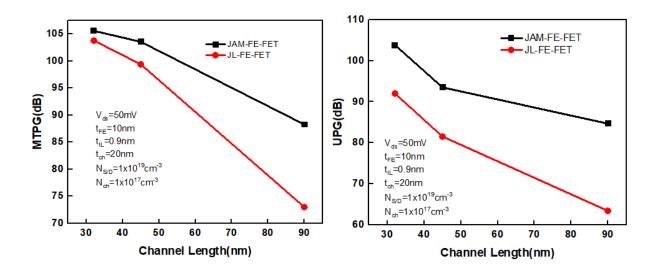

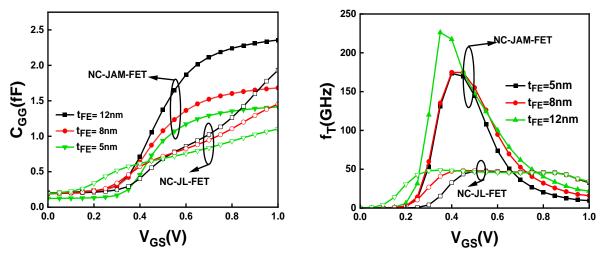

| Fig. 3.11. (a) MTPG variation with channel length (b) UPG variation with channel length47                                   |

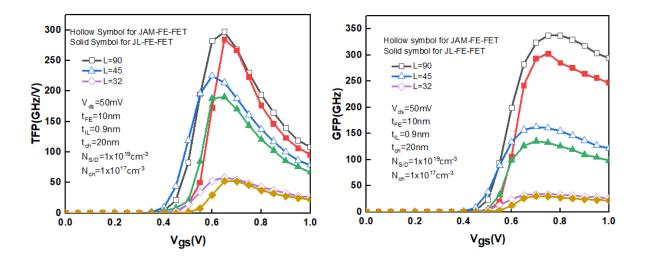

| Fig. 3.12. (a) TFP variation with $V_{gs}$ (b) GFP variation with $V_{gs}$                                                  |

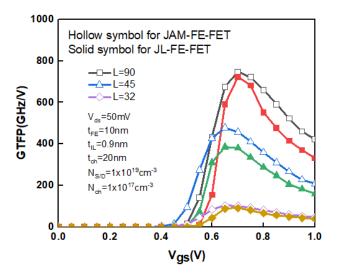

| Fig. 3.13. GTFP variation with V <sub>gs</sub>                                                                              |

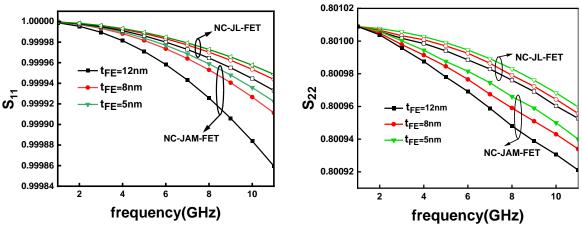

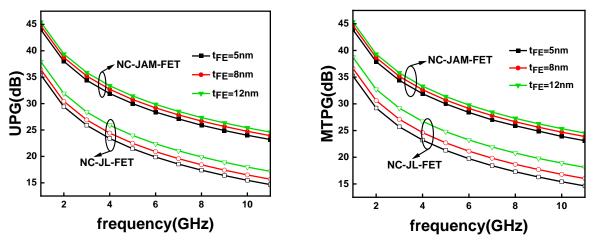

| <b>Fig. 3.14.</b> (a) Variation of S <sub>11</sub> with frequency (b) Variation of S <sub>22</sub> with frequency50         |

| <b>Fig. 3.15.</b> (a) Variation of S <sub>12</sub> with frequency (b) Variation of S <sub>21</sub> with frequency51         |

| <b>Fig. 3.16</b> (a) Variation of C <sub>GG</sub> with V <sub>GS</sub> (b) Variation of f <sub>T</sub> with V <sub>GS</sub> |

| Fig. 3.17. (a) Variation of UPG with frequency (b) Variation of MTPG with frequency52                                       |

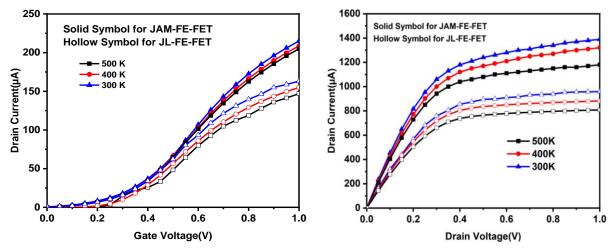

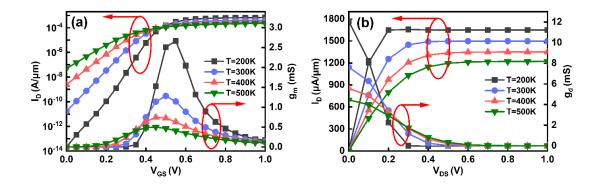

| Fig. 3.18 (a) Input characteristics at different temperatures (b) Output characteristics at                                 |

| different temperatures53                                                                                                    |

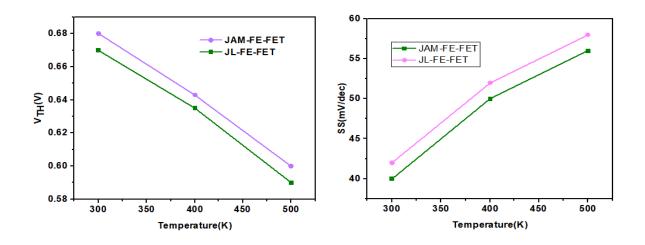

| Fig. 3.19. (a) V <sub>TH</sub> variation at different temperatures (b) SS variation at different temperatures               |

| 54                                                                                                                          |

| <b>Fig. 3.20</b> I <sub>on</sub> /I <sub>off</sub> variation at different temperatures                                      |

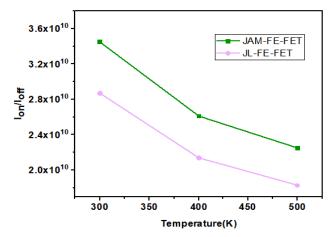

| Fig. 4.1. (a) Structure of Double Gate Junctionless Accumulation Mode Negative Capacitance                                  |

| FET (DG-JAM-NC-FET). (b) Schematic of energy bands of the device in NC region towards                                       |

| the direction of the thickness of the channel. The channel bent upward in the accumulation                                     |

|--------------------------------------------------------------------------------------------------------------------------------|

| mode                                                                                                                           |

| Fig. 4.2. (a) Calibration of transfer characteristics of simulated data with experimental (b)                                  |

| Calibration process flow and (c) Fabrication flowchart for the proposed device                                                 |

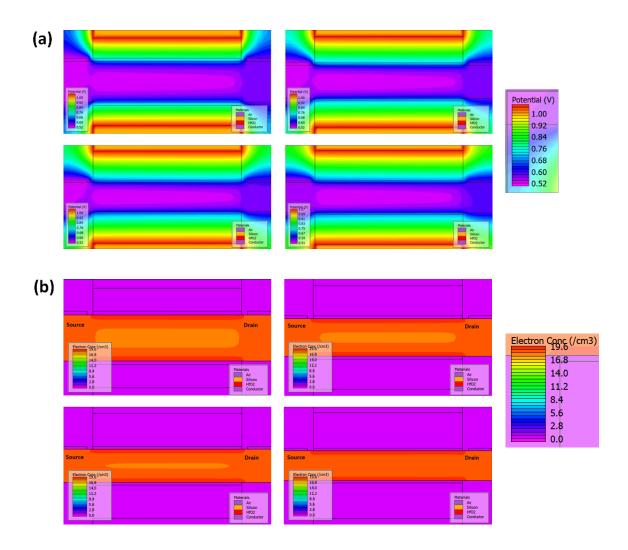

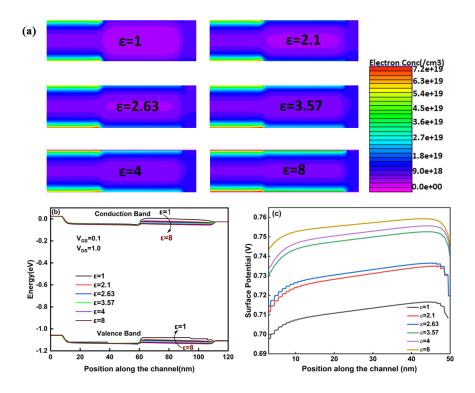

| Fig. 4.3. Contour plots for (a) potential and (b) electron concentration at various ferroelectric                              |

| thicknesses (t <sub>FE</sub> = 5, 8, 10, 12 nm)64                                                                              |

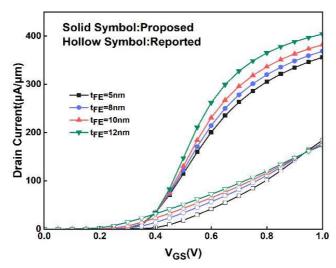

| Fig. 4.4. A comparison of the transfer characteristics as reported in Ref. [23] with the results                               |

| of the proposed model71                                                                                                        |

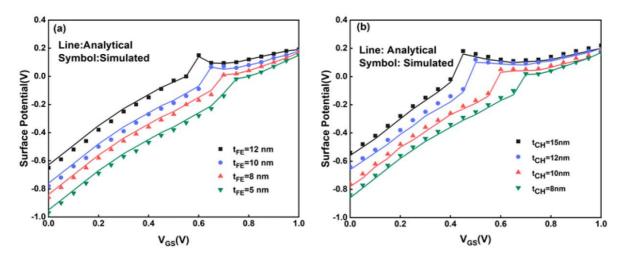

| Fig. 4.5. Surface potential of DG-JAM-NC-FET with respect to gate voltage for different (a)                                    |

| ferroelectric thicknesses and (b) channel thicknesses compared with simulated results72                                        |

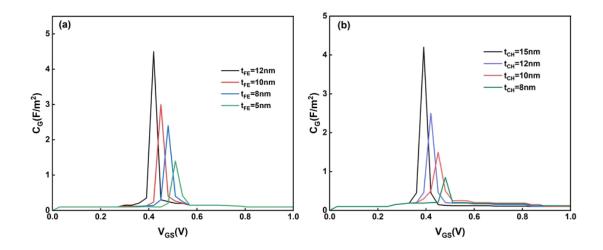

| Fig. 4.6. Gate capacitance against gate voltage for various (a) thicknesses of ferroelectric layer                             |

| and (b) silicon channel thicknesses of the model73                                                                             |

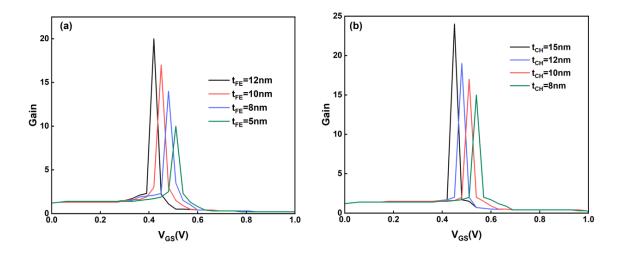

| Fig. 4.7. Gain $(d\phi_{sp}/dv_{gs})$ variation with gate voltage at different (a) ferroelectric layer                         |

| thicknesses and (b) channel thicknesses                                                                                        |

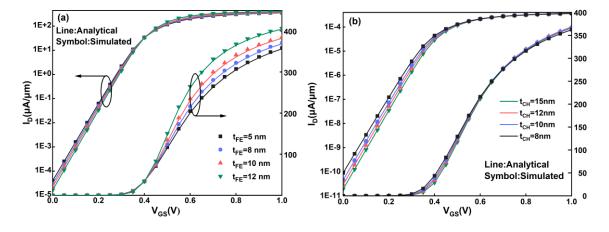

| Fig. 4.8. (a) Transfer characteristics of the model at different ferroelectric layer thicknesses and                           |

| (b) transfer characteristics of the model at different silicon channel thicknesses, compared with                              |

| simulated data in both logarithmic (primary axis) and linear scale (secondary axis)74                                          |

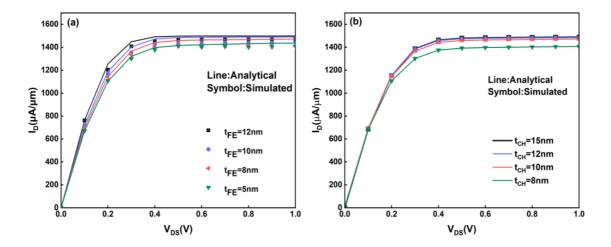

| Fig. 4.9. Output characteristics of the model at different (a) ferroelectric layer thicknesses and                             |

| (b) channel thicknesses, compared with simulated data75                                                                        |

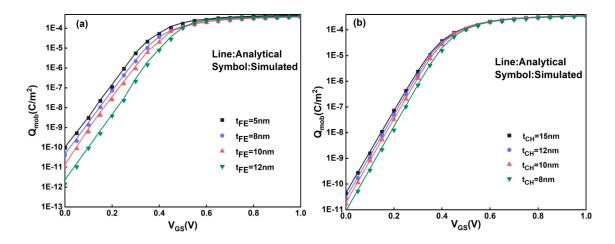

| Fig. 4.10. Mobile charge density variation with gate voltage at various (a) ferroelectric layer                                |

| thicknesses and (b) channel thicknesses, compared with simulated results76                                                     |

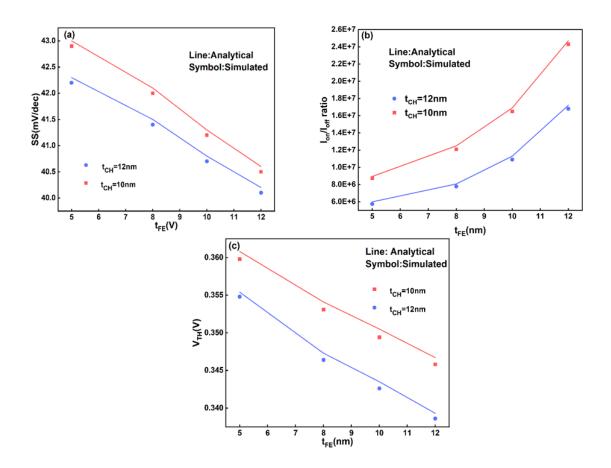

| Fig. 4.11. (a) SS (b) I <sub>on</sub> /I <sub>off</sub> and (c) Threshold voltage variation with ferroelectric layer thickness |

| at different channel thicknesses.                                                                                              |

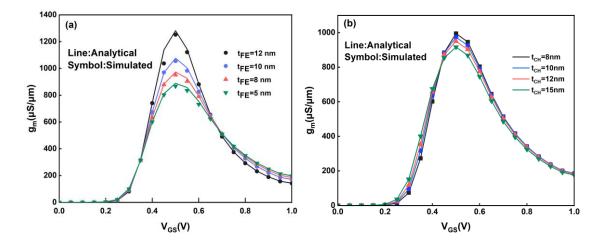

| Fig. 4.12. Transconductance as a function of gate voltage at various (a) ferroelectric layer                 |

|--------------------------------------------------------------------------------------------------------------|

| thicknesses (b) channel thicknesses, compared with simulated results                                         |

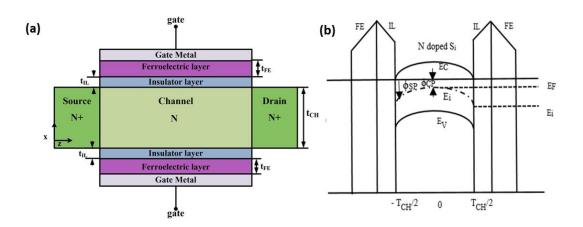

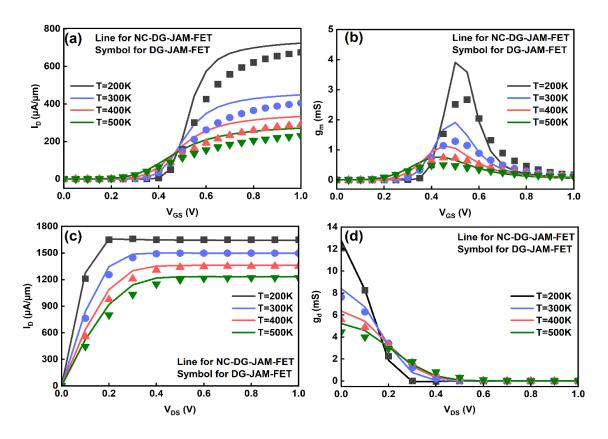

| Fig. 4.13. Transfer characteristics (a), transconductance (b), output characteristics (c) and                |

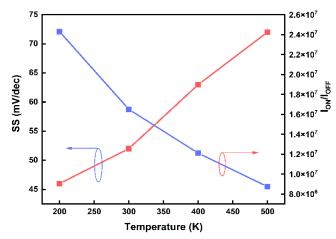

| output conductance (d) of the devices with temperature variation79                                           |

| Fig. 4.14. (a) SS and $I_{ON}/I_{OFF}$ ratio. (b) Threshold voltage of the devices with temperature          |

| variation80                                                                                                  |

| Fig. 4.15. Contour plot for electron concentration of DG-JAM-FET (a) and NC-DG-JAM-FET                       |

| (b) at different temperatures80                                                                              |

| Fig. 4.16. Contour plot for conduction band energy of DG-JAM-FET (a) and NC-DG-JAM-                          |

| FET (b) at different temperatures81                                                                          |

| Fig. 4.17. Surface potential (a), gain (b), gate capacitance (c) as a function of V <sub>GS</sub> at various |

| temperatures. 82                                                                                             |

| Fig. 4.18. Transfer characteristics and transconductance (a), output characteristics and output              |

| conductance (b) of NC-DG-JAM-FET at various temperatures                                                     |

| <b>Fig. 4.19.</b> SS and I <sub>ON</sub> /I <sub>OFF</sub> ratio at different temperature83                  |

| Fig. 5.1. (a) Structure of DC-NC-JAM-FET biosensor, (b) biomolecule infusion in the cavity                   |

| region, (c) equivalent capacitance model (d) P-E curve for ferroelectric illustrating the negative           |

| capacitance region89                                                                                         |

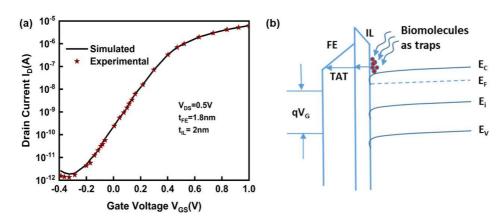

| Fig. 5.2. (a) Calibration with the reported work. (b) Energy band diagram showing trap assisted              |

| tunneling (TAT) of biomolecules through ferroelectric layer90                                                |

| Fig. 5.3. (a) The contour plot for electron concentration with different biomolecules (b) Energy             |

| band plots against position along the channel showing the conduction and valence band of DC-                 |

| NC-JAM-FET at different dielectric constants (c) Surface potential along the lateral direction     |

|----------------------------------------------------------------------------------------------------|

| for different dielectric constants                                                                 |

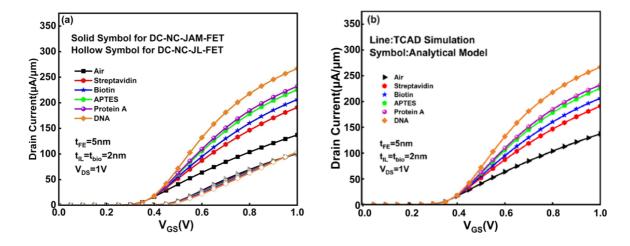

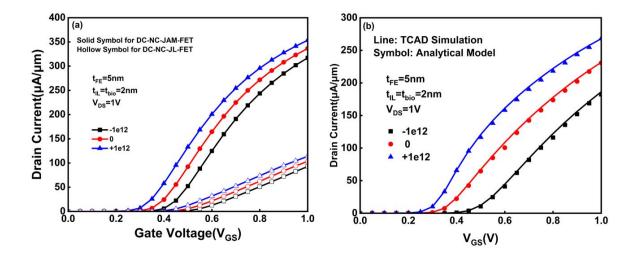

| Fig. 5.4. (a) Drain current characteristics of the devices for different biomolecule dielectric    |

| constant, (b) analytical drain current characteristics95                                           |

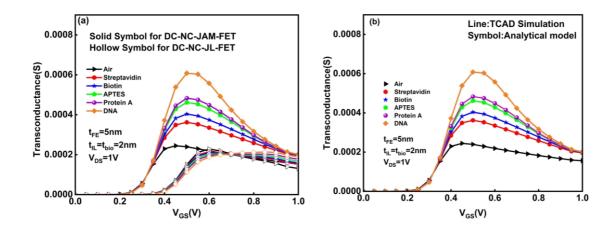

| Fig. 5.5. (a) Transconductance of different devices for different dielectric constant, (b)         |

| analytical transconductance variation of the proposed device for various biomolecules96            |

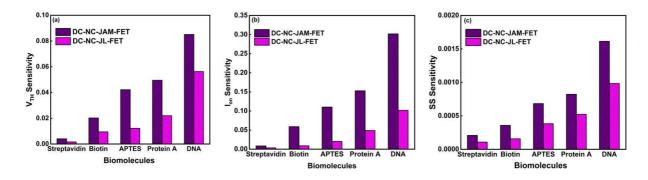

| Fig. 5.6. Comparison of different devices with respect to (a) Threshold voltage sensitivity, (b)   |

| On Current sensitivity and (c) SS sensitivity at different dielectric constants96                  |

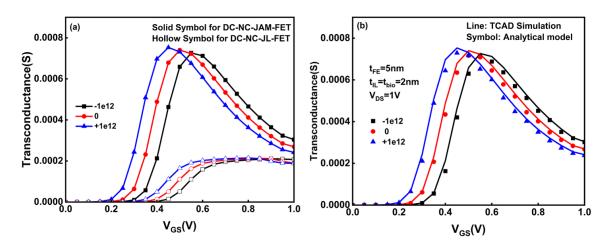

| Fig. 5.7. (a) Drain current characteristics of the devices for different biomolecule concentration |

| (b) Analytical drain current characteristics of the proposed device97                              |

| Fig. 5.8. (a) Transconductance of diiferent devices for various biomolecule concentartions (b)     |

| Analytical transconductance values for various biomolecule concentrations98                        |

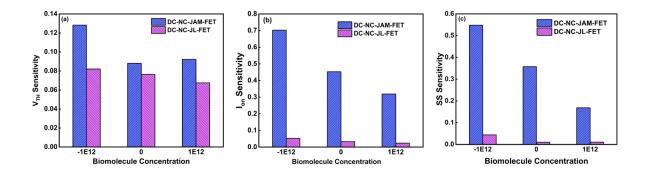

| Fig. 5.9. Sensitivity comparison of different devices in terms of (a) threshold voltage (b) On     |

| current (c) Subthreshold Swing at different biomolecule concentrations                             |

# **List of Tables**

| Table 2.1 Comparative summary of NCFET structures                    | 24 |

|----------------------------------------------------------------------|----|

| Table 3.1 Physical models used in the simulation                     | 36 |

| Table 3.2. Various parameters employed for the device simulation     | 37 |

| Table 3.3. Properties of ferroelectric material (HZO)                | 37 |

| <b>Table 3.4.</b> I <sub>on</sub> /I <sub>off</sub> Ratio            | 42 |

| <b>Table 3.5.</b> Performance parameters at channel length L = 32 nm | 49 |

| Table 4.1. Device and Material Parameters                            | 61 |

| Table 5.1. Biomolecules and corresponding dielectric constants       | 90 |

## **List of Symbols**

$\phi$  Electrostatic channel potential of the device

$N_D$  Doping concentration in channel region

$\varepsilon_{si}$  Silicon permittivity

$\varepsilon_{IL}$  Insulator/oxide permittivity

q Electronic charge

V Electron quasi-fermi potential

$\phi_{SP}$  Surface Potential. In simplest terms, it is the difference between the

voltage at the surface of the MOSFET capacitor.

$\phi_{CP}$  Center Potential

$\phi_M$  Work function of metal

$\phi_{si}$  Work function of semiconductor

$\chi$  Electron affinity

$E_g$  Energy band gap

$N_D^+$  Doping concentration in Source/drain regions

$t_{CH}$  Thickness of the channel layer

$t_{FE}$  Thickness of the ferroelectric layer

$t_{IL}$  Thickness of the insulator layer

$Q_{TOT}$  Total charge density over the entire channel(per unit gate area)

$V_{FE}$  Drop across ferroelectric layer

$V_{IL}$  Drop across insulator layer

$V_{FB}$  Flat band voltage which results due to the difference in the work

function of the metal and semiconductors

$V_{th}$  Threshold voltage

$Q_{MOB}$  Mobile charge density over the entire channel

$V_T$  Thermal Voltage

$I_D$  Drain current

$V_{GS}$  Gate to source voltage

*k* Boltzmann constant

T Temperature

$T_c$  Curie temperature

$C_{TOT}$  Total gate capacitance

$C_{IL}$  Capacitance across insulator layer

$C_S$  Semiconductor capacitance

$C_{FE}$  Ferroelectric capacitance

$C_G$  Gate stack capacitance

Q Surface charge

$\alpha$ ,  $\beta$ ,  $\gamma$  The Landau-coefficients that depends on the ferroelectric material

properties typical of HZO

$g_m$  Transconductance

$V_{EA}$  Early Voltage

$A_V$  Intrinsic Gain

*W/L* Width to length ratio of the transistor

$\mu$  Mobility of the charge carrier

U Ferroelectric's free energy density

E External applied electric field

P Polarization

## List of Abbreviations

ALD Atomic Layer Deposition

APTES (3-Aminopropyl)triethoxysilane

CLM Channel Length Modulation

CMD Carrier Mobility Degradation

CMOS Complementary Metal Oxide Semiconductor

CNFET Carbon Nanotube Field Effect transistor

CVT Concentration, Voltage, and Temperature

DG Double Gate

DGFET Double Gate Field Effect transistor

DGFJL Double Gate Ferroelectric Junctionless

DGNCFET Double Gate Negative Capacitance Field Effect Transistor

DIBL Drain Induced Barrier Lowering

DNA Deoxyribonucleic Acid

FE Ferroelectric

GAA Gate-All-Around

GFP Gain Frequency Product

GTFP Gain Transconductance Frequency Product

HCI Hot Carrier Injection

HZO Hafnium Zirconium Oxide

IC Integrated Circuits

IMOS Impact Ionization MOS

JAM Junctionless Accumulation Mode

JAMFET Junctionless Accumulation Mode Field Effect Transistor

JLGAA Junctionless Gate-All-Around

JLNW Junctionless Nanowire

JLT Junctionless Transistor

LK Landau Khalatnikov

MFIS Metal Ferroelectric Insulator Semiconductor

MFMIS Metal Ferroelectric Metal Insulator Semiconductor

MFS Metal Ferroelectric Semiconductor

MOSFET Metal Oxide Semiconductor Field Effect Transistor

MTPG Maximum Transducer Power Gain

NCFET Negative Capacitance Field Effect Transistor

NCTFET Negative Capacitance Tunnel Field Effect Transistor

PVD Physical Vapour Deposition

PZT Lead Zirconate Titanate

RCA Radio Corporation of America

RF Radio frequency

RTA Rapid Thermal Annealing

SBT Strontium Bismuth Tantalite

SCE Short Channel Effects

SRAM Static Random Access Memory

SRH Shockley-Read-Hall

SS Subthreshold Swing

TAT Trap Assisted Tunneling

TGF Transconductance Generation Factor

TFET Tunnel Field Effect Transistor

TFP Transconductance Frequency product

UPG Unilateral Power Gain

UTB Ultra thin body

VLSI Very Large Scale Integration

# **Chapter 1**

## Introduction

#### 1.1 Evolution of MOSFET

The mid-20th century marked the beginning of the Metal-Oxide-Semiconductor Field-Effect Transistor (MOSFET) era. The invention of the MOS (Metal-Oxide-Semiconductor) capacitor laid the groundwork for the MOSFET. Lilienfeld, a physicist, patented the concept of a field-effect transistor-like device based on a thin layer of semiconductor material in the 1920s [1]. Lilienfeld's work, however, remained purely theoretical. In the late 1950s, researchers began investigating the electrical properties of MOS capacitors [2]. M. Atalla and D. Kahng, physicists at Bell Laboratory, made substantial contributions to the invention of the MOSFET in 1959 [3]. They established the viability of fabricating a functional MOS capacitor by depositing a thin silicon dioxide (SiO<sub>2</sub>) layer on a silicon substrate and using metal connections. They also observed current flow control across the oxide layer by applying a voltage to the metal gate. Later in 1963, Chih-Tang Sah and Frank Wanlass at Fairchild Semiconductor introduced the planar MOSFET [4]. The planar MOSFET used a more feasible structure, including a metal gate, a thin oxide layer, and a p-n junction beneath the channel region. This design enabled better device characteristics such as lower power consumption and faster switching speed. Throughout the 1960s and 1970s, researchers and engineers achieved substantial advances in MOSFET technology. During this time, notable advances included the advent of complementary MOS (CMOS) logic, which used both n-channel and p-channel MOSFETs for improved power efficiency and noise immunity [5]. Furthermore, scaling down MOSFETs, resulting in reduced transistor size and higher integration density, became a major focus.

### 1.2 MOSFET Scaling and Challenges

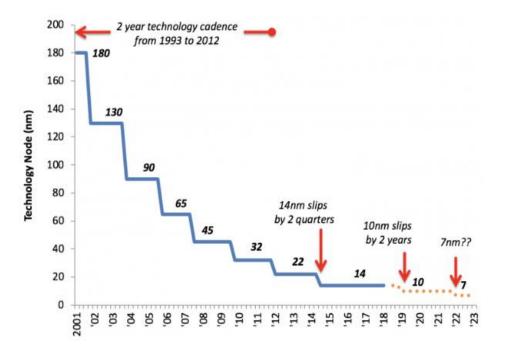

MOSFET scaling is the ongoing miniaturization of MOSFETs in order to improve their performance and density on integrated circuits. In 1965, Gordon Moore, co-founder of Intel, projected that the number of transistors on a semiconductor chip would double every two years, known as Moore's Law [6]. This doubling of transistor count has been made feasible by MOSFET scaling, which allows for smaller transistor sizes and the incorporation of a higher number of transistors on a chip as shown in Fig. 1.1 [7]. Moore's Law has been a guiding principle in the semiconductor industry for several decades, precisely describing the pattern of rising transistor density and performance. The fundamental reason for scaling MOSFETs is to minimize their size, which has various advantages, including increased performance, higher density, cost reduction, and low power consumption. However, as MOSFETs are scaled down to smaller dimensions, many significant challenges arise. Some of the significant challenges [8] are explained in following subsections.

Fig. 1.1 Scaling Trend of MOSFET [7]

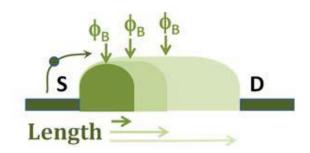

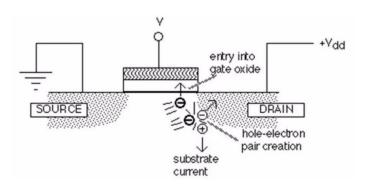

1.2.1 Short-channel effects: Short channel effects (SCEs) occur in MOSFETs when the channel length becomes comparable to the carrier mean free path or depletion zone width. As the channel length in modern integrated circuits reduces, these effects become more substantial, posing issues in transistor performance and device scalability. As channel lengths shorten, short-channel effects such as drain-induced barrier lowering (DIBL), hot carrier effects, mobility reduction, and increased leakage current become more evident [9]. The DIBL effect causes electrostatic coupling between the source and drain, rendering the gate inefficient as shown in Fig. 1.2 [10]. The power dissipation is increased by the leakage current. Hot carrier effects (as shown in Fig. 1.3) substantially degrade MOSFET performance and cause the device to behave differently than long-channel devices [11].

Fig. 1.2 Drain Induced Barrier Lowering (DIBL) [10]

Fig. 1.3 Hot Carrier Effects [11]

- 1.2.2 Variability: Scaling introduces variances in transistor properties due to manufacturing processes and statistical variations. Quantum mechanical effects become more pronounced, adding to variability. Variations occur due to factors such as the number of carriers in the channel, carrier tunneling, and scattering phenomena [12]. These variances can have a negative impact on device performance and yield, making it difficult to ensure consistent and dependable operation over a large number of transistors.

- 1.2.3 Gate oxide thickness: As gate lengths are reduced, the thickness of the gate oxide layer must be reduced as well. However, decreasing the oxide thickness increases gate leakage currents, which can impact the power consumption and reliability of the device [13]. The thinner gate oxide raises concerns about reliability issues like hot carrier injection (HCI) and oxide breakdown. High-energy carriers affect the gate oxide, causing deterioration and potential failure.

- 1.2.4 Heat dissipation: As transistor density increases, so does power density, resulting in increased heat generation. As devices shrink, there is not as much space for heat to dissipate. Due to the smaller physical dimensions, thermal paths, such as the distance between the transistor and the heat sink, and the availability of metal layers for efficient heat conduction, are limited. This constraint makes it more difficult to manage heat dissipation, which might have an impact on device durability and performance [14].

It's crucial to remember that, despite the fact that Moore's Law has been valid for many years, maintaining traditional MOSFET scaling over certain logical and technical limits is becoming more difficult. To continue expanding semiconductor technology and sustaining the spirit of Moore's Law, the industry is investigating alternate transistor topologies, novel materials, and innovative manufacturing procedures.

#### 1.3 Device Architectures to Overcome Scaling Challenges

In order to tackle the numerous challenges associated with miniaturization, including issues like short channel effects, complex fabrication requirements, and a notable rise in static power dissipation, researchers have proposed and extensively investigated several device technologies. These device technologies help in improving the gate control over the channel which results in lower leakage current, improved analog performance, and low power dissipation. Here, we outline some of the device technological advancements that aim to overcome the scaling challenges.

#### 1.3.1 Multigate MOSFETs

Multigate transistors, commonly known as multi-gate FETs, are a type of transistor architecture in which the channel current is controlled by numerous gates. When compared to standard planar MOSFETs, they provide better electrostatic control, lower leakage current, and higher performance [15]. The following are the most prevalent types of multigate transistors:

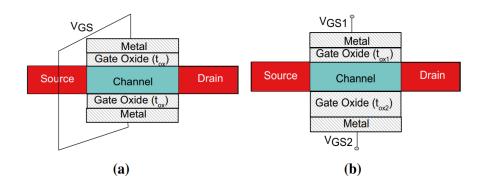

#### 1.3.1.1 Double Gate MOSFET

A Double Gate MOSFET (DG MOSFET) is a transistor with two gates rather than one. It is also referred to as a dual-gate or twin-gate MOSFET.

Fig. 1.4 Structure of Double Gate MOSFET (a) Symmetric and (b) Asymmetric [17]

The twin gate configuration allows for greater control over the flow of current through the transistor. A DG MOSFET has two gate electrodes, one on each side of the channel region. When the transistor is turned on, current flows across the channel. The gates are isolated from the channel by a thin insulating layer termed gate oxide [16]. DG MOSFET can be configured in two ways: Asymmetric DG MOSFET and Symmetric DG MOSFET as shown in Fig. 1.4 [17]. The front and back gates in Asymmetric DG are biased independently and also the thicknesses of oxide layers are distinct. In Symmetric DG, both oxide layers have the same thickness, and the two gates are connected by a common bias. The double gate configuration has various advantages over standard MOSFETs, including better control over the channel region, lower leakage current, higher drive current, better scalability, and improved analog performance [18].

#### 1.3.1.2 FinFET

A FinFET (Fin Field-Effect Transistor) is a transistor structure that has grown in prominence in semiconductor technology. As feature sizes fall, it is intended to overcome the limitations of classic planar MOSFETs (Metal-Oxide-Semiconductor Field-Effect Transistors). The channel in a FinFET is constructed as a thin, vertical fin that protrudes from the silicon substrate

Fig. 1.5 Schematic 3D view of FinFET [19]

and is enclosed by two or more gate electrodes as shown in Fig. 1.5 [19]. The fin serves as the conducting channel, while the gates regulate the passage of current through it. The verticality of the channel is an essential feature of FinFET, which helps decrease short-channel effects and increases control over the transistor's behavior [20]. FinFET offers several advantages over planar MOSFET such as improved scalability reducing performance degradation and enabling continued transistor scaling, lower leakage current, and compatibility with existing fabrication processes, making it easier to adopt in semiconductor manufacturing [21].

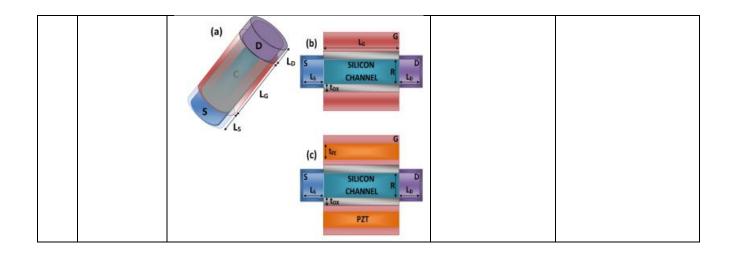

#### 1.3.2 Junctionless Transistor

All the MOSFETs have a p-n junction, having depletion layers that allow or block the current according to the voltage applied to the gate. Junctionless transistor (JLT) has no p-n junction as compared to the inversion mode device. The idea of the JLT has been reported by Colinge et.al in 2010 [22]. The challenging part of these inversion mode devices at nanoscale is the formation of ultra-sharp source/drain junctions due to which fabrication complexity increases and it requires precise control of doping and thermal conditions to form heterogeneous doping, like p-n junctions [23], [24]. The formation of source/drain junctions not only elevates the fabrication problem but also, consequently violates the electrical characteristics of the device. JLT presents an

Fig. 1.6 Junctionless Transistor (a) 3-D view (b) 2-D cross sectional view [25]

optimal resolution for addressing the challenge of achieving the extremely sharp formation of the source/drain junction. The basic structure of the JLT is shown in Fig. 1.6 which has a uniform and homogeneous doping throughout the source-channel-drain (N+-N+-N+) region [25]. JLT is basically a fully depleted device and the gate metal work function should be high as compared to conventional transistors. Due to the full depletion of charge carriers, it provides better subthreshold characteristics. It also has better SCE immunity as compared to conventional MOSFETs. The JLT, being free from abrupt changes in doping, holds great promise as a potential solution to address the challenges associated with costly annealing techniques and thermal budget constraints. Additionally, its fabrication is straightforward, and it offers opportunities for enhancing the electrical properties of the device [26]. There are some disadvantages of JLT such as low ON current and low transconductance, which have been improved by another alternative structure of junctionless structure known as Junctionless Accumulation Mode (JAM) structure.

#### 1.3.3 Junctionless Accumulation Mode FET

JLT has a number of advantages which have been discussed in our previous section but it has some disadvantages as well. The major disadvantages of the JLT are low drain current and low transconductance due to Carrier Mobility Degradation (CMD). The

Fig. 1.7 Schematic structure of Junctionless Accumulation Mode FET [28]

CMD occurs due to high channel doping concentration. The limitations of JLT can be addressed with the alternate structure known as Junctionless Accumulation Mode (JAM) transistor [27]. It is a homogeneously doped structure with N+-N-N+/N++-N+-N++ homo-junctions where the concentration in the channel region is moderately low in comparison to the source/drain region as shown in Fig. 1.7 [28]. In JAM FET, where the channel region has lower doping, the flow of current is not constrained primarily to the central region of the silicon channel. This results in a variation in current from the center towards the surface. Additionally, in the case of higher doping levels, a higher value of gate metal work function is needed to completely deplete the channel for its transition into the off state [29]. Moreover, the JAM FET employs a lower channel doping, forming a homogeneous N+-N-N+/N++-N++ junction, which facilitates a volume accumulation effect. JAM structure can also overcome the problem of CMD.

#### 1.3.4 Steep Subthreshold Slope Devices

Steep subthreshold devices, also known as steep slope transistors, are electronic devices that allow for efficient operation at very low power supply voltages. They have sparked considerable interest in recent years because of their prospective uses in low-power integrated circuits and energy-efficient devices. Conventional devices feature significant leakage currents and decreased performance in subthreshold operation, where the transistor operates below its threshold voltage, rendering them inefficient for low-power applications. Steep subthreshold devices seek to overcome these constraints by achieving a steeper subthreshold slope. The subthreshold slope measures how well a transistor switches between on and off states at low voltages. The subthreshold slope in conventional transistors is restricted by thermal energy and the Boltzmann distribution of carriers. Steep subthreshold devices have the potential to significantly reduce power consumption in a variety of applications, including low-power

electronics, Internet of Things (IoT) devices, wearable electronics, and energy-efficient computer systems. They can improve battery life, minimize energy consumption, and facilitate the adoption of energy-autonomous devices by running efficiently at low power supply voltages. Researchers have investigated and developed some of the steep subthreshold slope devices. A few of them are explained below:

#### 1.3.4.1 Tunnel FET (TFET)

A Tunnel Field-Effect Transistor (TFET) uses quantum mechanical

Fig. 1.8 Basic structure of Tunnel FET [30]

tunneling rather than typical thermionic emission to operate. TFETs are intended to alleviate the shortcomings of traditional MOSFETs, particularly with respect to power consumption and subthreshold slope. The channel region of a TFET is separated from the source and drain regions by a thin barrier known as the tunneling junction. Tunneling junctions are often made of high bandgap materials, such as strongly doped p-n junctions or heterojunctions as shown in Fig. 1.8 [30]. Due to the presence of a thin barrier, carriers (electrons or holes) can tunnel through the tunneling junction when a voltage is applied across the source and drain terminals [31]. This allows the TFET to toggle between on and off states. The main advantage of TFETs is their capacity to create a steep subthreshold slope.

TFETs can reach subthreshold slopes that are lower than this thermal limit, generally in the 10-100 mV/decade range or even below [32]. This enables transistor operation at lower power supply voltages to be more efficient. However, TFETs suffer limitations as well. The achievement of high onstate currents or drive currents is a considerable challenge, as quantum tunneling often results in lower current levels [33].

#### 1.3.4.2 Impact Ionization MOS (IMOS)

IMOS is proposed as a method of switching from off to on by modulating the avalanche breakdown voltage of a gated structure [34]. Fig. 1.9 shows the basic structure of n-channel IMOS. A p-n junction diode is utilized in this type of transistor with voltages greater than the breakdown voltage [35]. The delay of an IMOS is proportional to the logarithm of the required gain, making it incredibly fast. This device can therefore achieve subthreshold swing values that are substantially lower than the (kT/q) ln10 limit of a normal MOSFET [36]. The fundamental issue with impact

Fig. 1.9 Basic structure of an N-channel IMOS [35]

ionization MOSFETs is their long-term reliability. The existence of heated carriers in large densities is required for an avalanche breakdown, which affects reliability [37].

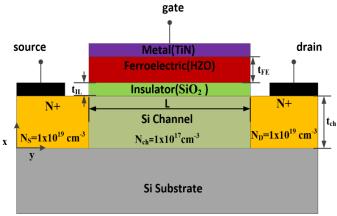

#### 1.3.4.3 Ferroelectric based Negative Capacitance FET

The Negative Capacitance Field-Effect Transistor (NCFET) is a particular type of field-effect transistor that uses the unique features of ferroelectric materials to produce a negative capacitance effect [38]. The NCFET concept originated as a possible solution to the power dissipation issues that traditional transistors confront. The schematic structure of a ferroelectric negative capacitance FET is shown in Fig. 1.10. The basic idea behind

Fig. 1.10 Schematic structure of a Ferroelectric Negative Capacitance FET [39]

NCFET is that by using a ferroelectric material as the gate dielectric, the effective capacitance of the transistor can be decreased below the physical capacitance. This negative capacitance effect occurs due to the intrinsic characteristics of the ferroelectric material, where the polarization response opposes the external electric field. When a positive voltage is provided to the gate of an NCFET, the ferroelectric material undergoes polarisation reversal, resulting in an internal negative voltage. This negative voltage effectively magnifies the voltage across the transistor, causing the charge density in the channel region to shift more dramatically. As a result, the NCFET has a subthreshold slope of less than 60 mV/decade, surpassing the

limit of typical MOSFET (about 60 mV/decade) [40]. NCFETs can function at lower supply voltages while preserving the needed functionality by amplifying the voltage shift at the gate. This offers the possibility of reduced power consumption in integrated circuits and potential energy savings.

#### 1.4 Motivation

The electronics industry has been driven to develop more features while also offering dense and quick integration over the past five decades as a result of CMOS technology scaling. The pursuit of enhanced performance and integration has been the driving force behind the scaling trends observed across various systems. As a result, present-day transistors exhibit speeds that are 20 times faster than their counterparts from half a century ago while occupying less than 1% of the space. However, these advancements have come at the cost of increased power consumption and power density, as highlighted in reference [14]. Furthermore, numerous parameters in VLSI design, such as supply voltage, gate dielectric constant, and leakage current, have undergone extensive customization to achieve the desired performance of integrated circuits (ICs). As per Moore's law, the reduction in oxide thickness and channel length poses a challenge to further scaling. To facilitate the dense integration of transistors, there is a need to linearly decrease the voltage supply and transistor size [41]. Dennard scaling laws state that reducing the size of a device lowers capacitance values and overall power usage. The limitation on the rate of increase in drain current with respect to the gate-source voltage to 60 mV/decade is attributed to the influence of Boltzmann statistics on the carriers in the source and drain regions of the MOSFET. As a result, this restriction prevents a further decrease in V<sub>DD</sub> (supply voltage) and hinders the reduction of overall power consumption [42]. To cope up with these challenges, various steeper subthreshold devices such as Tunnel FET, IMOS, and NCFET have been discussed in the previous section. However, the practical implementation of Tunnel FET and IMOS devices is constrained by a challenging fabrication procedure and poor reliability. Therefore, among these devices, NCFET has attracted the greatest interest due to its ability to achieve a steep subthreshold slope (SS) through a voltage amplification mechanism, all while maintaining a high drive current. Furthermore, NCFET offers additional advantages such as a high on-state current, minimal off-state current, and low power dissipation. Its straightforward construction, compatibility with existing fabrication processes, and exceptional performance characteristics, including a steep subthreshold swing (SS), a high on/off ratio, and adjustable hysteresis, further contribute to its appeal.

#### 1.5 Thesis Outline

#### • Chapter 1: Introduction

This chapter describes the evolution of MOSFET, the need for scaling the MOSFET, and various scaling challenges. Various device architectures have been explained to mitigate these challenges. This chapter also focuses on various steep subthreshold devices to overcome power challenge issues. Further, the main motivation behind this research work has been comprehended. Lastly, an overall organization of the thesis has been presented.

#### • Chapter 2: Literature Review

This chapter includes a thorough description of ferroelectric material based Negative Capacitance (NC) FET. Various ferroelectric materials exhibiting a negative capacitance effect have been presented. Furthermore, this chapter covers a brief history of NCFET as well as the work done on this device so far. Lastly, the research gaps and objectives have been defined based on the provided literature review.

# Chapter 3: Single Gate Junctionless Accumulation Mode Ferroelectric FET: Design & Analysis

This chapter involves the design and analysis of Single Gate Junctionless Accumulation Mode Ferroelectric FET. The main focus of this study is to combine the ferroelectric-induced NC effect with JAM architecture to get enhanced performance and fabrication feasibility. Methods used to model and simulate the device are discussed in detail. Many performance parameters such as DC, analog, and small signal parameters have been investigated to analyze the performance of the proposed device. The impact of temperature variation has also been studied on various parameters.

# Chapter 4: Double Gate Junctionless Accumulation Mode Ferroelectric FET: Design, Analysis & Modeling

This chapter includes the development of a compact analytical model of the double gate junctionless accumulation mode ferroelectric FET. The analytical surface potential model and drain current model of the proposed structure have been developed by using Poisson's equation and Landau- Khalatnikov equation and Pao-Sah integral equation. Analytical results derived from the model in this way were validated with simulation results obtained using the ATLAS TCAD simulator, which shows good agreement. The impact of temperature variation has also been investigated through similar modeling on various parameters.

#### • Chapter 5: Dual Gate Ferroelectric FET: Biosensor Design & Sensitivity Analysis

This chapter explores the biosensors application of the proposed dual gate ferroelectric structures. Label-free detection and ultra-sensitive detection of biomolecules are accomplished by integrating dielectric modulation and charge density concentration. The cavity is created inside the insulator layer as an immobilization site for the biomolecules to improve the drive current as well as sensitivity for biomolecule detection.

## • Chapter 6: Conclusion and Future Work

In this chapter, conclusions are drawn regarding NCFET potential in upcoming technology.

The contributions of this work are described, along with suggestions for additional research based on this dissertation.

# Chapter 2

## Literature Review

#### 2.1 Overview

In the preceding chapter, overview of various steep subthreshold devices which can handle the power challenge difficulties was presented. Among these devices, the NCFET has garnered the interest of researchers due to its ability to create a steep SS via a voltage amplification process. This chapter presents a literature review on several concepts of ferroelectric negative capacitance that was investigated and referenced during the research work. Several ferroelectric materials with negative capacitance effects have been reported. Furthermore, this chapter provides a brief history of NCFET as well as current research on this device. Finally, based on the provided literature review, the research gaps and objectives have been determined.

### 2.2 The Concept of Ferroelectric Negative Capacitance

#### 2.2.1 Negative capacitance: Definition

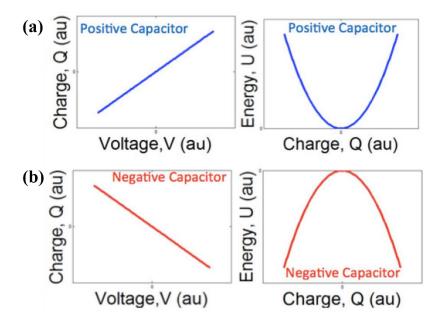

The definition of capacitance (C) for a device is the rate at which the charge (Q) increases with respect to the voltage (V) (C = dQ/dV). In the case of a negative capacitor, the charge decreases as the voltage increases as shown in Fig. 2.1 (a). Capacitance can also be described in terms of the free energy (U). The energy landscape of a negative capacitor follows an inverted parabola as depicted in Fig. 2.1 (b) [43].

For a linear capacitor, the free energy density (U) can be expressed in terms of capacitance as  $U=Q^2/2C$  or  $C=(d^2U/dQ^2)^{-1}$ . This capacitance and energy density relation also holds true for

a non-linear capacitor. To put it another way, the presence of a negative curvature zone in the energy landscape of an insulating material denotes the presence of a negative capacitance [44].

Fig. 2.1 Charge-voltage and energy landscapes of (a) Positive capacitor and (b) Negative capacitor [43]

# 2.2.2 Realization of Negative Capacitance through ferroelectric material

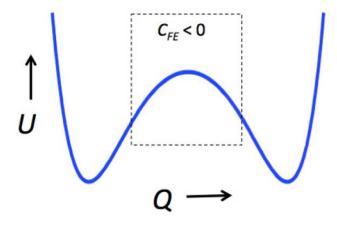

Figure 2.2 depicts the energy landscape of a ferroelectric material, displaying two degenerate energy minima [45]. This means that the ferroelectric material can have non-zero polarisation even when no electric field is provided. In general, the total charge density within a material can be stated as  $Q = \varepsilon E + P$ , where  $\varepsilon$  represents the ferroelectric's linear permittivity, E represents the external electric field, and P indicates polarization. Q is approximately equal to

Fig. 2.2 The energy double well diagram of a ferroelectric material. The area under the dashed region represents negative capacitance region [45]

P, in common ferroelectric materials because P is much bigger than E. As a result, we can use P and Q interchangeably [46]. When we compare the energy landscapes of a typical ferroelectric material as in Fig. 2.2 and a regular capacitor as in Fig. 2.1 (b), we see that the curvature around Q = 0 in a ferroelectric material is opposite to that of a regular capacitor. This opposing curvature raises the potential of a negative capacitance for the ferroelectric material close to Q = 0, keeping in mind that the energy of a regular capacitor is given by  $(Q^2/2C)$ . As a result, a ferroelectric material can exhibit negative capacitance around this point [47].

# 2.2.3 Landau Theory of Negative Capacitance

The free energy (U) of a ferroelectric can be expressed as an even-order polynomial of the polarization P [48] as follows:

$$U = \alpha P^2 + \beta P^4 + \gamma P^6 - EP \tag{2.1}$$

where, E=V/t, denotes the electric field applied, with V representing the voltage applied across the ferroelectric and t representing the ferroelectric thickness respectively. The  $\alpha$ ,  $\beta$ , and  $\gamma$  are the ferroelectric material parameters.  $\beta$  is negative for a first order phase transition and positive for a second order phase transition, whereas  $\gamma$  is always positive.  $\alpha = \alpha_0(T-T_C)$ , where  $\alpha_0$  is independent of temperature and always positive, T and  $T_C$  are temperature and Curie temperature, respectively [49]. Consequently, when the temperature is below the Curie temperature, the  $\alpha_0$  coefficient is negative, which leads to the negative curvature of the energy landscape of a ferroelectric around P=0. This negative curvature gives rise to the characteristic double-well energy landscape observed in ferroelectric materials [50].

Furthermore, at equilibrium, dU/dP=0, the following equation is obtained:

$$E = 2\alpha P + 4\beta P^3 + 6\gamma P^5 \tag{2.2}$$

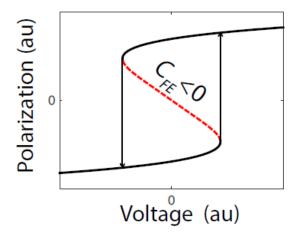

Fig. 2.3 Polarization characteristics of a ferroelectric material according to Landau theory [51]

Fig. 2.3 depicts the polarization-voltage characteristics of a ferroelectric capacitor as determined by equation 2.2 [51]. A ferroelectric capacitor exhibits non-linear charge-voltage properties, according to the Landau theory of ferroelectrics. There is a charge and voltage range, represented by the red dashed curve, where negative capacitance can be identified.

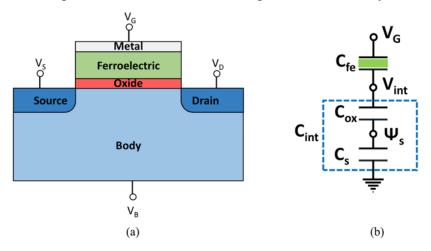

# 2.3 NCFET: Steep Switching

Field effect transistors are unable to efficiently control the heat generated, leading to the Boltzmann tyranny limit on the dimensional scalability of FETs. To circumvent this fundamental constraint and reduce power dissipation in electronic devices, negative capacitance employing ferroelectric materials has emerged as a promising solution. Fig. 2.4 (a) shows the schematic structure of NCFET which adds a ferroelectric layer in the gate stack of a conventional MOSFET [52]. The steep switching in Ferroelectric FET can be explained by using the following equation of SS obtained using the equivalent capacitance model in Fig. 2.4 (b) [53]:

$$SS = \frac{\partial V_g}{\partial log_{10}I_D} = \frac{\partial V_g}{\partial V_{int}} \frac{\partial V_{int}}{\partial \psi_S} \frac{\partial \psi_S}{\partial log_{10}I_D} = \frac{1}{A_v.m} \frac{\partial \psi_S}{\partial log_{10}I_D}$$

(2.3)

Here,  $V_{int}$  is the internal voltage and  $\psi_S$  is the surface potential. At room temperature, the final part in Equation 2.3 equates to a 60 mV/decade change. Since m is always less than one and  $A_v$

Fig. 2.4 (a) Ferroelectric material based negative capacitance FET (b) equivalent capacitance model [52]

is always one, the value of SS in a conventional transistor is always greater than one. In the case of an NCFET, however, the ferroelectric material can enter a negative capacitance state, resulting in a voltage amplification effect at the interface between the ferroelectric and oxide layers [53]. This leads the value of  $A_v$  to exceed one. This amplification factor offsets the effect of the m component in Equation 2.3, assisting in the suppression of the SS. If  $A_v$  is significantly bigger than m, SS can be reduced below the Boltzmann limit of 60 mV/decade.

Due to its elegance and simplicity, as well as the pressing demand for a new transistor, as Moore's law nears its limits, numerous researchers in industry and academia have been captivated by the concept of the device. They have conducted extensive investigations into the physics and technology of the NCFET, leading to a significant volume of scholarly articles published on the subject since 2008.

# 2.4 Literature Review

Ferroelectricity was initially discovered in 1920, but the concept of negative capacitance is relatively recent. Many researchers have attempted to minimize the Boltzmann limit by modifying the structure and materials employed. In 2008, Salahuddin et al. were the first to

report that SS could be reduced below the fundamental limit by utilizing a ferroelectric material as the gate insulator in a MOSFET. In the same year, Giovanni A. Salvatore et al. conducted the first experimental demonstration of an NCFET, achieving a minimum SS of 13 mV/decade using a 40 nm P(VDF-TrFE)/SiO<sub>2</sub> gate stack [54]. Since then, the NCFET has garnered considerable attention worldwide. In 2011, Khan and his research group explained the impact of negative capacitance in nanoscale ferroelectric dielectric heterostructures. They utilized a ferroelectric bilayer of Pb(Zr<sub>0.2</sub>Ti<sub>0.8</sub>)O<sub>3</sub> and a dielectric material SrTiO<sub>3</sub>. The device exhibited a minimum SS of 13 mV/decade, accompanied by an impressive on/off current ratio of approximately 10<sup>7</sup> [55].

Researchers have employed various ferroelectric materials in the demonstrations of NCFETs. This includes conventional perovskite materials like BaTiO<sub>3</sub> and PbZr<sub>x</sub>Ti<sub>1-x</sub>O<sub>3</sub>, as well as organic polymer ferroelectrics such as P(VDF<sub>x</sub>-TrFE<sub>1-x</sub>) [56]. Initially, there was a focus on ferroelectric materials like strontium bismuth tantalite (SBT) and lead zirconate titanate (PZT) due to their desirable dielectric, ferroelectric properties, low leakage current, and long polarization retention. However, these materials exhibited unstable ferroelectric behavior in thin film morphologies and were incompatible with standard IC processing technologies [57]. A significant breakthrough occurred with the discovery of doped HfO<sub>2</sub> ferroelectrics. The discovery of hafnium oxide (HfO<sub>2</sub>) based dielectrics presented a promising solution to overcome the limitations faced by previous ferroelectric materials. T. S. Boscke demonstrated ferroelectric properties in Si-doped HfO<sub>2</sub> materials in 2011 [58], and ferroelectric behavior was also discovered in Zr-doped HfO<sub>2</sub> in the same year [59]. Subsequent to that, research studies have demonstrated the ferroelectric properties of HfO<sub>2</sub> doped with Al [60], Y [61], Cd [62], La, and Sr [63]. Among these, HfO<sub>2</sub> materials doped with Zr have garnered significant attention due to their scalability to ultrathin films while maintaining desirable ferroelectric behavior.

In 2018, the discovery of ferroelectric materials based on Zr-doped HfO<sub>2</sub> brought about a breakthrough. These materials allowed for the scaling of the ferroelectric layer below 5 nm while still preserving a sufficiently strong polarization intensity [64]. This achievement was crucial in incorporating the negative capacitance effect in highly scaled transistor devices. In 2019, D. Kwon conducted a study where NCFET was fabricated using Zr-doped HfO<sub>2</sub> with a thickness of 1.8 nm. The results showed a steep SS of 20 mV/decade and a 10 times reduction in off current at a channel length of 30 nm, along with a significant improvement in on current compared to baseline transistors based on undoped HfO<sub>2</sub> [65]. In 2020, D. Kwon et. al. further demonstrated the persistence of spontaneous and switchable polarization in Zr-doped HfO<sub>2</sub> down to a thickness of one nm. This achievement was accomplished through the use of the atomic layer deposition method [66]. Ferroelectric materials based on Zr-doped HfO2 (HZO) offer several advantages over other known ferroelectric materials. They are compatible with modern semiconductor fabrication processes, thermally stable, exhibit higher dielectric permittivity, and possess a wide bandgap that helps suppress leakage current. Additionally, they can be scaled down to a thickness of 1 nm or less while maintaining a strong polarization intensity, making them highly attractive for advanced device applications.

Furthermore, one of the primary benefits of the negative capacitance (NC) effect is its ability to be integrated into a variety of transistor architectures by simply inserting a ferroelectric material layer in the gate stack. Numerous NCFET modifications have been investigated and shown as a result of this great compatibility with various transistor configurations. Planar NC-FETs, 2D NC-FETs [67], NC-JL-FETs [68], NC-JLNW-FETs [69], NC-FinFETs [70], NC-TFETs [71], NC-GAA-FETs [72], NC-GAA-TFETs [73], and NC-JLGAA-FETs [74] have all been proposed and experimentally proved. These transistor architectures demonstrated sub-60mV/decade SS and improved on-state current, demonstrating the effectiveness of the NC effect in improving device performance. A comparative summary of various NCFET structures

is reported in Table 2.1. In this table, various NCFET structures, ferroelectric materials, and their respective performance are presented.

**Table 2.1** Comparative summary of NCFET structures

| Ref. | Author &<br>Year                   | Ferroelectric NCFET Structures                                                                                                                                                                                     | Ferroelectric materials                                | Performance                                                                              |  |

|------|------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|------------------------------------------------------------------------------------------|--|

| [55] | A.I. Khan<br>et. al.<br>2011       | Planar  V <sub>G</sub> Ferro- electric Metal Hi-K Oxide  P Silicon N <sub>A</sub> =5E17cm <sup>-3</sup>                                                                                                            | Pb(Zr <sub>0.2</sub> Ti <sub>0.8</sub> )O <sub>3</sub> | • $SS_{min}$ = 13 mV/dec<br>• $I_{on}/I_{off}$ ratio = 10 <sup>7</sup>                   |  |

| [75] | Y.G. Xiao<br>et. al.<br>2012       | Planar  Top gate $V_0$ Metal  Ferroelectric $t_1$ Insulator $t_1$ Source  Insulator  Insulator  Ferroelectric  Metal  Bottom gate $V_0$                                                                            | Strontium Bismuth Tantalite (SBT)                      | • $SS_{min}$ = 28.9mV/dec<br>• $I_{on}/I_{off}$ ratio = $10^{12}$                        |  |

| [76] | Yeung et. al. 2013                 | UTB- NCFET (Ultra thin body)  V <sub>G</sub> Ferro- electric Metal High-K Oxide N+ High-K Buried Oxide N+ P+ Si                                                                                                    | Zr-doped HfO <sub>2</sub>                              | • $SS_{min}$ = 21 mV/dec<br>• $I_{on}/I_{off}$ ratio = 10 <sup>9</sup>                   |  |

| [77] | N.<br>Chowdhary<br>et. al.<br>2014 | NC TFET  Gate FE Metal High-k  Depletion region  P+  i n+  E  Gate  Ferroelectric Oxide  Name Depletion region  P+  i n+  A  Gate  Ferroelectric Oxide  Name Depletion Region  Region  P+  I n+  A  Retal FE  Gate | BaTiO <sub>3</sub>                                     | $ \bullet SS_{min} = 13.87 mV/dec $ $ \bullet I_{on}/I_{off}\ ratio = 10^{10} $          |  |

| [78] | J. Jo. et. al.<br>2015             | Planar                                                                                                                                                                                                             | P(VDF <sub>0.75</sub> -<br>TrFE <sub>0.25</sub> )      | $ \bullet SS_{min} = 18 \text{ mV/dec} $ $ \bullet I_{on}/I_{off} \text{ ratio} = 10^7 $ |  |

|      |                                | Au P(VDF-Trfe) TIN $V_{int}$ TiN $SiO_2$ N+  1 $\mu$ m NMOS N+                  |                                                          |                                                                                     |

|------|--------------------------------|---------------------------------------------------------------------------------|----------------------------------------------------------|-------------------------------------------------------------------------------------|

| [79] | S. Dasgupta<br>et. al.<br>2015 | Planar  Gate  Source  Drain  P2T  (100 nm)  n+  n+  p-substrate (5 × 1016 cm-3) | Pb(Zr <sub>0.52</sub> Ti <sub>0.48</sub> )O <sub>3</sub> | • $SS_{min}$ = 13 mV/dec<br>• $I_{on}/I_{off}$ ratio = $10^8$                       |

| [80] | K.S. Li. et.<br>al.<br>2015    | NC-FinFET  Gate  Mistrael gate  August  Sio  Si                                 | HfZrO <sub>2</sub>                                       | • $SS_{min}$ = 55 mV/dec<br>• $I_{on}/I_{off}$ ratio = $10^6$                       |

| [81] | C. Hu. et. al.<br>2015         | NC-FinFET Oxide  Metal Gate Ferroelectric High-k Fin  BOX                       | PZT                                                      | • $SS_{min}$ = 32 mV/dec<br>• $I_{on}/I_{off}$ ratio = $10^7$                       |

| [82] | M.H. Lee et.<br>al. 2016       | NC-FinFET  FE-HZO  DE                                                           | HfZrO <sub>x</sub>                                       | • $SS_{min}$ = 52 mV/dec<br>• $I_{on}/I_{off}$ ratio = $10^{10}$                    |

| [83] | C. Jiang et. al. 2016          | NC-DG-Junctionless FET    Metal gate                                            | SBT                                                      | $ \bullet \ SS_{min} = 10 \ mV/dec $ $ \bullet \ I_{on}/I_{off} \ ratio = 10^{11} $ |

|      | T                                  | V 2 2 2 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | T                         | T                                                                                                                     |

|------|------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|-----------------------------------------------------------------------------------------------------------------------|

| [84] | H. Mehta et.<br>al.<br>2016        | NC-DG-Junctionless FET  Top Gate  time  Channel  Drain  n+  time  Ferroelectric  Drain  n+  ph  Ferroelectric  Drain  ph  time  Ferroelectric  Drain  ph  time | Si doped HfO <sub>2</sub> | • SS= 10 mV/dec<br>• $I_{on}/I_{off}$ ratio = $10^{14}$                                                               |

| [85] | Eunah Ko.<br>et. al.<br>2017       | NC-FinFET  VD  GATE  GND (Vs)  S  Metal  Ferroelectric  Metal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | HfZrO <sub>2</sub>        | • $SS_{min}$ = 36 mV/dec<br>• $I_{on}/I_{off}$ ratio = $10^{10}$                                                      |

| [86] | F.A.<br>McGuire et.<br>al.<br>2017 | NC-MoS2 2D FET  (a)  No MoS2   | HfZrO <sub>2</sub>        | • $SS_{min}$ = 6.07 mV/dec<br>• $I_{on}/I_{off}$ ratio = $10^9$                                                       |