#### DESIGN AND CONTROL OF VIENNA RECTIFIER FED FULL BRIDGE LLC RESONANT CONVERTER BASED TWO STAGE OFF-BOARD EV CHARGER WITH CC-CV CHARGING ALGORITHM

#### DISSERTATION/THESIS

SUBMITTED IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE AWARD OF THE DEGREE OF

MASTER OF TECHNOLOGY

IN

POWER ELECTRONICS & SYSTEMS

Submitted by:

#### **KUSHANK SINGH**

#### 2K21/PES/08

Under the supervision of

DR. VANJARI VENKATA RAMANA (Assistant Professor, EED, DTU)

# DEPARTMENT OF ELECTRICAL ENGINEERING DELHI TECHNOLOGICAL UNIVERSITY

(Formerly Delhi College of Engineering) Bawana Road, Delhi-110042

MAY, 2023

DEPARTMENT OF ELECTRICAL ENGINEERING

DELHI TECHNOLOGICAL UNIVERSITY

(Formerly Delhi College of Engineering)

Bawana Road, Delhi-110042

**CANDIDATE'S DECLARATION**

I, KUSHANK SINGH, Roll No. 2K21/PES/08 student of M. Tech (Power Electronics &

Systems), hereby declare that the project Dissertation titled "Design and Control of Vienna

Rectifier fed Full Bridge LLC Resonant Converter based Two Stage off-Board EV

Charger with CC-CV Charging Algorithm" which is submitted by me to the Department

of Electrical Engineering Department, Delhi Technological University, Delhi in partial

fulfillment of the requirement for the award of the degree of Master of Technology, is original

and not copied from any source without proper citation. This work has not previously

submitted for the award of any Degree, Diploma.

Place: Delhi

Date: 31/05/2023

(Kushank Singh)

ii

DEPARTMENT OF ELECTRICAL ENGINEERING

DELHI TECHNOLOGICAL UNIVERSITY

(Formerly Delhi College of Engineering)

Bawana Road, Delhi-110042

CERTIFICATE

I hereby certify that the project Dissertation titled "Design and Control of Vienna Rectifier

fed Full Bridge LLC Resonant Converter based Two Stage off-Board EV Charger with

CC-CV Charging Algorithm" which is submitted by Kushank Singh, Roll No.

2K21/PES/08, Department of Electrical Engineering, Delhi Technological University, Delhi

in partial fulfilment of the requirement for the award of the degree of Master of Technology,

is a record of the project work carried out by the student under my supervision. To the best

of my knowledge this work has not been submitted in part or full for any Degree or Diploma

to this University or elsewhere.

Place: Delhi DR. VANJARI VENKATA RAMANA

Date: 31.05.2023 (SUPERVISOR)

iii

DEPARTMENT OF ELECTRICAL ENGINEERING

DELHI TECHNOLOGICAL UNIVERSITY

(Formerly Delhi College of Engineering)

Bawana Road, Delhi-110042

ACKNOWLEDGEMENT

I would like to express my gratitude towards all the people who have contributed their

precious time and effort to help me without whom it would not have been possible for me to

understand and complete the project.

I would like to thank **Dr. Vanjari Venkata Ramana** (Assistant Professor, Department of

Electrical Engineering, DTU, Delhi) my Project guide, for supporting, motivating and

encouraging me throughout the period of this work was carried out. His readiness for

consultation at all times, his educative comments, his concern and assistance even with

practical things have been invaluable. I would also like to thank the Centre of Excellence for

Electric Vehicles and Related Technologies, Delhi Technological University for providing

necessary facilities for performing my research work.

Finally, I must express my very profound gratitude to my parents, seniors and to my friends

for providing me with unfailing support and continuous encouragement throughout the

research work.

Date: 31/05/2023

Kushank Singh

M. Tech (Power Electronics & Systems)

Roll No. 2K21/PES/08

iv

#### **ABSTRACT**

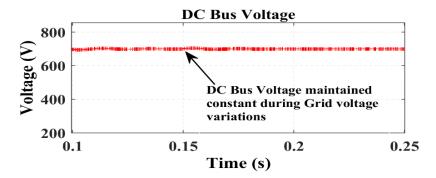

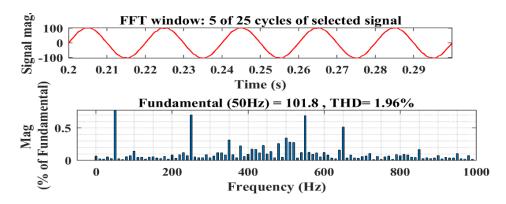

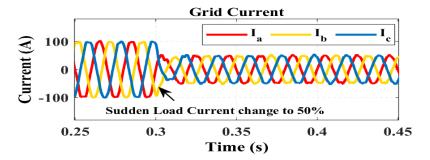

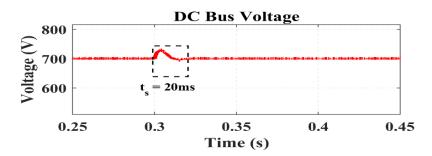

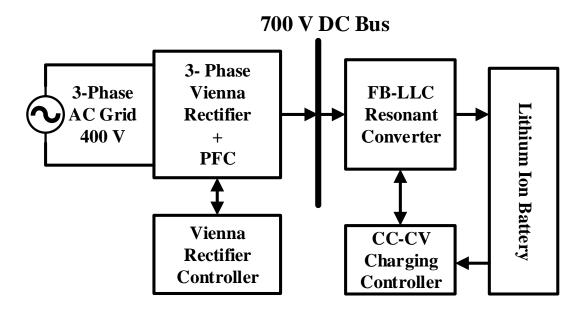

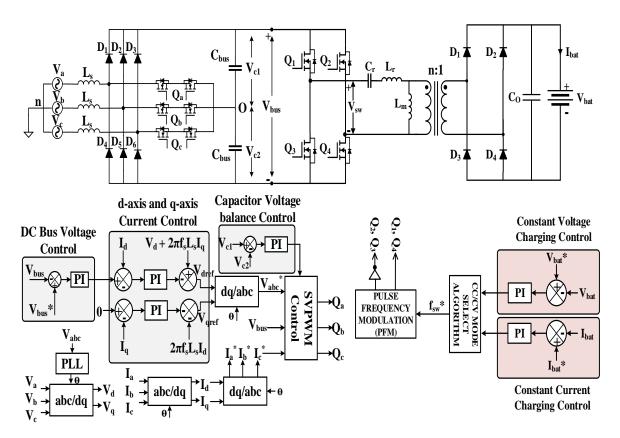

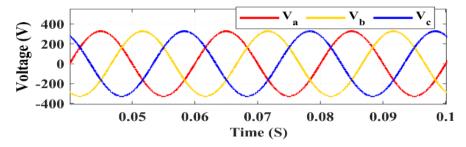

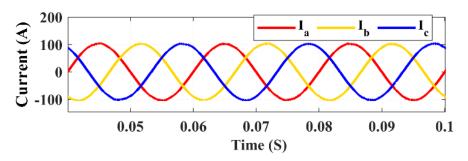

This work has three objectives, first objective is designing and controlling of Vienna rectifier. In this objective a complete analysis of three phase Vienna rectifier considering the effect of parasitic in the system for off-board EV charging application is discussed. To improve the dynamic response a modified dual loop control using d-axis and q-axis current controller including the effect of system parasitic in control loops is proposed. The proposed algorithm is compared with different control algorithms viz., dual loop control using hysteresis current controller and dual loop control using d-axis and q-axis current controller with SVPWM. A comparative performance analysis is discussed in terms of dynamic response during system disturbances like load variation, reference DC bus voltage variation and grid side variations. A 50 kW Vienna Rectifier operating at a switching frequency of 200 kHz is used for performance evaluation of all three control algorithms and is validated using MATLAB-Simulink. The second objective is the designing of full bridge LLC resonant converter as well as designing of magnetics for high frequency transformer. In this objective voltage control of LLC resonant converter is designed using pulse frequency modulation (PFM) for controlling the output voltage and analyze the effect of load side and input side variations on the converter. In this, the input is constant 700V DC rather than the Vienna rectifier output to analyze the performance of the converter and it is validated using MATLAB-Simulink. The third objective combines all the analysis involved in first and second objective. In this objective a 50 kW two stage off-Board EV charger is designed for charging a lithium ion battery using constant current (CC)-constant voltage (CV) algorithm. First stage includes three phase Vienna rectifier with power factor correction. The output of the first stage is the DC bus, which acts as an input to the second stage. Second stage includes full bridge LLC resonant converter and a lithium ion battery is connected to the output of second stage. To maintain constant DC bus voltage of 700V and to ensure unity power factor, dual loop control using d-axis and q-axis current control using space vector pulse width modulation (SVPWM) is adopted for controlling Vienna rectifier. Closed loop control for full bridge LLC resonant converter is designed using CC-CV control algorithm and pulse frequency modulation (PFM) to charge the rated 280 V/112 Ah lithium ion battery. The designed system outcomes are validated using MATLAB-Simulink.

## TABLE OF CONTENTS

| CANDIDATE DECLARATION                                                       | ii      |

|-----------------------------------------------------------------------------|---------|

| CERTIFICATE                                                                 | iii     |

| ACKNOWLEDGEMENT<br>ABSTRACT                                                 | iv      |

| TABLE OF CONTENTS                                                           | v<br>vi |

| LIST OF FIGURES                                                             | ix      |

| LIST OF TABLES                                                              | xii     |

| LIST OF ABBREVIATIONS                                                       | xiii    |

| LIST OF SYMBOLS                                                             | xiv     |

| CHAPTER 1: INTRODUCTION                                                     | 1       |

| 1.1 Introduction                                                            | 1       |

| 1.2 Background                                                              | 5       |

| 1.3 Thesis Motivation                                                       | 7       |

| 1.4 Thesis Objective                                                        | 7       |

| 1.5 Thesis Organization                                                     | 8       |

| CHAPTER 2: DESIGN AND ANALYSIS OF VIENNA RECTIFIER                          | 10      |

| 2.1 Introduction                                                            | 10      |

| 2.2 Modes of Operation                                                      | 11      |

| 2.3 Design of Vienna rectifier                                              | 16      |

| 2.4 Small Signal Modelling of Vienna rectifier                              | 17      |

| 2.5 Chapter Summary                                                         | 21      |

| CHAPTER 3: CONTROL OF VIENNA RECTIFIER                                      | 22      |

| 3.1 Introduction                                                            | 22      |

| 3.2 Dual Loop Control using Hysteresis Current Controller                   | 23      |

| 3.3 Dual Loop Control using d-axis and q-axis Current Controller with SVPWM | 24      |

| 3.3.1 SVPWM Control                                                         | 26      |

| 3.4 Proposed Modified Dual Loop Control using d-axis and q-axis Current Controller with SVPWM                                                | 30 |

|----------------------------------------------------------------------------------------------------------------------------------------------|----|

| 3.5 Results and Performance Evaluation                                                                                                       | 32 |

| 3.6 Chapter Summary                                                                                                                          | 39 |

| CHAPTER 4: DESIGN AND ANALYSIS OF FULL BRIDGE LLC RESONANT CONVERTER                                                                         | 41 |

| 4.1 Introduction                                                                                                                             | 41 |

| 4.2 Modes of Operation                                                                                                                       | 44 |

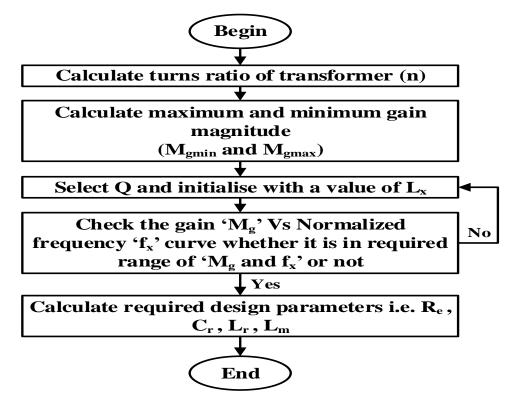

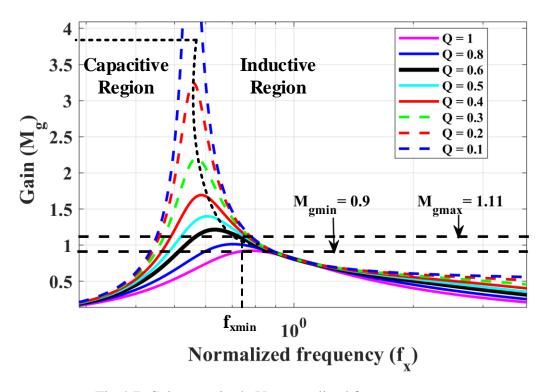

| 4.3 Design of Full Bridge LLC Resonant Converter                                                                                             | 46 |

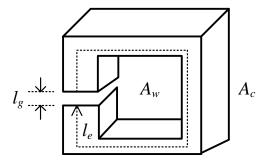

| 4.4 Magnetic Design of LLC Converter                                                                                                         | 50 |

| 4.5 Chapter Summary                                                                                                                          | 55 |

| CHAPTER 5: CONTROL OF FULL BRIDGE LLC RESONANT CONVERTER                                                                                     | 56 |

| 5.1 Introduction                                                                                                                             | 56 |

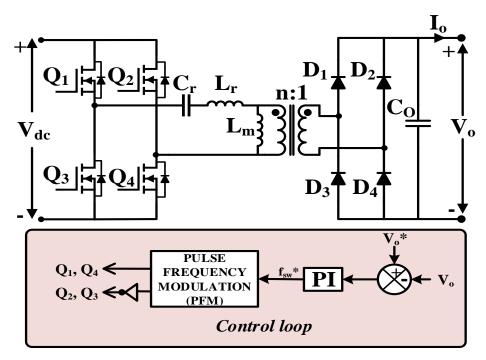

| 5.2 Voltage Control of LLC Resonant Converter                                                                                                | 56 |

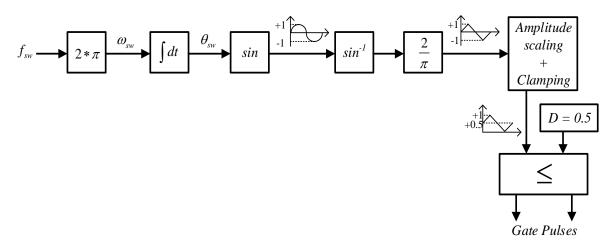

| 5.3 Pulse Frequency Modulation (PFM) Control                                                                                                 | 57 |

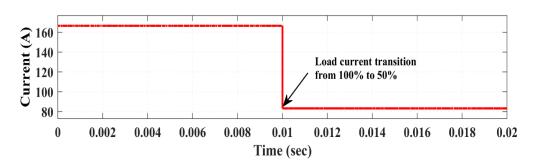

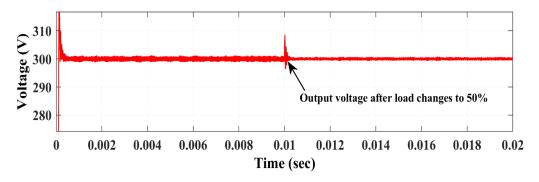

| 5.4 Results and Performance Evaluation                                                                                                       | 59 |

| 5.5 Chapter Summary                                                                                                                          | 63 |

| CHAPTER 6: TWO STAGE VIENNA RECTIFIER FED FULL BRIDGE<br>LLC RESONANT CONVERTER BASED OFF- BOARD EV CHARGER<br>WITH CC-CV CHARGING ALGORITHM | 64 |

| 6.1 Introduction                                                                                                                             | 64 |

| 6.2 Circuit Description of EV Charger                                                                                                        | 65 |

| 6.3 Control of EV Charger                                                                                                                    | 67 |

| 6.3.1 Vienna Rectifier Control                                                                                                               | 67 |

| 6.3.2 FBLLC Resonant Converter Control                                                                                                       | 68 |

| 6.4 Results                                                                                                                                  | 70 |

| 6.5 Chapter Summary                                                                                                                          | 74 |

| CHADTED 7. CONCLUSION AND EUTLIDE SCODE                                                                                                      | 75 |

| 7.1 Conclusion      | 75 |

|---------------------|----|

| 7.2 Future Scope    | 76 |

| REFERENCES          | 77 |

| LIST OF PUBLICATION | 83 |

# **LIST OF FIGURES**

| Fig.1.1.   | Port diagram of SAE J1772                                                                                                                                                                                                                                                     | 3  |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Fig.1.2.   | Circuit description of boost PFC                                                                                                                                                                                                                                              | 4  |

| Fig.1.3.   | Circuit description of interleaved boost PFC                                                                                                                                                                                                                                  | 4  |

| Fig.2.1.   | Three phase Vienna Rectifier circuit diagram                                                                                                                                                                                                                                  | 10 |

| Fig.2.2.   | Vienna rectifier operation at switching state 000                                                                                                                                                                                                                             | 12 |

| Fig.2.3.   | Vienna rectifier operation at switching state 001                                                                                                                                                                                                                             | 13 |

| Fig.2.4.   | Vienna rectifier operation at switching state 010                                                                                                                                                                                                                             | 13 |

| Fig.2.5.   | Vienna rectifier operation at switching state 011                                                                                                                                                                                                                             | 14 |

| Fig.2.6.   | Vienna rectifier operation at switching state 100                                                                                                                                                                                                                             | 14 |

| Fig.2.7.   | Vienna rectifier operation at switching state 101                                                                                                                                                                                                                             | 15 |

| Fig.2.8.   | Vienna rectifier operation at switching state 110                                                                                                                                                                                                                             | 15 |

| Fig.2.9.   | Vienna rectifier operation at switching state 111                                                                                                                                                                                                                             | 16 |

| Fig. 2.10. | Bode plot of $\Delta V_c(s)/d_0'(s)$                                                                                                                                                                                                                                          | 21 |

| Fig.3.1.   | Three phase Vienna Rectifier circuit diagram including parasitic                                                                                                                                                                                                              | 22 |

| Fig.3.2.   | Block diagram of dual loop control using hysteresis current control scheme                                                                                                                                                                                                    | 23 |

| Fig.3.3.   | Block diagram of dual loop control using d-axis and q-axis current control strategy with SVPWM                                                                                                                                                                                | 25 |

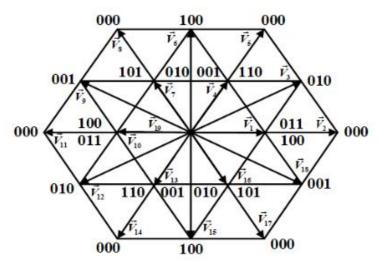

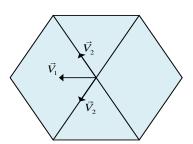

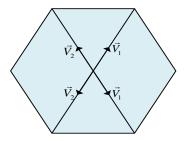

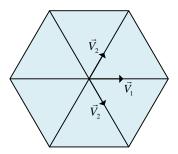

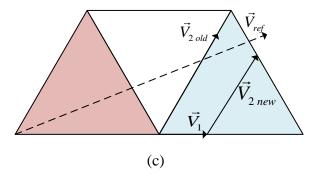

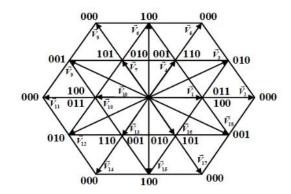

| Fig.3.4.   | Diagram of space vectors for Vienna Rectifier                                                                                                                                                                                                                                 | 26 |

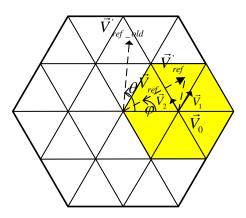

| Fig.3.5.   | Angle normalization                                                                                                                                                                                                                                                           | 27 |

| Fig.3.6.   | Dwell times for triangle 1                                                                                                                                                                                                                                                    | 28 |

| Fig.3.7.   | Dwell times for triangle 2                                                                                                                                                                                                                                                    | 28 |

| Fig.3.8.   | Dwell times for triangle 3                                                                                                                                                                                                                                                    | 29 |

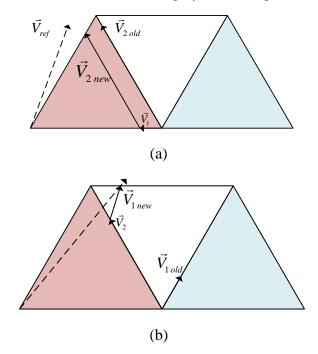

| Fig.3.9.   | Shortening of sub-vectors for (a) Triangle 1 (b) Triangle 2 (c) Triangle 3                                                                                                                                                                                                    | 29 |

| Fig.3.10.  | Block diagram of proposed modified dual loop control using d-axis and q-axis current control strategy                                                                                                                                                                         | 31 |

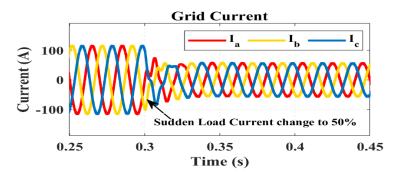

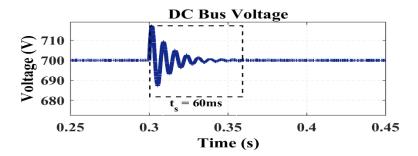

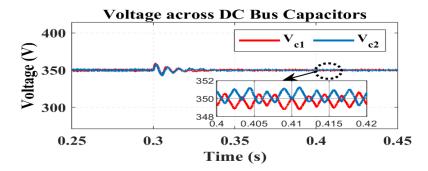

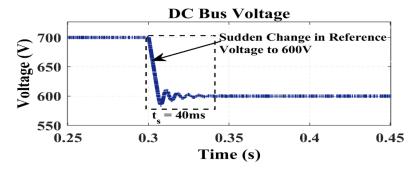

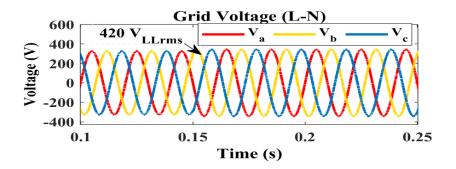

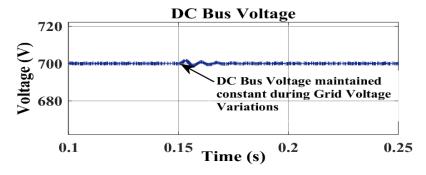

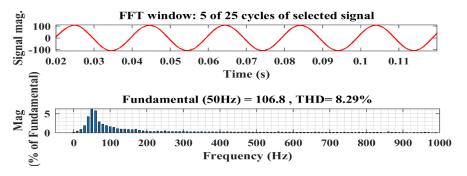

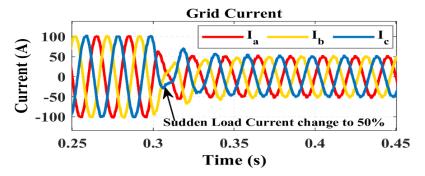

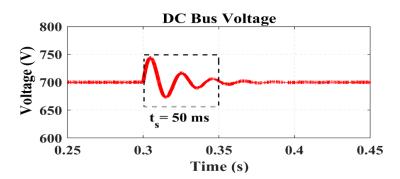

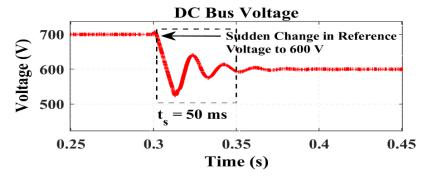

| Fig.3.11.  | Simulation results for dual loop control using hysteresis current control strategy (a) Grid current during load variations (b) DC bus voltage adaption to load variations (c) DC bus capacitor voltage (d) System adaption to reference DC voltage variation (e) Grid voltage | 34 |

|           | variation (f) System adaption to grid voltage variation (g) System non-adaption to grid frequency variation at 50.5 Hz                                                                                                                                                                                                                                                                                                                                                                                               |    |

|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Fig.3.12. | Simulation results for dual loop control using d-axis and q-axis current control strategy with SVPWM (a) Grid current during load variations (b) DC bus voltage adaption to load variations (c) DC bus capacitor voltage (d) System adaption to reference DC voltage variation (e) System adaption to grid voltage variation as in Fig 7(e) (f) System adaption to grid frequency variation at 50.5 Hz                                                                                                               | 36 |

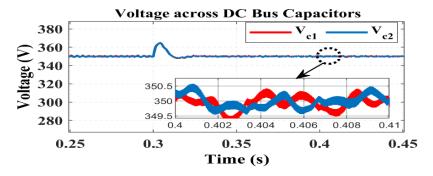

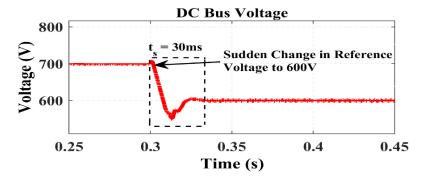

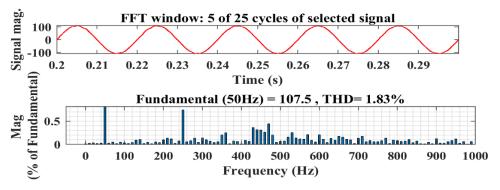

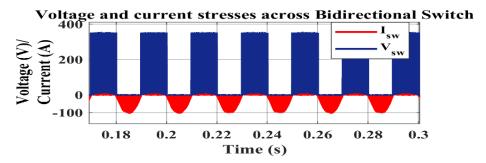

| Fig.3.13. | Simulation results of proposed modified dual loop control using daxis and q-axis current control strategy with SVPWM (a) Grid current during load variations (b) DC bus voltage adaption to load variations (c) DC bus capacitor voltage (d) system adaption to reference DC voltage variation (e) System adaption to grid frequency variation at 50.5 Hz (f) Voltage and current stresses across bidirectional switch                                                                                               | 38 |

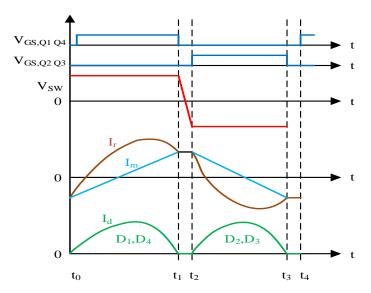

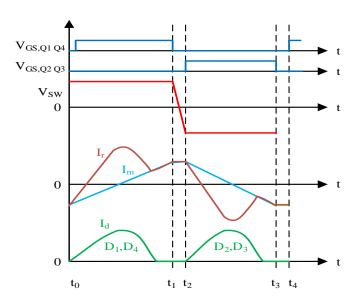

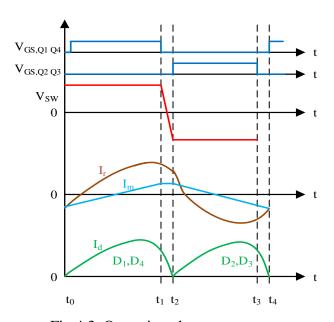

| Fig.4.1.  | Operation at resonance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 43 |

| Fig.4.2.  | Operation below resonance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 43 |

| Fig.4.3.  | Operation above resonance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 44 |

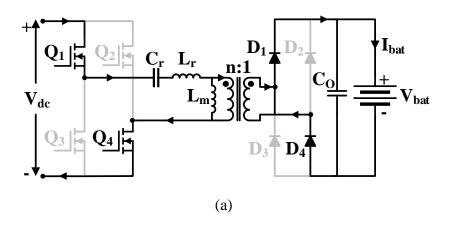

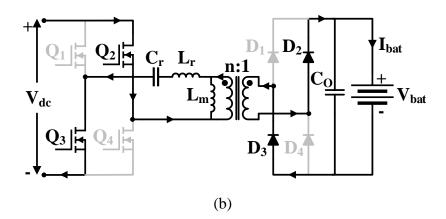

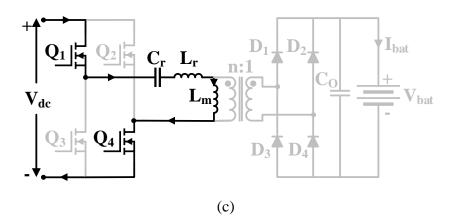

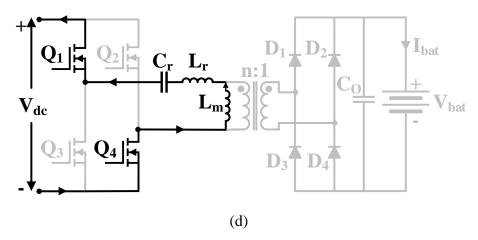

| Fig.4.4.  | FBLLC modes of operation for (a), (b) Power delivery (c), (d) No power delivery                                                                                                                                                                                                                                                                                                                                                                                                                                      | 45 |

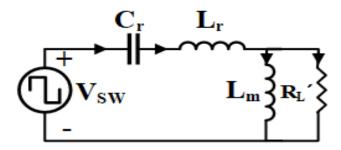

| Fig.4.5.  | LLC equivalent circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 46 |

| Fig.4.6.  | Designing Steps of LLC resonant circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 47 |

| Fig.4.7.  | Gain magnitude Vs normalized frequency curve                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 47 |

| Fig.4.8.  | Basic core specification                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 50 |

| Fig.5.1.  | Voltage control of LLC resonant converter                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 56 |

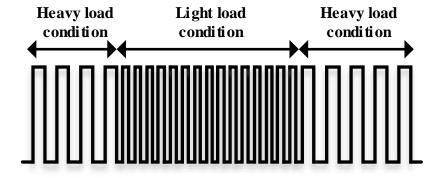

| Fig.5.2.  | Variation in switching frequency (fsw) or number of cycles based on loading condition to generate train of pulses                                                                                                                                                                                                                                                                                                                                                                                                    | 57 |

| Fig.5.3.  | PFM control block diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 58 |

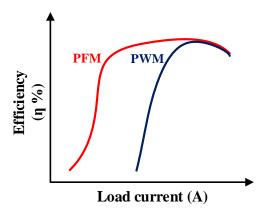

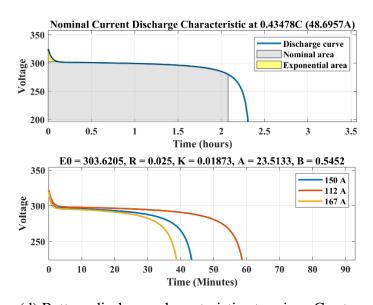

| Fig.5.4.  | Comparison of efficiency for different modulation techniques w.r.t. load                                                                                                                                                                                                                                                                                                                                                                                                                                             | 59 |

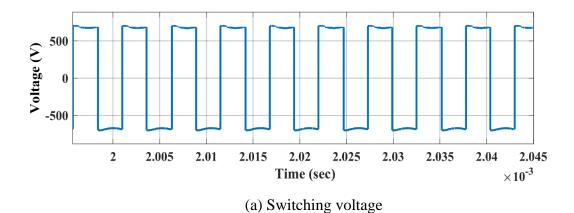

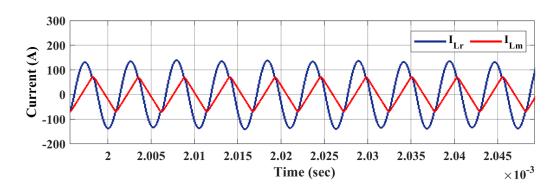

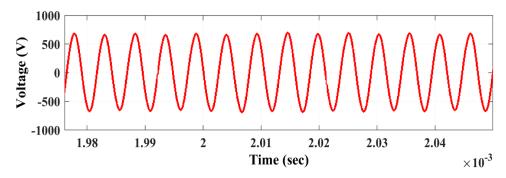

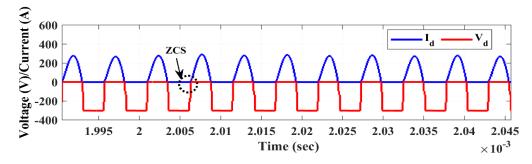

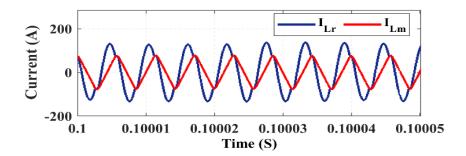

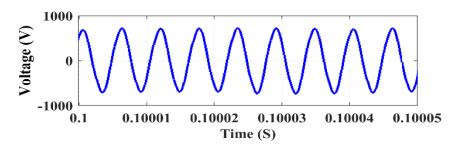

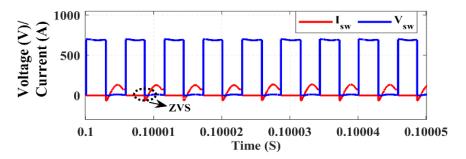

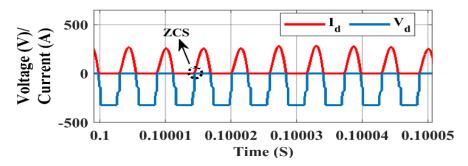

| Fig.5.5.  | Simulation results of FBLLC resonant converter (a) Switching voltage (b) Resonating and magnetizing inductor current (c) Voltage across resonating capacitor (d) Load current variation (e) Output voltage adaption due to load current variation (f) Output voltage tracking at various reference output voltage (g) Input voltage variations (h) Output voltage adaption at various input voltage variation (i) Voltage and current across primary side switch (j) Voltage and current across secondary side diode | 60 |

| Fig.6.1. | Block diagram of designed off-board EV charger                                                                                                                                                                                                                          | 64 |

|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Fig.6.2. | Circuit diagram and control diagram of designed off-board EV charger                                                                                                                                                                                                    | 65 |

| Fig.6.3. | Diagram of space vectors for Vienna rectifier                                                                                                                                                                                                                           | 68 |

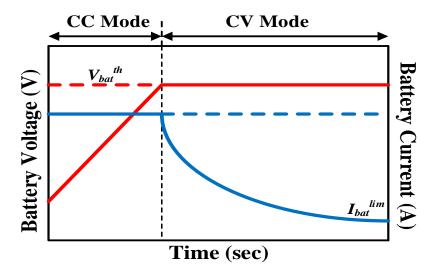

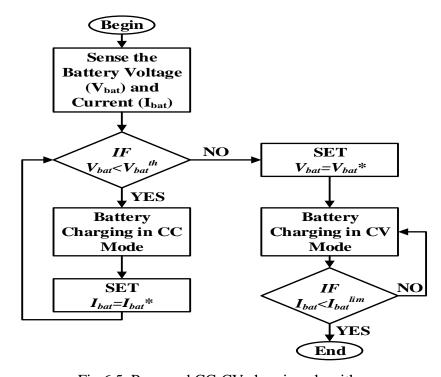

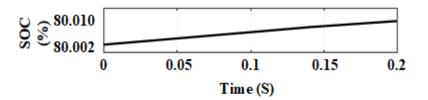

| Fig.6.4. | CC-CV charging curve                                                                                                                                                                                                                                                    | 69 |

| Fig.6.5. | Proposed CC-CV charging algorithm                                                                                                                                                                                                                                       | 69 |

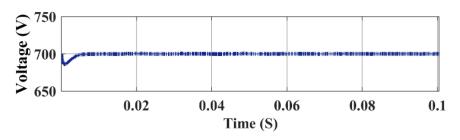

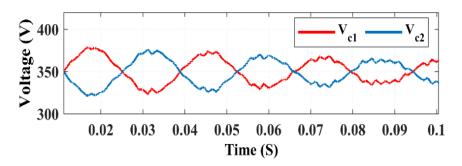

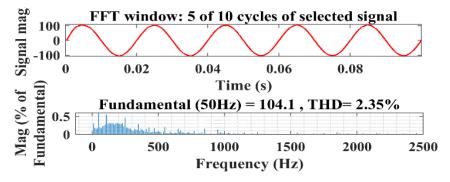

| Fig.6.6. | Simulation results of first stage Vienna rectifier (a) 3-phase grid voltage (b) 3-phase grid current (c) DC bus voltage (d) Bus capacitors voltage balance (e) FFT analysis of grid current                                                                             | 71 |

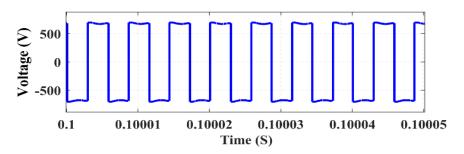

| Fig.6.7. | Simulation results of second stage FBLLC converter (a) Switching voltage (b) Resonating and magnetizing inductor current (c) Voltage across resonating capacitor (d) Voltage and current across primary side switch (e) Voltage and current across secondary side diode | 72 |

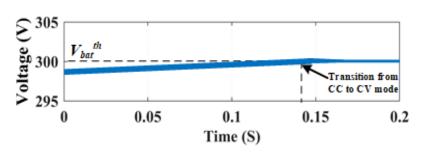

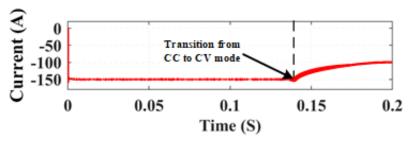

| Fig.6.8. | Simulation results of lithium ion battery (a) Battery voltage (b)<br>Battery current (c) Battery state of charge (SOC) (d) Battery<br>discharge characteristic at various C-rates                                                                                       | 73 |

# **LIST OF TABLES**

| Table 2.1. | Space vectors of Vienna rectifier                                                  | 11 |

|------------|------------------------------------------------------------------------------------|----|

| Table 2.2. | Sector classification based on grid current polarities                             | 12 |

| Table 2.3. | Voltage magnitude and capacitor mid-point current during each switching state      | 12 |

| Table 2.4. | Design specifications for Vienna rectifier                                         | 17 |

| Table 3.1. | Sector classification based on angle                                               | 27 |

| Table 3.2. | Conduction losses for all switching states of sector 1                             | 32 |

| Table 3.3. | Comparison of Different Control Algorithms due to Dynamic Variations in the System | 40 |

| Table 4.1. | Design Specifications for LLC Resonant Converter                                   | 50 |

| Table 4.2. | Design specifications for transformer design                                       | 52 |

| Table 4.3. | Wire specifications                                                                | 53 |

| Table 4.4. | Core specifications                                                                | 54 |

| Table 6.1. | Design specification for first stage Vienna rectifier                              | 66 |

| Table 6.2. | Design specifications for second stage FBLLC resonant converter                    | 66 |

## **LIST OF ABBREVIATIONS**

| EV      | Electric Vehicle                    |

|---------|-------------------------------------|

| p.f.    | Power Factor                        |

| THD     | Total Harmonic Distortion           |

| SAE     | Society of Automotive Engineers     |

| CHAdeMO | CHArge de MOve                      |

| BMS     | Battery Management System           |

| PHEV    | Plug In Hybrid Vehicle              |

| SoC     | State of Charge                     |

| C-Rate  | Charging/ Discharging Rate          |

| PFC     | Power Factor Correction             |

| DBR     | Diode Bridge Rectifier              |

| EMI     | Electro Magnetic Interference       |

| CICM    | Continuous Inductor Current Mode    |

| CC      | Constant Current                    |

| CV      | Constant Voltage                    |

| ZVS     | Zero Voltage Switching              |

| ZCS     | Zero Current Switching              |

| LLC     | Inductor Inductor Capacitor         |

| q-axis  | Quadrature- axis                    |

| d-axis  | Direct- axis                        |

| PFM     | Pulse Frequency Modulation          |

| SVPWM   | Space Vector Pulse Width Modulation |

| PI      | Proportional Integral               |

| ESR     | Equivalent Series Resistance        |

| FFT     | Fast Fourier Transform              |

| FHA     | First Harmonic Approximation        |

| AWG     | American Wire Gauge                 |

| MLT     | Mean length turn                    |

| MPL     | Magnetic path length                |

| Ah      | Ampere Hour                         |

## **LIST OF SYMBOLS**

| $Q_a, Q_b, Q_c$                           | Bidirectional switches in Vienna rectifier                  |

|-------------------------------------------|-------------------------------------------------------------|

|                                           | rms grid voltage, rms grid current                          |

| $V_{abc}$ , $I_{abc}$                     | Bus capacitors voltage                                      |

| $V_{c1}, V_{c2}$                          |                                                             |

| $\frac{I_N}{f_{sw}}$                      | Capacitor midpoint current                                  |

|                                           | switching frequency                                         |

| $\Delta i_{ppmax}$                        | maximum ripple in the current through filter inductor       |

| $f_s$                                     | grid frequency                                              |

| $C_o, r_c$                                | bus capacitor, ESR                                          |

| $L_s$ , $(r_s)$                           | input filter inductance, source resistance                  |

| $\Delta V_c$                              | mismatch between the bus capacitors voltage                 |

| $I_{abc}*$                                | reference grid current                                      |

| $V_{dc}*$                                 | reference bus voltage.                                      |

| $V_{qref}$ , $V_{dref}$                   | reference q-axis, d-axis voltage                            |

| $I_{qref}$ , $I_{dref}$                   | reference q-axis, d-axis current                            |

| I <sub>SWrms</sub> , V <sub>SWavg</sub>   | rms current, average voltage across bidirectional switch    |

| I <sub>Crms</sub>                         | rms current through bus capacitor                           |

| I <sub>Srms</sub>                         | input rms current                                           |

| $V_{Davg}$ , $I_{Drms}$                   | average diode voltage, rms diode current                    |

| $R_{DS(on)}, r_D$                         | on resistance of switch, diode                              |

| $t_{\scriptscriptstyle S}$                | settling time                                               |

| $Q_1, Q_2, Q_3, Q_4$                      | controlled switches on primary side                         |

| $f_o$                                     | resonating frequency                                        |

| $L_r$ , $C_r$                             | Resonating inductor, Resonating capacitor                   |

| $L_m$ , $L_x$                             | Magnetizing inductance, inductance ratio                    |

| Q                                         | Quality factor                                              |

| $K_{pv}$ and $K_{iv}$                     | PI controller gains for the voltage control loop of FBLLC   |

|                                           | converter                                                   |

| V <sub>bus</sub>                          | DC bus voltage                                              |

| $V_{bus}^{*}$                             | reference DC bus voltage                                    |

| Kp <sub>vbus</sub> and Ki <sub>vbus</sub> | PI controller gains for output bus voltage loop             |

| Kpvc and Kivc                             | PI controller gains for bus capacitors voltage balance loop |

| Kp <sub>iq</sub> and Ki <sub>iq</sub>     | PI controller gains for q-axis current loop                 |

| Kp <sub>id</sub> and Ki <sub>id</sub>     | PI controller gains for d-axis current loop                 |

| $V_{bat}$                                 | Battery voltage                                             |

| $V_{bat}*$                                | reference battery voltage                                   |

| f <sub>sw</sub> *                         | reference frequency                                         |

| $I_{bat}$                                 | Battery current                                             |

| $I_{bat}*$                                | reference battery current                                   |

| K <sub>pcv</sub> and K <sub>icv</sub>     | PI controller gains for CV charging                         |

| K <sub>pcc</sub> and K <sub>icc</sub>     | PI controller gains for CC charging                         |

| V <sub>bat</sub> <sup>th</sup>            | Battery threshold voltage                                   |

| I <sub>bat</sub> lim                      | Limiting current                                            |

|                                           |                                                             |

#### **CHAPTER 1**

#### INTRODUCTION

#### 1.1 INTRODUCTION

In today's growing world the fossils fuel are diminishing at an alarming rate, which leads to the researchers to find alternative fuel for vehicles [1]-[3]. That's why development in EV batteries is going on to achieve higher power density and also reduce the size of battery. An efficient Battery Management System (BMS) also required along with the battery which helps the battery to avoid certain threshold parameters, like prevents battery to achieve temperature rise beyond certain limits [4]. The growing future of EVs needs more reliable and efficient power electronics systems [5]. Advancements in power electronics converters involve a complex control algorithm. The EV charging system has a great involvement of the AC grid. A battery can be charged using a charging station but its impact on the AC grid has to be analyzed [6]. There are many power factor correction methods that have been adopted in literature which include advancement in PFC boost using wide band gap devices in which we can operate at high switching frequency which indirectly reduces the size of the system [7]. For off-board EV charging applications a three-phase power factor correction method needs to be implemented to improve the injected grid current. One of these topologies includes Vienna Rectifier with power factor correction.

The major concerns with the electric vehicle is the range of vehicle in a single charge and charging time required for battery. Fast charging is the only available option when the vehicle owner is in between the journey. There are both unidirectional and bidirectional EV chargers for charging the battery [8]. Both have some advantages and limitations, unidirectional chargers are easy to interconnect as compare to bidirectional charger as well have less tedious control, as controllable switches are also less. But bidirectional charger features supply of battery energy to the grid. The range anxiety in other way can be minimized by using plug in hybrid vehicle (PHEV) [9], [10], in which the vehicle can switched to the fuel system when battery is discharged and provides an upper hand for the vehicle owner.

In the growing market of EVs globally, unavailability of fast charging stations at certain distance is the main reason for the range anxiety among the EV users [11]. Therefore, the main focus of various charging companies is towards the charging of electric vehicles at higher charging rates under the EV standards [12]. Fast charging requires efficient power converters which are capable of transferring higher power to achieve high C-rate. Most of researchers working on the new topologies to make grid more stable during charging, as the THD in the injected grid current without any power factor correction (PFC) control is more than 5% which is not acceptable according to Indian EV standards [6].

There are various level of charging: level 1, level 2 and level 3 charging [5], [13]. Level 1 are mostly used in residential areas and have low ratings of up to 2 kW, which supports only slow charging and can take around 12 hours to charge to 100% SOC. Level 2 charging is adopted in residential as well as working premises, public places etc. which is capable of improving the C-rate of the battery and take around 6 hours to charge to 100% SOC. The ratings of level 2 charging goes up to 20 kW. Level 3 or DC fast charging are the most focus area nowadays due to their higher ratings ranging from 50 kW to several hundred kW. These charging station are provided among various areas of the cities and are expanding at a rising rate. Level 3 provides higher C-rates which helps the user to charge their vehicles up to 80% SOC in about 20 minutes and can take up to 1 hour depending on the rating of charging station. Level 1, level 2 chargers are characterized as on- board chargers and level 3 chargers as off board chargers.

The various levels of charging can be classified as:

#### a) Level 1 charging:

Level 1 charging is considered as slow charging which is mostly used by the user at residential area and have around 2 kW power rating. Level 1 charging can take up to 12 hours for full charge.

#### b) Level 2 charging:

Level 2 charging is considered as moderate charging which is mostly used by the user at private or public outlets and have up to 20 kW power rating. Level 2 charging can take up to 4-6 hours for full charge based on EV charger rating.

#### c) Level 3 charging:

Level 3 charging is considered as DC fast charging which is available at charging stations and have around 50 kW- 100's of kW power rating. Level 3 charging can take up to 30-40 minutes for charging up to 80% SoC based on EV charging station rating.

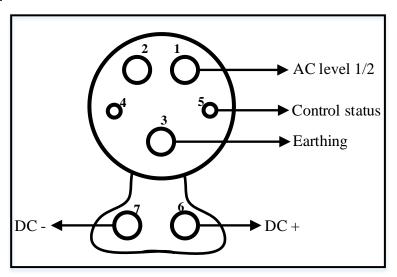

Level 1 and level 2 charging are classified as on-board charging and level 3 charging is considered as off-board charging. SAE J1772 connector can be used for level 1 and level 2 charging which consists of AC pins on top for ac charging and two DC connectors at bottom for dc charging as in Fig.1.1. For level 3 charging CHAdeMO connectors are widely considered [14].

Fig.1.1. Port diagram of SAE J1772

But the main concern regarding EV charging is the availability of fast charging stations at certain distance which requires more efficient and high power density power converters. High power density can provides charging of EV battery at higher C-rate which also reduces the range anxiety among the EV users. Another concern is the grid side disturbances when charging the electric vehicles. As, AC/DC converters are used to convert AC to DC due to which the grid side current becomes distorted and THD becomes quite high which is not recommended according to EV standards in India. Various power factor correction (PFC) methods are employed when designing an EV charger to make grid current in phase with the grid voltage [15]-[18].

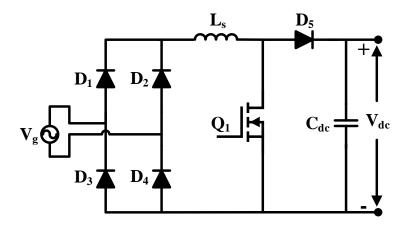

There are various power factor correction topologies which are adopted for improving the Total Harmonic Distortion (THD) of the grid current injected to the grid and one of them is boost PFC [19],[20]. The circuit description includes the AC grid at the input, followed by the Diode Bridge Rectifier (DBR) which provides a pulsating DC at the output. This pulsating DC acts as an input to the DC-DC boost converter which consists of inductor at the input which features to make input current continuous. In boost converter the controlling switch is the low side switch which ease its hardware designing as low side is connected to the ground. At the output, a capacitor is connected to maintain a certain level of DC bus voltage. A load is connected across the bus capacitor as in Fig.1.2.

Fig.1.2. Circuit description of boost PFC

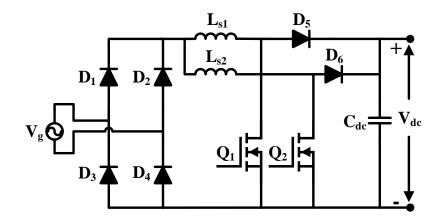

Interleaving of input inductors provide the features of reduced inductor and also minimizes the inductor current ripple [21], [22] as in Fig.1.3.

Fig.1.3. Circuit description of interleaved boost PFC

#### 1.2 BACKGROUND

There are on-board chargers as well as off-board charger for charging the EV battery. On-board charger includes single phase power factor correction (PFC) to mitigate the effect on the grid side by reducing the THD below 5% as per Indian EV standards. In [23], the authors have discussed the various PFC topologies for on-board charger. The various PFC topologies also reduces EMI, reduces higher order harmonics. The interleaved boost PFC significantly reduces the EMI due to interleaving which provides the 180° phase shifting between the interleaved inductor currents. It also features operation in continuous inductor conduction mode (CICM). In this topology the device count is high with medium costing but it offers efficiency between 91%-97% [24], [25]. In bridge-less boost the EMI is high as input voltage is always floating w.r.t. output voltage. It also operates in the CICM and this topology offers reduced less number of devices as compare to previous one, due to which the cost is less and it offers efficiency between 94%-96% [26]. In bridge-less interleaved boost the EMI gets reduced due to interleaving. It also operates in the CICM and requires more number of devices due to which the costing is increased. It offers the efficiency between 94%-99% [24], [27]. In semi-bridgeless boost the EMI is medium as input and output voltage have same ground. It also works in CICM with moderate number of devices due to which the cost is moderate and offers efficiency between 96%-99% [28]. In phase shifted semi-bridgeless boost the EMI is medium and it also works in CICM. The number of devices in operation is moderate due to which costing is moderate but it offers efficiency between 93%-99% [24]. In bridgeless dual boost the EMI is high but the number of devices used is very less due to which the cost is very less compared to other topologies and also works in CICM [29]. In totem-pole bridgeless boost the EMI is high as it works in discontinuous inductor conduction mode but number of devices used is less due to which cost is less and it offers efficiency between 96%-98% [30].

Various power factor corrections topologies are considered to make the grid current in phase with the voltage to minimize the THD below 5% based on the EV standards [31]. These topologies include interleaved boost PFC which is the simplified topology for power factor correction and features minimized inductor current ripples. In [32] the authors proposed a bridge less boost PFC topology for an EV charger which features no diode bridge

rectifier and improved efficiency. A comparison was also made among PFC boost, interleaved boost, semi-bridge less boost and totem pole boost on the basis of the system complexity and efficiency.

For off-board EV chargers three phase power factor correction is required at the front end to minimize the disturbances in the grid. In [33], the authors proposed three phase interleaved buck-boost with power factor correction is proposed. In this topology the working is in discontinuous current conduction mode. It provides high power density and efficient power conversion with reduced THD of 2.52 % and near to unity power factor. Other three phase power factor correction is implementing Vienna rectifier with power factor correction. Vienna rectifier is a 3-level converter which provides the operation of AC/DC conversion and with proper control algorithms design, power factor can be achieved near to unity and THD less than 5%. This will mitigate the effects of grid current in the system. Vienna rectifier provides high power density and efficient power conversion that's why it can be utilized in higher ratings off-board charger.

In [34] balancing of the output capacitor voltages in Vienna Rectifier using modified Discontinuous PWM to reduce the error between the bus capacitor voltages and to operate at high frequency is proposed. The authors in [35] proposed a hysteresis current control which reduces the computation complexity and is easy to implement. To reduce the THD of grid current a lot of research involves Space Vector PWM control [36]-[37]. In [38], the authors also included the system parasitic in Vienna Rectifier but the effect of parasitic is not included in the controlling loops.

For off-board EV charging, non- isolated dc-dc converters are not significant due to their limitations in power ratings and size. The full bridge LLC converter features higher power density, can be operated at higher switching frequency and also features ZVS of the primary side controlled switches based on the design consideration of the converter which minimizes the losses to a greater extent. The size of the converter can also be reduced when we are operating at higher switching frequency. But the designing of LLC converter is a tedious task due to various design consideration but its features attracts it for EV charging applications [39], [40].

There are various types of batteries which includes lead acid (Pb/PbO<sub>2</sub>) battery, lithium ion polymer (LiPo), nickel metal hydride (NiMH) batteries. Lithium ion batteries are preferred over other batteries in electric vehicles (EVs) due to their lighter weight and decent life cycle. To maximize the life of the lithium ion batteries CC-CV charging algorithm is preferred over CC or CV charging as it is more likely to mimic the chemistry involved in the battery. CC charging for fast charging can lead to temperature rise when the threshold voltage is reached. In CC-CV charging the CV mode is activated when the battery is charged up to a threshold voltage. In [41] the authors compared various charging algorithm including CC-CV, multi- stage CC, fuzzy logic etc. and conclusion are made on the basis of charging time and temperature effect on the battery.

#### 1.3 THESIS MOTIVATION

In the current scenario of EV market, availability of off-board EV charger at certain distance is the major concern. This will reduce the range anxiety among the users and will rise the sales of EVs and make growth of EV market in India stable. That's why this research area was selected to work upon and to add some contribution in the power converters for off-board EV charging. In this work a complete two stage off-board is designed for EV charging using constant current (CC) - constant voltage (CV) algorithm. Vienna rectifier is designed for power conversion from AC to DC and three control algorithms is designed for controlling the DC bus as well improve the power factor by mitigating the grid side effects. All the three control algorithms is compared in terms of dynamic variations and grid side variations in the system. In second stage a full bridge LLC resonant converter is designed by ensuring zero voltage switching (ZVS) in the primary side controlled switches and zero current switching (ZCS) in the secondary side diodes. A lithium ion battery is charged using proposed CC-CV charging algorithm. The charging will be at higher C-rate which will reduce the charging time.

#### 1.4 THESIS OBJECTIVE

This work has three objectives, first objective is designing and controlling of Vienna rectifier. In this objective a complete analysis of three phase Vienna rectifier considering the effect of parasitic in the system for off-board EV charging application is discussed. To

improve the dynamic response a modified dual loop control using d-axis and q-axis current controller including the effect of system parasitic in control loops is proposed.

The second objective is the designing of full bridge LLC resonant converter as well as designing of magnetics for high frequency transformer. In this objective voltage control of LLC resonant converter is designed using pulse frequency modulation (PFM) for controlling the output voltage and analyze the effect of load side and input side variations on the converter. In this, the input is constant 700V DC rather than the Vienna rectifier output to analyze the performance of the converter.

The third objective combines all the analysis involved in first and second objective. In this objective a 50 kW two stage off-Board EV charger is designed for charging the rated 280 V/112 Ah lithium ion battery using constant current (CC)-constant voltage (CV) charging algorithm.

#### 1.5 THESIS ORGANIZATION

This thesis consists of complete design and control of the two stage off-board EV charger for charging a lithium ion battery using CC-CV charging algorithm. The outline of this thesis is as follows:

**Chapter 1:** This chapter gives brief introduction regarding EV charging issues, different levels of EV charging and different type of connectors. It also provides brief background of this research topic. This chapter also provides motivation and objective of this thesis and then thesis organization.

**Chapter 2:** This chapter consist of circuit analysis of Vienna rectifier which includes its modelling, design as well as different modes of operation.

**Chapter 3:** This chapter explains the three control algorithms i.e. dual loop control using hysteresis current controller, dual loop control using d-axis and q-axis current controller with SVPWM and proposed modified dual loop control using d-axis and q-axis current controller including the effect of system parasitic in control loops. A comparative performance analysis is discussed in terms of dynamic response during system disturbances like load variation, reference DC bus voltage variation and grid side variations.

**Chapter 4:** This chapter includes full bridge LLC resonant converter description and analysis. It also includes various modes of operations and complete design of LLC circuit as well as magnetic design is explained with proper calculations.

**Chapter 5:** This chapter explains the controlling of full bridge LLC resonant converter which includes pulse frequency modulation (PFM) control and its dynamic performance is evaluated.

**Chapter 6:** In this chapter, by considering all the analysis performed in previous chapters, a two stage off-board charger is discussed. CC-CV charging algorithm is also discussed for charging a rated lithium ion battery.

**Chapter 7:** In this chapter conclusion of this work is summarized and future work is discussed.

#### **CHAPTER 2**

#### DESIGN AND ANALYSIS OF VIENNA RECTIFIER

#### 2.1 INTRODUCTION

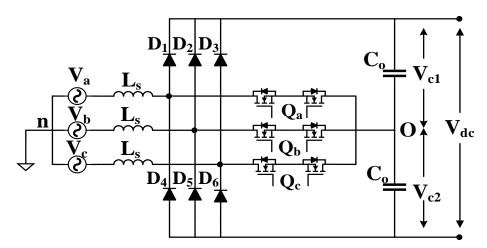

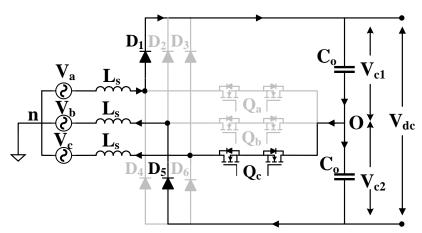

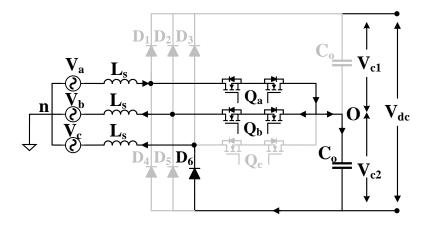

Vienna Rectifier is a three-level AC-DC converter that maintains a desired DC voltage at the output. It also features input power factor correction and eliminates harmonics which leads to a reduction in Total Harmonic Distortion (THD) [42]. The circuit includes three input filter inductances, one for each phase, which helps out in the reduction of input current ripples and also performs the function of boosting. The second stage includes the diode bridge rectifier containing six power diodes, two diodes for each phase. The additional elements in the Vienna Rectifier are the three bi-directional switches Qa, Qb and Qc in each phases due which it is called as multilevel converter. The last stage is the DC bus capacitors which helps to maintain the required DC bus voltage and also reduce the ripples in the output voltage. The circuit diagram of Vienna rectifier is shown in Fig.2.1.

Fig.2.1. Three phase Vienna Rectifier circuit diagram

The voltage applied between the phase and capacitor midpoint is decided by the current direction as well as the switching of the bi-directional switches. When all the bidirectional switches are ON then voltage is zero, when bidirectional switch is OFF and

either of D1, D2, D3 conducts then voltage is  $+V_{dc}/2$ . Voltage is  $-V_{dc}/2$  when either of D4, D5, D6 conducts. This can be generalized as,

$$V_{xo} = \frac{V_{dc}}{2} * sign(i_x) \{1 - Q_x\}$$

(2.1)

Where,  $sign(i_x)$  is decided by the current direction,  $Q_x$  is switching state of the bidirectional switch and x = a, b, c.

The voltage between neutral (n) and capacitor midpoint is,

$$V_{no} = \frac{V_{dc}}{6} (Q_a + Q_b + Q_c)$$

(2.2)

The voltage between rectifier input and neutral 'n' is,

$$V_{xn} = V_{xo} - V_{no} (2.3)$$

Space vectors for Vienna rectifier can be depicted as,

$$\vec{V}_{ref} = \frac{V_{dc}}{3} \left[ Q_a e^{j0} + Q_b e^{j\frac{2}{3}\pi} + Q_c e^{-j\frac{2}{3}\pi} \right]$$

(2.4)

Table 2.1. Space vectors of Vienna rectifier

| Vectors        | No. of vectors | Magnitude           |

|----------------|----------------|---------------------|

| Long vectors   | 6              | $\frac{2V_{dc}}{3}$ |

| Medium vectors | 6              | $V_{dc}/\sqrt{3}$   |

| Short vectors  | 6              | $V_{dc}/_3$         |

| Zero vector    | 1              | 0                   |

#### 2.2 MODES OF OPERATION

Vienna rectifier consists of three bi-directional switches which makes eight switching states possible for operation. Based on grid current direction there are six sectors possible, which makes 48 possible states but some of them are redundant states which leads to 25

modes of operation. But in this paper all possible modes of operation for sector 1 is stated in Table 2.2 and in Fig.2.2 to Fig.2.9.

Table 2.2. Sector classification based on grid current polarities

| Sector 1 | $i_a, i_b, i_c = +, -, -$ | Sector 4 | $i_a, i_b, i_c = -, +, +$ |

|----------|---------------------------|----------|---------------------------|

| Sector 2 | $i_a, i_b, i_c = +, +, -$ | Sector 5 | $i_a, i_b, i_c = -, -, +$ |

| Sector 3 | $i_a, i_b, i_c = -, +, -$ | Sector 6 | $i_a, i_b, i_c = +, -, +$ |

Table 2.3. Voltage magnitude and capacitor mid-point current during each switching state

| <b>Switching State</b> | Vao                | $V_{bo}$    | V <sub>co</sub> | $I_N$           |

|------------------------|--------------------|-------------|-----------------|-----------------|

| 000                    | V <sub>dc</sub> /2 | $-V_{dc}/2$ | $-V_{dc}/2$     | 0               |

| 001                    | V <sub>dc</sub> /2 | $-V_{dc}/2$ | 0               | ic              |

| 010                    | V <sub>dc</sub> /2 | 0           | $-V_{dc}/2$     | $i_b$           |

| 011                    | V <sub>dc</sub> /2 | 0           | 0               | -i <sub>a</sub> |

| 100                    | 0                  | $-V_{dc}/2$ | $-V_{dc}/2$     | ia              |

| 101                    | 0                  | $-V_{dc}/2$ | 0               | -i <sub>b</sub> |

| 110                    | 0                  | 0           | $-V_{dc}/2$     | -i <sub>c</sub> |

| 111                    | 0                  | 0           | 0               | 0               |

In Table 2.3  $V_{ao}$ ,  $V_{bo}$  and  $V_{co}$  are the voltage magnitude between phases and capacitor mid-point and  $I_N$  is capacitor mid-point current. All modes for a complete sector 1 is explained below,

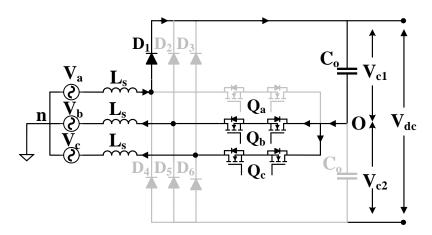

#### Mode I: Switches Qa, Qb, Qc are OFF

In this mode of operation, all three bi-directional switches  $Q_a$ ,  $Q_b$ ,  $Q_c$  are OFF due to which the capacitor mid-point current is zero and the different voltage levels are,

$$V_{ao} = V_{dc}/2, V_{bo} = -V_{dc}/2, V_{co} = -V_{dc}/2$$

$$\begin{array}{c} V_{a} & L_{s} \\ \hline V_{b} & L_{s} \\ \hline V_{c} & L_{s} \\ \hline \end{array}$$

$$\begin{array}{c} V_{a} & C_{o} \\ \hline V_{c1} \\ \hline \end{array}$$

Fig.2.2. Vienna rectifier operation at switching state 000

#### Mode II: Switches Qa, Qb are OFF and Qc is ON

In this mode of operation, two bi-directional switches  $Q_a$ ,  $Q_b$  are OFF and  $Q_c$  is ON due to which the capacitor mid-point current is equal to phase c current and the different voltage levels are,

$$V_{ao} = V_{dc}/2, V_{bo} = -V_{dc}/2, V_{co} = 0$$

Fig.2.3. Vienna rectifier operation at switching state 001

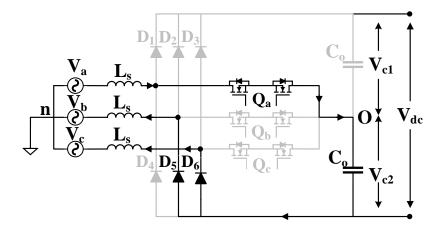

#### Mode III: Switches $Q_a,\,Q_c$ are OFF and $Q_b$ is ON

In this mode of operation, two bi-directional switches  $Q_a$ ,  $Q_c$  are OFF and  $Q_b$  is ON due to which the capacitor mid-point current is equal to phase b current and the different voltage levels are,

$V_{ao} = V_{dc}/2$ ,  $V_{bo} = 0$ ,  $V_{co} = -V_{dc}/2$

Fig.2.4. Vienna rectifier operation at switching state 010

#### Mode IV: Switches Qb, Qc are ON and Qa is OFF

In this mode of operation, two bi-directional switches  $Q_b$ ,  $Q_c$  are ON and  $Q_a$  is OFF due to which the capacitor mid-point current is equal to phase a current but in opposite direction and the different voltage levels are,

$$V_{ao} = V_{dc}/2, V_{bo} = 0, V_{co} = 0$$

Fig.2.5. Vienna rectifier operation at switching state 011

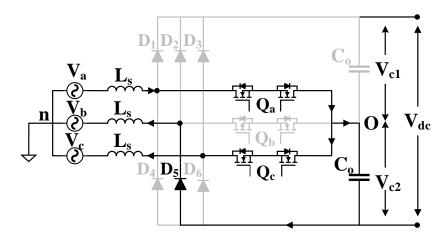

#### Mode V: Switches Qb, Qc are OFF and Qa is ON

In this mode of operation, two bi-directional switches  $Q_b$ ,  $Q_c$  are OFF and  $Q_a$  is ON due to which the capacitor mid-point current is equal to phase a current and the different voltage levels are,

$$V_{ao} = 0$$

,  $V_{bo} = -V_{dc}/2$ ,  $V_{co} = -V_{dc}/2$

Fig.2.6. Vienna rectifier operation at switching state 100

#### Mode VI: Switches Qa, Qc are ON and Qb is OFF

In this mode of operation, two bi-directional switches  $Q_a$ ,  $Q_c$  are ON and  $Q_b$  is OFF due to which the capacitor mid-point current is equal to phase b current but in opposite direction and the different voltage levels are,

$$V_{ao} = 0$$

,  $V_{bo} = -V_{dc}/2$ ,  $V_{co} = 0$

Fig.2.7. Vienna rectifier operation at switching state 101

#### Mode VII: Switches Qa, Qb are ON and Qc is OFF

In this mode of operation, two bi-directional switches  $Q_a$ ,  $Q_b$  are ON and  $Q_c$  is OFF due to which the capacitor mid-point current is equal to phase c current but in opposite direction and the different voltage levels are,

$$V_{ao} = 0$$

,  $V_{bo} = 0$ ,  $V_{co} = - V_{dc}/2$

Fig.2.8. Vienna rectifier operation at switching state 110

#### Mode VIII: Switches Qa, Qb and Qc are ON

In this mode of operation, two bi-directional switches  $Q_a$ ,  $Q_b$  and  $Q_c$  are ON due to which the capacitor mid-point current is zero and the different voltage levels are,

$$V_{ao} = 0$$

,  $V_{bo} = 0$ ,  $V_{co} = 0$

Fig.2.9. Vienna rectifier operation at switching state 111

#### 2.3 DESIGN OF VIENNA RECTIFIER

The system parameters for the Vienna Rectifier can be calculated using [43]. The input filter inductance can be calculated using (2.5),

$$L_s = \frac{\begin{pmatrix} V_{dc} / 2 \end{pmatrix}}{4 * f_{sw} * \Delta i_{pp_{max}}}$$

(2.5)

Where,  $V_{dc}$  is the output DC bus voltage of Vienna Rectifier,  $f_{sw}$  is the operating switching frequency of Vienna Rectifier and  $\Delta i_{ppmax}$  is the maximum ripple in the current through filter inductor. The filter inductance value is inversely proportional to the switching frequency. For the system analysis,  $f_{sw}$  =200 kHz is opted for off-board EV charging application due to which the size of the inductor gets reduced and the THD can be minimized using control loops.

The output capacitance value is calculated using (2.6),

$$C_o = \left(\frac{1}{3}\right) \frac{P_{ac}}{4 * f_s * \left(V_{dc}^2 - \left(V_{dc} - \Delta V_{dc}\right)^2\right)}$$

(2.6)

Where  $P_{ac}$  is the power ratings of the system,  $f_s$  is grid frequency,  $\Delta V_{dc}$  is the bus voltage ripple and  $V_{dc}$  is the DC bus voltage. The design specifications considered in this work are tabulated in Table 2.4.

| Parameters                                | Value                   |

|-------------------------------------------|-------------------------|

| L-L rms grid voltage ( $V_{abc}$ ), grid  | 400 V, 50 Hz            |

| frequency $(f_s)$                         | 400 V, 30 11Z           |

| Output DC bus voltage $(V_{dc})$          | 700V                    |

| Power rating $(P_{ac})$                   | 50 kW                   |

| Output current $(I_o)$                    | 71.4285 A               |

| Switching frequency $(f_{sw})$            | 200 kHz                 |

| Bus capacitor $(C_o)$ , ESR $(r_c)$       | $4300 \mu F$ , $3.8 mΩ$ |

| Input filter inductance ( $L_s$ ), source | 41 μΗ, 0.1 Ω            |

| resistance $(r_s)$                        |                         |

| Input current THD                         | < 2%                    |

Table 2.4. Design specifications for Vienna rectifier

#### 2.4 SMALL SIGNAL MODELLING OF VIENNA RECTIFIER

The small signal modelling of Vienna rectifier can be analyzed using [44] and by applying KVL,

$$V_{x} = L_{s} \frac{di_{x}}{dx} + \frac{V_{dc}}{2} \left[ sign(i_{x}) * (1 - d_{k}) \right] + V_{On}$$

$$(2.7)$$

Where,  $x = \{a, b, c\}$ ;  $k = \{1, 2, 3\}$  and,

$$sign(i_x) = \begin{cases} +1 & if \ i_x > 0 \\ -1 & if \ i_x < 0 \end{cases}$$

(2.8)

Where,  $V_x$  and  $i_x$  are the grid voltages and current respectively.

For balanced system,

$$V_a + V_b + V_c = 0 (2.9)$$

$$i_a + i_b + i_c = 0 (2.10)$$

$$V_{a} = L_{s} \frac{di_{a}}{dt} + \frac{V_{dc}}{3} \left[ 2 \operatorname{sign}(i_{a})(1 - d_{1}) - \operatorname{sign}(i_{b})(1 - d_{2}) - \operatorname{sign}(i_{c})(1 - d_{3}) \right]$$

(2.11)

$$V_{b} = L_{s} \frac{di_{b}}{dt} + \frac{V_{dc}}{3} \left[ -sign(i_{a})(1 - d_{1}) + 2sign(i_{b})(1 - d_{2}) - sign(i_{c})(1 - d_{3}) \right]$$

(2.12)

$$V_{c} = L_{s} \frac{di_{c}}{dt} + \frac{V_{dc}}{3} \left[ -sign(i_{a})(1 - d_{1}) - sign(i_{b})(1 - d_{2}) + 2sign(i_{c})(1 - d_{3}) \right]$$

(2.13)

From above equations, it can be depicted that the voltage is current direction dependent, so to make it independent from it, the following control variable is determined,

$$d_{k} = 1 - d_{k}^{'} \left[ sign(i_{x}) - \frac{\Delta V_{c}}{V_{dc}} \right]$$

(2.14)

Where,  $\Delta V_c$  is the mismatch between the bus capacitors voltage.

$$V_x = L_s \frac{di_x}{dt} + \frac{V_{dc}}{6} M d_k$$

(2.15)

Where,

$$M = \begin{pmatrix} 2 & -1 & -1 \\ -1 & 2 & -1 \\ -1 & -1 & 2 \end{pmatrix}$$

$$C_o \frac{dV_{dc}}{dt} = \sum_{k=1}^{3} (1 - d_k) sign(i_x) i_x - I_o$$

(2.16)

$$C_o \frac{d\Delta V_c}{dt} = \sum_{k=1}^{3} d_k^{'} \left[ sign(i_x) - \frac{\Delta V_c}{V_{dc}} \right] i_x$$

(2.17)

The above equations is also time dependent so using abc to dq transform to get following control equations,

$$\frac{di_d}{dt} = \frac{1}{L_s} \left( V_d + L_s \omega_s i_q - \frac{V_{dc}}{2} d_d^{'} \right)$$

(2.18)

$$\frac{di_q}{dt} = \frac{1}{L_s} \left( V_q - L_s \omega_s i_q - \frac{V_{dc}}{2} d_q^{'} \right)$$

(2.19)

$$\frac{dV_{dc}}{dt} = \frac{1}{C_o} \left[ \frac{3}{2} \left( d_d^{'} i_d + d_q^{'} i_q \right) - \alpha \frac{\Delta V_c}{V_{dc}} d_o^{'} i_d - I_o \right]$$

(2.20)

$$\frac{d\Delta V_c}{dt} = \frac{1}{C_o} \left[ -\frac{3}{2} \frac{\Delta V_c}{V_{dc}} \left( d_d^{'} i_d + d_q^{'} i_q \right) - \alpha d_o^{'} i_d \right]$$

(2.21)

Where,

$$\alpha = \frac{2}{\pi} = 0.64$$

The static duty cycle in dq0 reference frame is written as,

$$D_{d}' = \frac{2V_{d}}{V_{dc}^{*}}; \quad D_{q}' = \frac{2L_{s}\omega_{s}I_{d}}{V_{dc}^{*}}; D_{o}' = 0$$

(2.22)

The nominal points are calculated as,

$$\begin{bmatrix} V_d \\ V_q \\ V_o \end{bmatrix} = \begin{pmatrix} \sqrt{2}V_{abc} \\ 0 \\ 0 \end{pmatrix} \begin{bmatrix} I_d \\ I_q \\ I_o \end{bmatrix} = \begin{pmatrix} \sqrt{2}I_{abc}^* \\ 0 \\ 0 \end{pmatrix}$$

(2.23)

$$V_{dc} = V_{dc}^* \tag{2.24}$$

Where  $V_{abc}$ = rms grid voltage,  $I_{abc}$ \*= reference grid current,  $V_{dc}$ \*= reference bus voltage.

The small signal modelling leads to,

$$\dot{\tilde{X}}(t) = A\tilde{X}(t) + B\tilde{d}(t) + E\tilde{V}(t)$$

(2.25)

Where  $\tilde{X} = \text{state}$  variable vector;  $\tilde{d} = \text{control}$  input vector;  $\tilde{V} = \text{input}$  disturbance vector and A, B, E are their respective matrices.

$$\tilde{X} = \begin{bmatrix} \tilde{i}_d \\ \tilde{i}_q \\ \tilde{v}_{dc} \\ \Delta \tilde{v}_c \end{bmatrix}; \tilde{d} = \begin{bmatrix} \tilde{d}_d \\ \tilde{d}_q \\ \tilde{d}_o \end{bmatrix}; \tilde{v} = \begin{bmatrix} \tilde{v}_d \\ \tilde{v}_q \end{bmatrix}$$

(2.26)

The matrices A, B, E can be evaluated as,

$$A = \left(\frac{\partial f}{\partial X}\right)_{X = X_o}, \quad B = \left(\frac{\partial f}{\partial d}\right)_{X = X_o}, \quad E = \left(\frac{\partial f}{\partial v}\right)_{X = X_o}$$

(2.27)

$$A = \begin{bmatrix} 0 & \omega_{s} & -\frac{\sqrt{2}V_{abc}}{L_{s}V_{dc}^{*}} & 0 \\ -\omega_{s} & 0 & \frac{\omega_{s}\sqrt{2}I_{abc}^{*}}{V_{dc}^{*}} & 0 \\ \frac{3\sqrt{2}V_{abc}}{C_{o}V_{dc}^{*}} & -\frac{3\sqrt{2}L_{s}\omega_{s}I_{abc}^{*}}{C_{o}V_{s}^{*}} & -\frac{1}{C_{o}R_{o}} & 0 \\ 0 & 0 & 0 & -\frac{6V_{abc}I_{abc}^{*}}{C_{o}V_{dc}^{*2}} - \frac{1}{C_{o}R_{o}} \end{bmatrix}$$

(2.28)

$$B = \begin{bmatrix} -\frac{V_{dc}^*}{2L_s} & 0 & 0\\ 0 & -\frac{V_{dc}^*}{2L_s} & 0\\ \frac{3\sqrt{2}I_{abc}^*}{2C_o} & 0 & \frac{\alpha\sqrt{2}I_{abc}^*}{C_o} \end{bmatrix}; E = \begin{bmatrix} \frac{1}{L_s} & 0\\ 0 & \frac{1}{L_s}\\ 0 & 0\\ 0 & 0 \end{bmatrix}$$

(2.29)

Using laplace transform,

$$\tilde{X}(s) = (sI - A)^{-1} B\tilde{d}(s) + (sI - A)^{-1} E\tilde{v}(s)$$

(2.30)

Using (2.30) various transfer function can be analyzed accordingly.

For example,

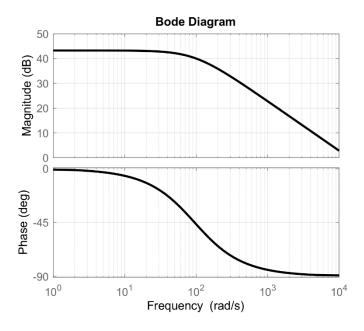

$$\frac{\Delta V_c(s)}{d_o'(s)} = \frac{2\sqrt{2}R_o}{\pi} * \left[ \frac{1}{2 + (R_oC_o)s} \right]$$

(2.31)

The bode plot of above transfer function is shown in Fig.2.10.

Fig.2.10. Bode plot of  $\Delta V_c(s)/d_0'(s)$

#### 2.5 CHAPTER SUMMARY

In this chapter complete analysis of Vienna rectifier is discussed with all modes of operation for a complete sector 1. It also includes designing of Vienna rectifier to achieve required DC bus voltage and near to unity power factor. The small signal modelling is also studied to design the controlling loops for mitigating both the grid side and load side variations.

#### **CHAPTER 3**

#### **CONTROL OF VIENNA RECTIFIER**

#### 3.1 INTRODUCTION

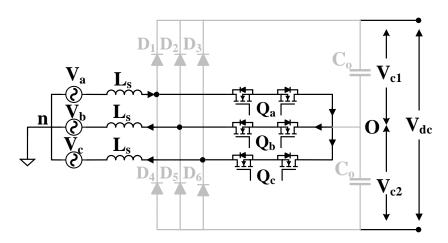

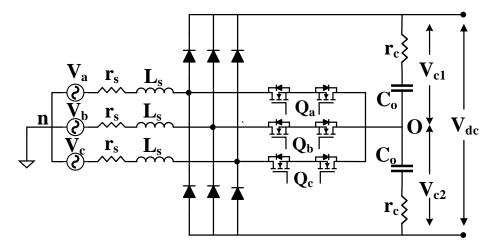

The need for higher power ratings and efficient AC-DC conversion led to opting of Vienna Rectifier for off-board electric vehicle (EV) charging applications. In this chapter, a complete analysis of three phase Vienna Rectifier considering the effect of parasitic in the system for off-board EV charging application is discussed. To improve the dynamic response a modified dual loop control using d-axis and q-axis current controller including the effect of system parasitic in control loops is proposed. The proposed algorithm is compared with different control algorithms viz., dual loop control using hysteresis current controller and dual loop control using d-axis and q-axis current controller with SVPWM. A comparative performance analysis is discussed in terms of dynamic response during system disturbances like load variation, reference DC bus voltage variation and grid side variations. A 50 kW Vienna Rectifier operating at a switching frequency of 200 kHz is used for performance evaluation of all three control algorithms and is validated using MATLAB-Simulink. Fig.3.1. depicts the circuit diagram of Vienna rectifier considering system parasitic.

Fig.3.1. Three phase Vienna Rectifier circuit diagram including parasitic

### 3.2 DUAL LOOP CONTROL USING HYSTERESIS CURRENT CONTROLLER

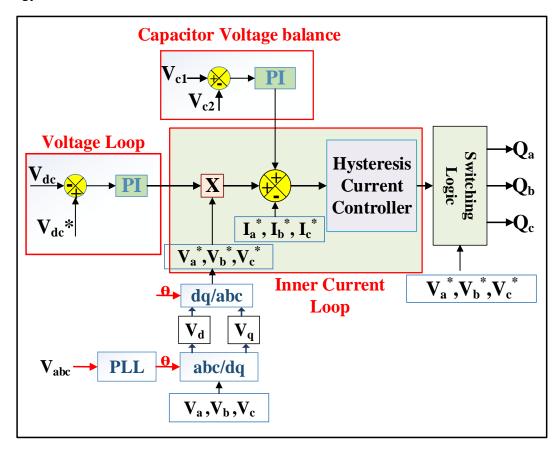

In this control strategy, there involves different controlling loops, an outer control loop for DC bus voltage uses a PI controller to provide reference signals. The generated reference signals are provided to the inner current control loops and hysteresis controllers which are used instead of PI controller. Three-phase PLL is designed to provide clocking frequency theta/ $\omega$ t for abc/dq0 and dq0/abc transformations. The three-phase voltages are transformed into alpha-beta and thereafter to d-q transform to extract three phase reference voltages,  $V_a$ \*,  $V_b$ \* and  $V_c$ \*. Finally the output of hysteresis controller for the inner control loops is compared with  $V_a$ \*,  $V_b$ \* and  $V_c$ \* respectively. Switching pulses for controlled bidirectional switches are obtained and Fig.3.2 depicts control block diagram for this control strategy [35].

Fig.3.2. Block diagram of dual loop control using hysteresis current control scheme

## 3.3 DUAL LOOP CONTROL USING D-AXIS AND Q-AXIS CURRENT CONTROLLER WITH SVPWM

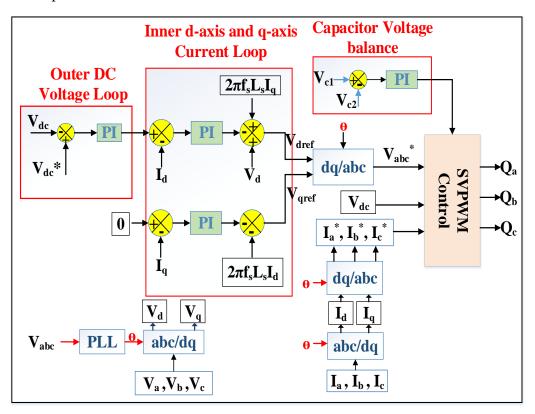

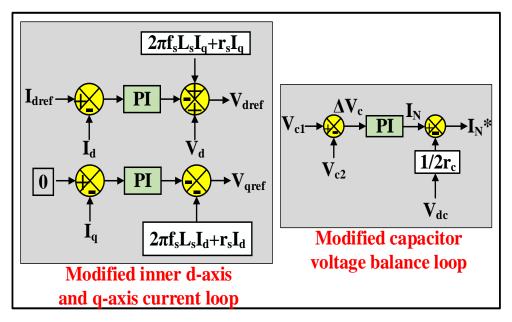

The dual loop control strategy using hysteresis controller is able to provide power factor which tends to unity and able to achieve the THD under EV standards but it is not able to mitigate the 1% variations in grid frequency. So, a dual loop control using d-axis and qaxis current control strategy is adopted for further analysis of Vienna Rectifier [36]. In this strategy one loop will be the inner control loop which includes the d-axis current,  $I_d$  and qaxis current,  $I_q$  control. Second loop is the outer voltage control loop where the output voltage is compared with the DC bus reference voltage and the voltage error is provided to a PI controller and output of this PI controller is reference d-axis current,  $I_{dref}$  and compared with the  $I_d$  and the error is provided to a PI Controller and generated output is summed with the expression,  $V_d + 2\pi f_s L_s I_q$  using (3.4) to generate reference d-axis voltage  $V_{dref}$ . Similarly for qaxis controller,  $I_q$  is compared with 0 to reduce or eliminate reactive component. The error is provided to the PI controller and the generated output is differenced from an expression,  $2\pi f_s L_s I_d$  using (3.1) to generate reference q-axis voltage  $V_{qref}$ . Next step is to convert  $V_{dref}$ ,  $V_{qref}$  and 0 to three phase reference voltage,  $V_{abc}$ \* using dq0 to abc transformations. Clarke and Park transformation are utilized to transform the three phase grid voltages and current to alpha-beta and then to d-q respectively. Three-phase PLL is used to generate theta/ωt for the clarke and park transformations.  $I_d$  and  $I_q$  are transformed to three phase reference current,  $I_{abc}$ \* using dq0 to abc transform. In Vienna Rectifier, the main concern is the capacitor voltage balancing. So, here a proportional controller is incorporated to ensure that the voltage across the capacitors remains balanced under various dynamic changes in the system, to ensure the desired output bus voltage. Fig.3.3 depicts block diagram for this control strategy [36]. The final step includes generation of pulses for the three bi-directional switches using SVPWM. The input Control parameters to the SVPWM pulse generator are  $V_{abc}^*$ ,  $I_{abc}^*$  and controller output for the capacitor voltage balancing.

The control loops are designed using following calculated equations,

$$V_{q_{ref}} = \begin{cases} -\left(K_{p_{i_q}}(0 - I_q) + K_{i_{i_q}} \int (0 - I_q) dt\right) \\ -2\pi f_s L_s I_d \end{cases}$$

(3.1)

$$I_{d_{ref}} = K_{p_{v_{dc}}}(V_{dc}^* - V_{dc}) + K_{i_{v_{dc}}} \int (V_{dc}^* - V_{dc}) dt$$

(3.2)

$$\Delta V_c = K_{p_{v_c}} (V_{c_1} - V_{c_2}) + K_{i_{v_c}} \int (V_{c_1} - V_{c_2}) dt$$

(3.3)

$$V_{d_{ref}} = \begin{cases} K_{p_{i_d}} \left( I_{d_{ref}} - I_d \right) + \\ K_{i_{i_d}} \int \left( I_{d_{ref}} - I_d \right) dt \\ + V_d + 2\pi f_s L_s I_q \end{cases}$$

(3.4)

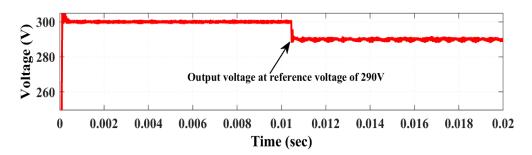

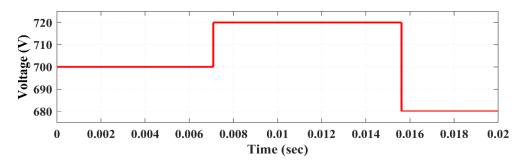

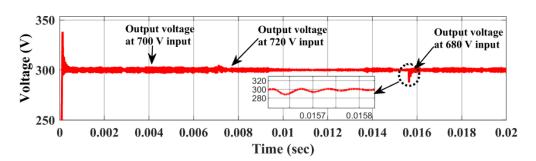

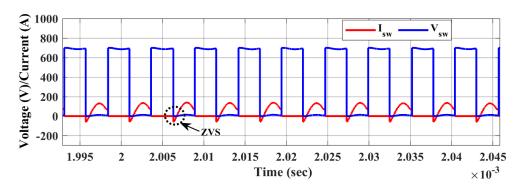

$$V_{dc} = V_{c_1} + V_{c_2} (3.5)$$