# IMPLEMENTATION OF HIGH PERFORMANCE ROUTER USING FSM, SYNCHRONIZER AND FIFO

PROJECT REPORT

MASTER OF TECHNOLOGY IN

VLSI DESIGN AND EMBEDDED SYSTEMS

Submitted by: Manshi Singh 2K20/VLS/11

Under the supervision of Mr. LOKESH GAUTAM Assistant Professor

# DEPARTMENT OF ELECTRONICS AND COMMUNICATION ENGINEERING

DELHI TECHNOLOGICAL UNIVERSITY

(Formerly Delhi College of Engineering) New Delhi-110042

# DEPARTMENT OF ELECTRONICS AND COMMUNICATION ENGINEERING

## DELHI TECHNOLOGICAL UNIVERSITY

(Formerly Delhi College of Engineering) New Delhi-110042

# **CANDIDATE'S DECLARATION**

I MANSHI SINGH student of M.Tech (VLSI and Embedded Systems), hereby declare that the project Dissertation titled "IMPLEMENTATION OF HIGH PERFORMANCE ROUTER USING FSM, SYNCHRONIZER AND FIFO" which is submitted by me to the Department of Electronics and Communication Engineering, Delhi Technological University, for open area seminar, is original and not copied from any source without proper citation.

Place: Delhi

Date: 22.05.2022

Manshi Singh (2K20/VLS/11)

# DEPARTMENT OF ELECTRONICS AND COMMUNICATION ENGINEERING

## DELHI TECHNOLOGICAL UNIVERSITY

(Formerly Delhi College of Engineering) New Delhi-110042

# **CERTIFICATE**

I hereby certify that the Project Report titled "IMPLEMENTATION OF HIGH PERFORMANCE ROUTER USING FSM, SYNCHRONIZER AND FIFO" which is submitted by Manshi Singh (2K20/VLS/11) of Electronics and Communication Department, Delhi Technological University, Delhi for the Innovative work , is a record of the project work carried out by the students under my supervision.

Place: Delhi

Date: 31.05.2022

Mr. LOKESH GAUTAM

Assistant Professor

for esh

**ACKNOWLEDGEMENT**

A successful project can never be prepared by the efforts of the person to whom

the project is assigned, but it also demands the help and guardianship of people

who helped in completion of the project. I would like to thank all those people who

have helped us in this research and inspired me during my study.

With profound sense of gratitude, I thank Mr. Lokesh Gautam my Research

Supervisor, for his encouragement, support, patience and his guidance in this

project work. I heartily appreciate the guidance given by him in the project

presentation that has improved my presentation skills with his comments and

advices. I take immense delight in extending my acknowledgement to my family

and friends who have helped me throughout this project work.

Manshi Singh

Roll no: 2K20/VLS/11

4

# **ABSTRACT**

Routing is defined as procedure of transferring any sort of data in compact form from sender to receiver and this is a step by step process i.e. one after another until target receiver is found. This process requires some sort of data that has the address of the client or destination. This process of routing message from source to client or destination happens at networking layer of OSI model. Hence it follows all the protocols of networking layer. The transmission or transition of data through router occurs in the form of packets, which usually contains header byte, payload and parity (trailer). Header will contain destination or client address and the upcoming size of payload byte. Payloads are the actual message or data which needs to be forwarded to destination network by the router. Trailer byte is for error detection. We use router as a networking device that advances data frames with computer and networks on other side. Router can be linked to more than two lines from various networks (this process is totally opposite of working of network switch that is used to establish a link data line and network). Project that is performed by me is basically based on few topic like working of router, its top model architecture, working of its other parts i.e. FIFO, FSM and Register.

# **Table of Contents**

| Candidate's D   | eclaration                   | 2  |

|-----------------|------------------------------|----|

| Certificate     |                              | 3  |

| Acknowledger    | ment                         | 4  |

| Abstract        |                              | 5  |

| List of Figures | S                            | 9  |

| Chapter 1: In   | troduction                   | 10 |

| 1.1 Types       | of Router                    | 11 |

| 1.1.1           | Non-modular Router           | 11 |

| 1.1.2           | Modular Router               | 11 |

| 1.1.3           | Edge Router                  | 12 |

| 1.1.4           | Subscriber Edge Router       | 12 |

| 1.1.5           | Inter Provider Border Router | 12 |

| 1.1.6           | Core Router                  | 12 |

| 1.1.7           | Wired and Wireless Router    | 12 |

| 1.2 Metho       | odology                      | 13 |

| 1.3 Motiv       | ation                        | 13 |

| Chapter 2: Ro   | outer Design                 | 14 |

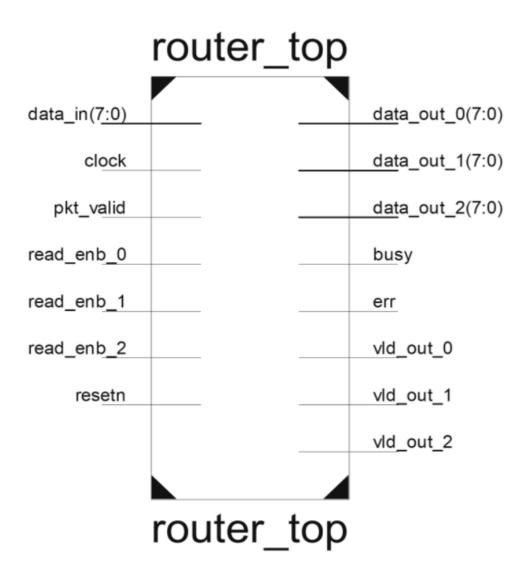

| 2.1 Route       | er: Top Level Block          | 14 |

| 2.2 Top E       | Block of Router              | 14 |

| 2.3 Top L       | Level Architecture           | 15 |

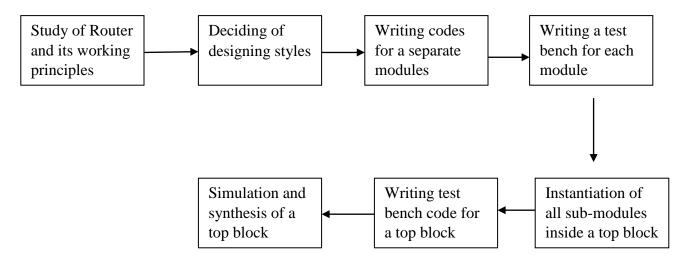

| 2.4 Progr       | ress of Work                 | 15 |

| 2.5 Work        | Plan                         | 16 |

| 2.6 Router      | r Features                   | 16 |

| 2.7 Packet      | t Format                     | 17 |

| 2.8 Router: Input Protocol                      | 18 |

|-------------------------------------------------|----|

| 2.9 Router: Output Protocol.                    | 19 |

| Chapter 3: Sub Module Functionality Description | 20 |

| 3.1 Router: FIFO                                | 20 |

| 3.1.1 Functionality                             | 20 |

| 3.1.2 Read Operation.                           | 21 |

| 3.2 Router: Synchronizer                        | 22 |

| 3.2.1 Functionality                             | 22 |

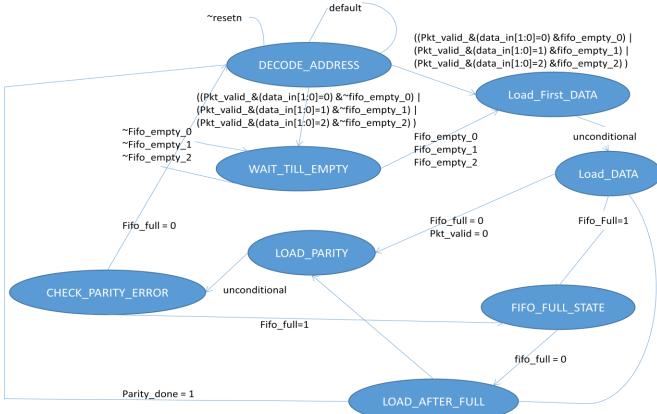

| 3.3 Router: FSM                                 | 23 |

| 3.3.1 State: Decode Address                     | 24 |

| 3.3.2 Sate: Load First Data                     | 24 |

| 3.3.3 State: Load Data                          | 24 |

| 3.3.4 State: Load Parity                        | 24 |

| 3.3.5 State: FIFO Full State.                   | 25 |

| 3.3.6 State: Load After Full.                   | 25 |

| 3.3.7 State: Wait Till Empty                    | 25 |

| 3.3.8 State: Check Parity Error.                | 25 |

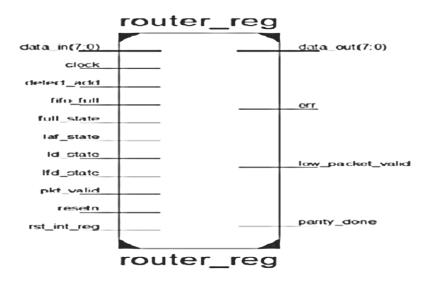

| 3.4 Router: Register                            | 26 |

| 3.4.1 Functionality                             | 27 |

| Chapter 4: Simulation Results.                  | 28 |

| 4.1 Router: Top Level                           | 28 |

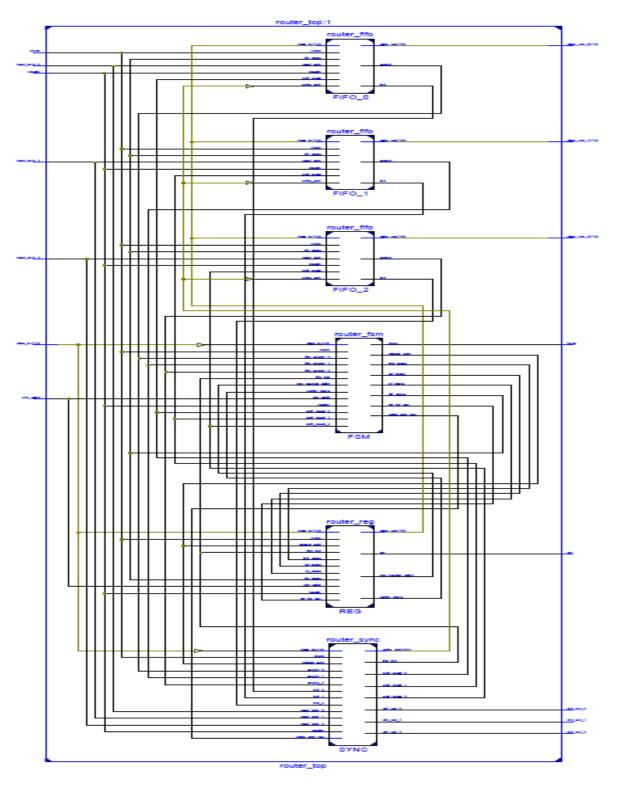

| 4.2 Overall Schematic                           | 29 |

| References             | 37 |

|------------------------|----|

| Chapter 5: Conclusion  |    |

| 4.5 Tools Used         | 35 |

| 4.4 Synthesis Reports  | 32 |

| 4.3 Simulation Results | 30 |

## **List of Figures**

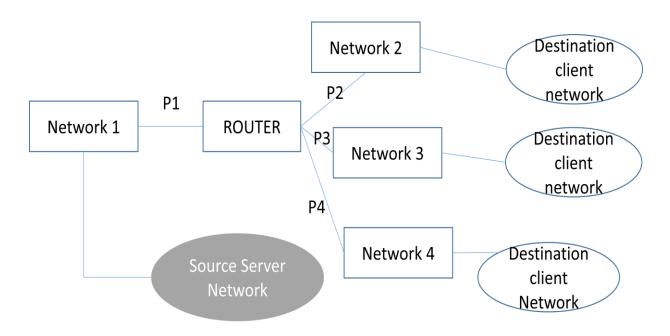

**Figure 1.1** – Connectivity of Router

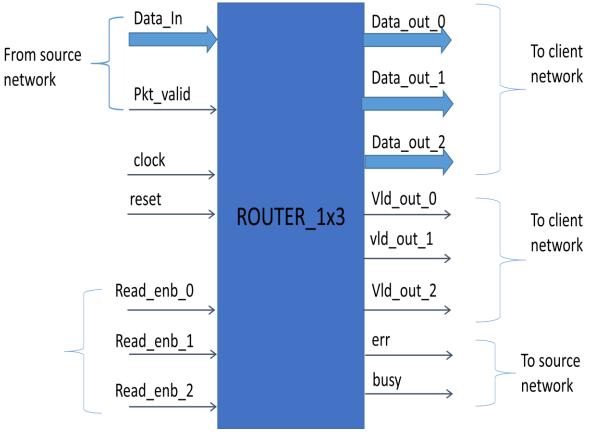

**Figure2.1**– Top level block

**Figure2.2**– Top level Architecture of Router

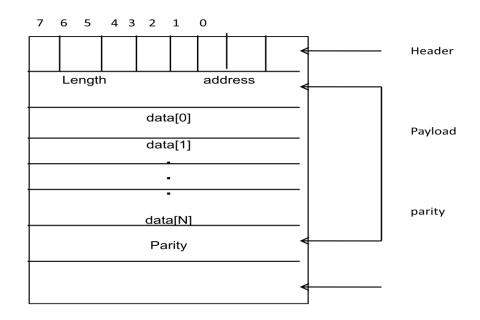

Figure 2.3- Packet format

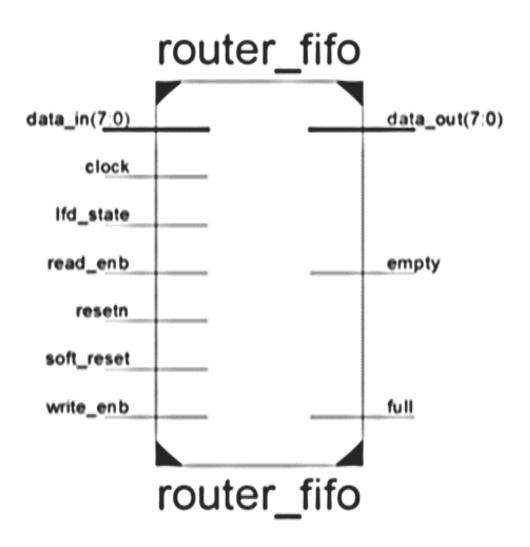

Figure 3.1 – RTL Sc hematic of Router FIFO

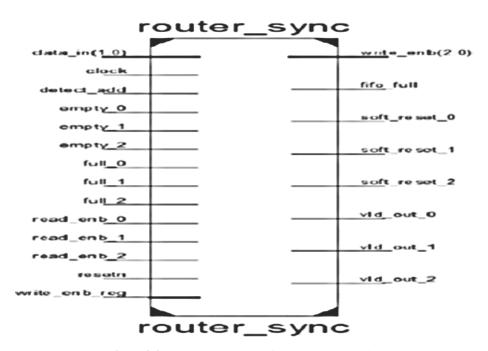

Figure 3.2 – RTL Schematic of Router Synchronizer

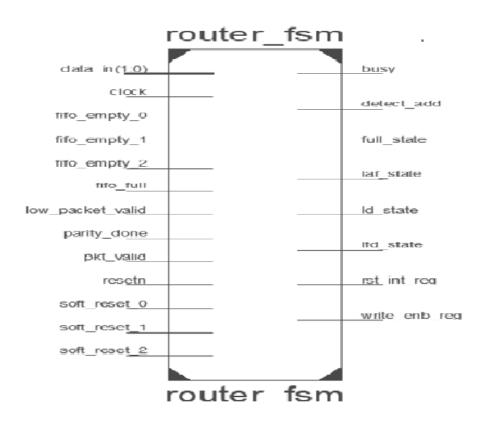

Figure 3.3 – RTL Schematic of Router FSM

**Figure3.4** – Diagram of FSM

**Figure3.5** – RTL Schematic of Router Register Block

Figure 4.1 – Block Diagram of Router

Figure 4.2 – Overall RTL Schematic of Router

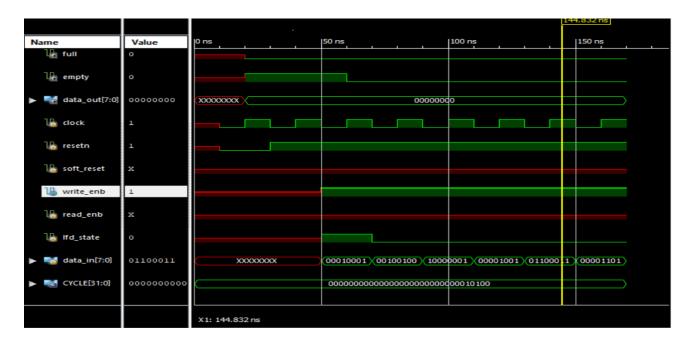

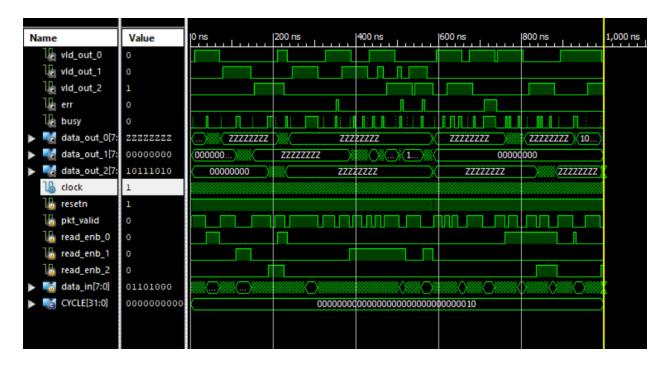

**Figure 4.3** – Output of FIFO

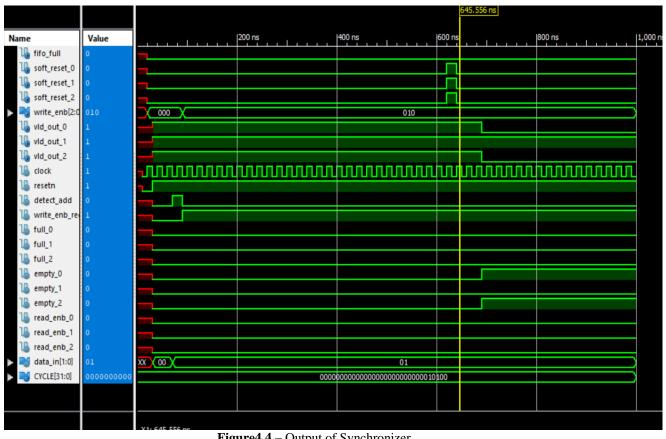

**Figure 4.4** – Output of Synchronizer

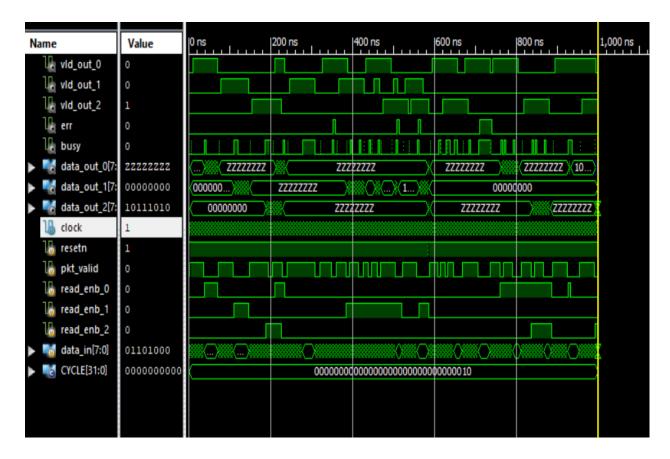

**Figure 4.5** – Output of Synchronizer

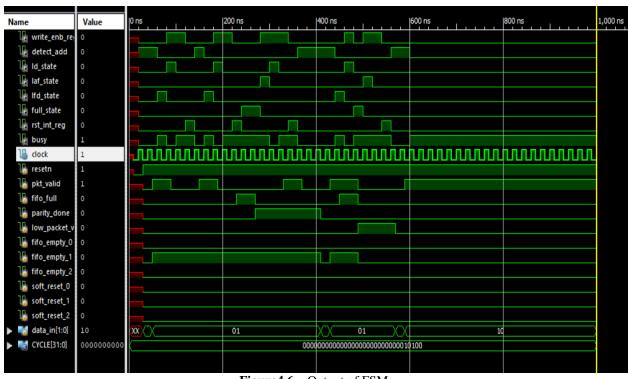

**Figure4.6** – Output of FSM

**Figure4.7** – Output of FSM

**Figure 4.8** – Synthesis options summary

**Figure 4.9** – Synthesis options summary

Figure 4.10 – HDL Synthesis Report

Figure 4.11 – Advanced HDL Synthesis Report

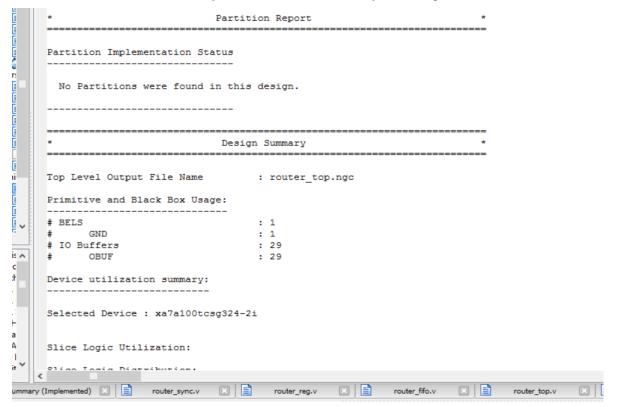

**Figure4.12** – Design Summary

## Chapter 1

# **INTRODUCTION**

A router is a device used in networking, universally dedicated hardware that forward data package from one computer networks to another. This forms overlay between internetworks, as routers are connected in between two or multiple data lines from various networks. Whenever a packet which contains any information (data) is encountered at any network line, router will try to get the address of the its receiver that is stored in that data packet which was encountered. After collecting information this will send the packet to next network according to the its table. Functioning of routers are similar to "traffic flow guide". The process of sending data packet is from sender to receiver that is routers with the help of different network till it reaches to receiver side router. Home-based and minor office routers are most familiar sort of routers which only allows data like email, web page, videos, and IM between a household computers and interent.

**Figure 1.1** – Connectivity of Router

## 1.1 Types of Router:

#### 1) On basis of Configuration or Flexibility:

#### 1.1.1 Non-modular router

Generally, Low-end routers are referred as Non-modular router which have interfaces which cannot be changed, like if we want to add or subtract ports or interface at later stage then we cannot do so. These routers are mainly accommodated in houses or small groups to connect. Non-modular type of router gives SLIP or PPP connection as well as it is compatible with some other protocols and few of them are virtual private network protocols PPTP and IPSec, etc. Technology such as ADSL will shortly improve the whole situation existing for every broadband, and this leads will lead to increment in the access router afford. Due to scenarios like this, Non-modular router will be able establish compatibility between various heterogeneous and high-speed ports in the future, and with the capability to execute more than one protocols on every port.

#### 1.1.2 Modular router

Router which is able to extendable with particular components are described by the term Modular router, we can add router with features such as encryption accelerators, sound processing modules, interfaces, etc. This type of routers basically denotes routers like interface type and some extension which are accommodated as per requirements of user router and configurable at the factory, these types of devices mainly gives the basic routing features, like users can establish a connection to a fixed sort of network to choose the useful module, different connectivity and management capabilities can be given by various modules. Taking an example, majorly modular router provides flexibility to users so that they can choose network interface type, modular routers are able to offer VPN and various functional modules, and few of the this type of routers are eligible to give firewall functions, and much more. Major number of present routers are modular router. These devices basically establishes connection among enterprises, one enterprise and other the Internet, this is inside an Internet Service Provider (ISP). As an example Cisco Juniper T1600 or CRS-1 provides interconnection between ISP, and they are incorporated inside ISP, either this can be accommodated in large scale enterprise network.

Smallest router are basically used to establish connections inside the small and home offices.

## 2) On the basis of Applications:

### 1.1.3 Edge Router

Basically this kind i.e. Edge router is incorporated at edges of any Internet Service Provider network, edge routers are majorly organized between protocols like from Border gateway protocol to one other BGP of one other Internet Service Providers or big association.

#### 1.1.4 Subscriber Edge Router

Subscriber Edge is a kind of routers which have its place an edge of a subscribers network. This type of router are constructed to broadcast External BGP to its provider's.

#### 1.1.5 Inter Provider Border Router

It is a kind of router which is incorporated to establish a connection between ISPs from one another. It is working like a BGP dialogue router which can maintains BGP sessions between same type of BGP dialogue routers in other provider's.

#### 1.1.6 Core Router

Core routers is a type of router that is placed in the center or backbone structure of any LAN networks, that means it is not placed at any boundary. In illustrations, core router delivers a step-down backbone, establishing connection between distribution router begins at various office block (LAN), or Large enterprise Location (WAN). These are incorporated in any system when we want optimization for high bandwidth.

#### 1.1.7 Wired and Wireless Routers

The widespread of houses and small scale industries networking is increasing rapidly by using this kind of routers. These kinds of routers has the power so that it can organize routing and configuration data in particular table used for routing. It can also give the facility of segregating circulation of data package on the basis of their IP addresses. Few of wireless kind of routers syndicates the purpose of router with network switch and an firewall as an single entity.

## 1.2 Methodology:

Methodology can be classified into 3 main stages:-

- Xilinx ISE (Integrated Synthesis Environment) consists of total three kinds of lineups for Designing, Simulating and Implementing respectively.

- For Design and simulation simple Verilog HDL code file which is of .v type is castoff (also known as Testbench file). For Implementation Constraint File .ucf is used to design. The code for designing of module has to be set as a Top module.

- We can use any kind of modelling out of three i.e. Dataflow, Behavioral and structural modeling. Testbench file deliver different users input comprises clock signal to design which is inevitable to support simulate the design and analyze that designed module is working as per our requirement.

## 1.3 Motivation:

- Objective of the project is to provide efficient router architecture having three in no. output port selected according to header, which must contains address of the port.

- Old router uses OSI model; which have seven in numbers of layer so for transmitting a

data package it takes additional time in compare to TCP model, which have only four in

numbers of layer, so time taken for transmitting a package is less, therefore overall speed

increases.

## **Chapter 2**

# **Router Design**

## 2.1 Router: Top Level block

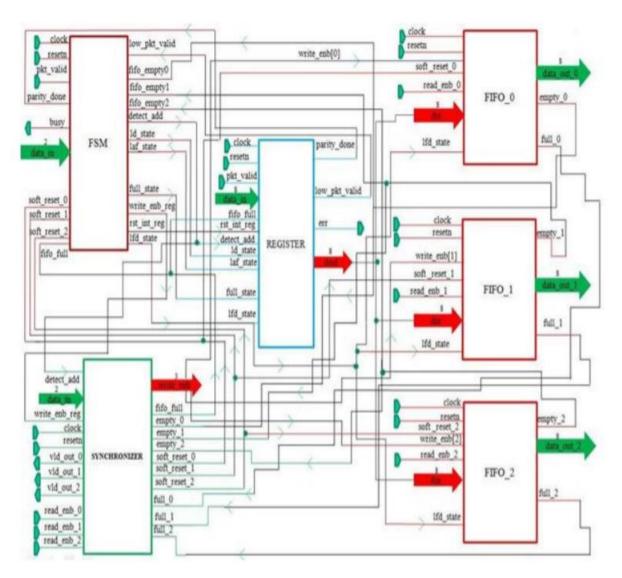

The construction of a top level router is depicted in a diagram. SYNCHRONIZER, FSM, FIFO-0, FIFO-1, FIFO-2, and REGISTER are the components of a Router package. During the planning and implementation of the entire module, we develop each sub-module separately via RTL coding in a Verilog; and at that time we instantiate all submodules from the top using structural modelling and certain advanced Verilog structures.

## 2.2 Top Block of Router

Figure2.1- Top level block

## 2.3 Top Level Architecture

Figure 2.2 — Top level Architecture of Router

## 2.4 Progress of Work:

- Studied basic fundamentals of router and it's working principle.

- Studied about OSI Layers (Specially Network layer).

- Installed Xilinx ISE 14.7. Design Suite.

- For simulation and designing a simple .v form of Verilog module file is used(also acknowledged as Test bench file). A .ucf file is used for designing implementation constraints. The top module is designated as design file.

- The concept can be implemented using behavioral, dataflow, and structural modelling techniques. The Test bench file allows many different users to submit data, including a clock to the design file, which is required for simulation and testing of the design.

## 2.5 Work Plan:

#### 2.6 Router Features:

- **Packet Routing:-** The packets are from obtained an input ports and is routed towards an output port dependent on an receivers networks address.

- Parity Checking:- An error-recognition approach that verifies the truthfulness of digital data which has been sent between the server and the client. This is a technique that guarantees that data sent by the server network is correctly received and without corruption by a client network.

- **Reset**:- The router's condition is reset by a low active synchronous input, the routers FIFOs are rendered vacant, and a valid signal goes low; indicative of none of the valid packets are recognised on output data bus.

- **Sending Packet**:- Router input protocol.

• **Reading Packet:-** Router output protocol.

## 2.7 Packet Format:

The packets contains 3 parts-

- Header

- Payload

- Parity

Figure 1.3 - Packet Format

Each payload length and breadth of 8 bits can be expanded from 1 to 63 bytes.

Header: Package headers have 2 dimensions:- Destination Address and length.

• **Destination Address (DA)**: A package's destination address is 2-bit long. Based on the package's destination address, the router directs the package to its appropriate port. A 2-bit port address is assigned to each output port. If a package's destination address matches the address of a port, the router will send the package to the appropriate output port. '3' is not a valid address.

- Length: Six bits make up the data length. The number of data bytes is specified. A packet's data size cannot be less than 1 byte or greater than 63 bytes.

- If the length is equal to one, the data length is one byte.

- If the length is equal to two, the data is two bytes long.

- If the length equals three, the data length is three bytes.

- If the length equals 63, that signifies the data is 63\*8 bits long...

- **Payload:** The payload contains data statistics. Bytes are used to represent the data.

- **Parity**: This parameter verifies the package's security. For header and payload bytes, parity is determined bitwise.

## 2.8 Router :- Input Protocol

The following are some of the features of DUT input protocols:

- **Testbench Notes:** Except for the low reset, all inputs of the module are in sync with the negative edge of systems clock. This is owing to the DUT routers sensitivity to the clock's turning point i.e. when the clock is changing from 0 to 1. As a result, inputs of the module which are driving at the clocks edge when the clock is going from 1 to 0 in the test bench ensures setup and holds time. Signals which are obtained at the clock's another edge i.e. changing from 0 to 1, can be obtained using the clocking block itself in a Verilog/UVM system-based test-bench, avoiding meta-stability.

- At the clock's turning edge when header byte is being driven into the input bus, package valid signal is asserted.

- In the meantime, the header byte provides address of receiver, followed by the router's address to which package is being directed (data\_out 0; data\_out 1; data\_out 2).

- For every new falling edge of the clock, each following byte of payload shall be fed onto the data bus which is being used as input.

- After driving the preceding payload 8 bits to upcoming negative turning point of clock, the package-signal which is valid needs to be de-asserted, parity of the package should needs to be driven. This is being sensed as package is finished.

- When a busy signal is detected, the test-bench should not drive any of the bytes; as an alternative, it needs to have the values which are driven recently.

- If any of the incoming byte (8 bits) of information is dropped, then 'busy' signal is being asserted in the cycle.

- An "err" signal is inserted in the cycle if any of the packet's parity bit is not as required.

This is done at the time when it is recognized that parity bits is mismatched.

## 2.9 Router :- Output Protocol

Below mentioned are the features of any output protocol:

- Test-bench note: All the signals which are being used as output in the router module are actively high, they must be synchronized with the clock's rising edge i.e. when clock is getting from 0 to 1.

- A FIFO with a 16x9 capacity buffers each data out\_x (data out\_0, data out\_1, and data out\_2) output port.

- If any data which is genuine reaches at the vld out\_x (data out\_0, data out\_1, and data out\_2) output line, the router asserts vld out\_x (vld out\_0, vld out\_1, and vld out\_2) signal. It is in one of that signal which is used to direct to the receiver's client indicating that data is existing at specific output data line.

- If receiver's package want to grasp the package's bits before inserting read enb\_x (read enb\_0, read enb\_1, and read enb\_2) then it should be in waiting state till is has enough memory space to store data.

- When clock negative turning point i.e. transition from 1 to 0 comes, the read enb\_x (read enb\_0, read enb\_1, or read enb\_2) input signals could be inserted, allowing data to be read from data out\_x (data out\_0, data out\_1, or data out\_2) line.

- When read enb\_x (read enb\_0, read out\_1, or read out\_2) is inserted in the range of 30 clock cycles of vld out\_x (vld out\_0, vld out\_1, or vld out\_2), the FIFO will be reset.

- When a package header byte becomes corrupted due to a time-out event, then data out\_x

(data out\_0, data out\_1 or data out\_2) line is in Z state i.e. high impedance state

throughout the process.

## Chapter 3

# **Sub Module Functionality Description**

3.1 Router: FIFO

Figure 3.1 - RTL Schematic of Router FIFO

## **3.1.1 Functionality**

In the router design there are 3 FIFOs used. Each FIFO size is of 16 bits or 2 bytes depth and 9 bits wide. FIFO can be reset using a synchronizer which is actively low reset and is powered by the clock which is used in the system. Internally, a soft reset signal also resets the FIFO. The SYNCHRONIZER block generates a **soft\_reset** active high signal during the ROUTER's time

out state. When the value of **resetn** port's value is zero, empty=1, full is equal to 0 and data out is equal to zero 0 are the values.

Dimensions of FIFO m/m is 16\*9 bits. Detecting the header byte requires the following step: extra bit in a data width is added. The header byte i.e. 8 bits of a package is sensed by **Lfd\_state**. For remaining bytes, the bit which is at ninth position is 0 and for the header byte, it's value is equal to 1.

## Write Operation:-

- **Data\_in** signal's samples are being taken at positive transition of clock i.e. from 0 to 1 change, but only if the value **write\_enb** is equal to logic 1.

- To avoid an over run condition, write operation will be performed only if FIFO is vacant i.e. it does not has any data.

### 3.1.2 Read operation:-

- Data\_out signal is being recited at positive transition of clock i.e. from 0 to 1 change, but only but only if the value **read\_enb** is equal to logic 1.

- To avoid an under run state, read operation will be performed only if FIFO is not in the vacant state.

- When the header byte is read, the internal counter will have a value 1 more than the payload length (parity byte), and this value will be decreased by one after each clock until 0 is observed. Until the counter is reloaded with a fresh packet payload length, it will remain at 0.

- All through time-out condition, empty=1 and value of full is equal to 0.

- **Data\_out** is being driven into a Z state i.e. high-impedance state beneath two conditions:

- 1. When **read\_enb** reads the fifo m/m entirely (payload + header + parity).

- 2. When Router is under time-out conditions.

- Status Full-FIFO can be sensed as that every place within FIFO has been occupied or written.

- All locations inside FIFO are being analyzed and made empty is indicated by Empty-FIFO status.

## 3.2 Router: Synchronizer

Figure 3.2 – RTL Schematic of Router Synchronizer

## **3.2.1 Functionality:**

This sort of module is used to establish synchronization among two modules of router i.e. FSM and FIFO. It's useful for establishing secure communication between a single input and three output ports.

- The **data\_in** and **detect\_add** signals are being utilized to pick FIFO while waiting for the package routing for that FIFO is complete.

- Full\_status of FIFO\_0, FIFO\_1 or FIFO\_2 can be used to determine the signal fifo

\_full value.

- When **data\_in** has the value equals to 2"b00 then **full\_0** value will be assigned to **fifo\_full.**

- When **data\_in** has the value equals to 2"b01 then **full\_1** value will be assigned to **fifo\_full.**

- When **data\_in** has the value equals to 2"b02 then **full\_2** value will be assigned to **fifo\_full.**

- Signal vld\_out\_x is calculated which is being created on the FIFO's vacant condition as written:

- Value of **empty\_0** inverted and assigned to **vld\_out\_0**.

- Value of **empty\_1** inverted and assigned to **vld\_out\_1**.

- Value of empty\_2 inverted and assigned to vld\_out\_2.

- In process of writing operation in selected FIFO; for producing the write\_enb signal, a

write\_enb register indication is also used.

- soft\_reset\_0, soft\_reset\_1, soft\_reset\_2 are the 3 internal reset signal for each of the

FIFO respectively. It becomes equal to logic 1 if read\_enb\_x (read\_enb\_0,read\_out\_1,

read\_out\_2) is not inserted inside 30 cycle of clock of vld\_out\_x (vld out 0,vld out 1 or

vld out 2).

- Simultaneously we can read and write.

### 3.3 Router: FSM

Figure 3.3 – RTL Schematic of Router FSM

### 3.3.1 STATE -DECODE\_ADDRESS

- It is being used as the initial state.

- The **detect\_add** is added to state and utilized to sense any arriving packets. This is useful in latching first byte which is treated as header byte.

## 3.3.2 STATE-LOAD\_FIRST\_DATA

- The **lfd\_state** signal is injected into above mentioned block and is being utilized in accommodating first 8 bits data to FIFO.

- Signal **busy** can be used in above condition to appropriately latch the header byte and prevent it from being modified with a new value for the current packet.

- In the upcoming clock, this state will be renamed LOAD DATA without any condition checking.

## 3.3.3 STATE-LOAD\_DATA

- The lfd\_state signal is injected into above mentioned block and is being utilized in loading payload data into FIFO.

- In above condition, busy state is de inserted, making the ROUTER ready to receive new data from the source.

- In above mentioned state, the signal **write\_enb\_reg** is being utilized in writing packet information i.e. summation of header, payload and parity to appropriate FIFO.

- When pkt\_valid is low, it switches to LAOD PARITY, and when the FIFO is full, it

switches to IFO\_FULL\_STATE. Signal busy is de inserted in above state to make

ROUTER ready to accept upcoming data from sender.

## 3.3.4 STATE-LOAD\_PARITY

- Above mentioned state is utilized to latch the last byte i.e. parity 8 bits.

- This goes without any condition to CHECK\_PARITY\_ERROR state.

- Signal busy is inserted to stop the ROUTER from receiving any upcoming data.

• write\_enb\_reg is set as logic 1 to latch the parity 8 bits to FIFO.

#### 3.3.5 STATE-FIFO\_FULL\_STATE

- Signal busy alloted as logic 1 but the signal write\_enb\_reg is set as logic 0.

- Signal **full\_state** is inserted to check for the state of FIFO whether it is full or not.

#### 3.3.6 STATE-LOAD AFTER FULL

- After FIFO\_FULL\_STATE, the laf\_state signal is introduced, and it is utilized for latching out the information.

- Write\_enb\_reg is accommodated despite the signal busy.

- It looks for the parity\_done signal, and if it is logic 1, it indicates that the

LOAD\_PARITY state has encountered, then proceeds towards DECODE\_ADDRESS.

- When low\_packet\_valid is sensed as logic 1, the state will be LOAD PARITY;

otherwise, it will be LOAD DATA state.

#### 3.3.7 STATE-WAIT\_TILL\_EMPTY

• Signal **busy** is set at logic 1 and signal **write\_enb\_reg** is set as logic 0.

#### 3.3.8 STATE-CHECK\_PARITY\_ERROR

- At this point, the rst\_int\_reg signal is generated, which is then utilized to reset low\_packet\_valid signal.

- When the FIFO is not full, this stage switches to DECODE ADDRESS, and when the FIFO is full, it switches to FIFO FULL STATE.

- In this stage, the **busy** is inserted.

# FSM State Diagram

Figure3.4 – Diagram of FSM

## 3.4 Router: Register

Figure3.5 – RTL Schematic of Router Register Block

### **3.4.1 Functionality:**

This module implements 4 internal registers in order to hold a header byte, FIFO full state byte, internal parity and packet parity byte. All the registers in this module are latched on the rising edge of the **clock**.

- If **resetn** is low then the signals (**dout,err,parity\_done and low\_pkt\_valid**) are low.

- The signal **parity\_done** is high under the following conditions:

- When signal **ld state** is high and signals (**fifo full and pkt valid**) are low.

- When signals laf\_state and low\_pkt\_valid both are high and the previous value of parity\_done is low.

- rst\_int\_reg signal is used to reset low\_pkt\_valid signal.

- **detect\_add** signal is used to reset **parity\_done** signal.

- Signal low\_pkt\_valid is high when ld\_state is high and pkt\_valid is low.

Low\_packet\_valid shows that pkt\_valid for current state has been deasserted.

- First data byte i.e., header is latched inside an internal register when detect\_add and pkt\_valid signals are high. This data is latched to the output dout when lfd\_state goes high.

- Then signal data\_in i.e. Payload is latched to dout if ld\_state signal is high and fifo\_full is low.

- Signal data\_in is latched to an internal register when **ld\_state** and **fifo\_full** are high. This data is latched to output **dout** when laf\_state goes high.

- **Full\_state** is used to calculate internal parity.

- Another internal register is used to store internal parity for parity matching. Internal

parity is calculated using the bit-wise xor operation between header byte, payload byte

and previous parity values as shown below:

```

parity_reg=parity_reg_previous^header_byte ---- t1 clock cycle

parity_reg=parity_reg_previous^header_byte ---- t1 clock cycle

parity_reg=parity_reg_previous^header_byte ---- t1 clock cycle

parity_reg=parity_reg_previous^header_byte ---- t1 clock cycle Last payload byte

□ The err is calculated only after packet parity is loaded and goes high if the packet parity doesn"t match with the internal parity.

```

# **Chapter 4**

# **Simulation Results**

**4.1 Router: Top Level**

Figure 4.1 – Block Diagram of Router

## **4.2 Overall Schematic**

Figure 4.2—Overall RTL Schematic of Router

## 4.3 Simulation Results

**Figure4.3** – Output of FIFO

Figure 4.4 – Output of Synchronizer

**Figure 4.5** – Output of Synchronizer

Figure 4.6 – Output of FSM

Figure 4.7 – Output of FSM

## 4.4 Synthesis Reports:

Figure 4.8 – Synthesis options summary

```

--- Target Options

LUT Combining

: Auto

Reduce Control Sets

: Auto

Add IO Buffers

: YES

Global Maximum Fanout

: 100000

Add Generic Clock Buffer (BUFG)

: 32

: YES

Register Duplication

Optimize Instantiated Primitives : NO

Use Clock Enable

: Auto

Use Synchronous Set

: Auto

Use Synchronous Reset

: Auto

Pack IO Registers into IOBs

: Auto

Equivalent register Removal

: YES

---- General Options

Optimization Goal

: Speed

Optimization Effort

: 1

Power Reduction

: NO

Keep Hierarchy

: No

Netlist Hierarchy

: As_Optimized

RTL Output

: Yes

Global Optimization

: AllClockNets

Read Cores

: YES

: NO

Write Timing Constraints

Cross Clock Analysis

: NO

Hierarchy Separator

Bus Delimiter

: Maintain

Case Specifier

Slice Utilization Ratio

: 100

: 100

BRAM Utilization Ratio

DSP48 Utilization Ratio

: 100

Auto BRAM Packing

Slice Utilization Ratio Delta

ary (Implemented) 🔞 🖹 router_sync.v 🔞 🖺 router_reg.v 🔯 🖺 router_ffo.v 🔯 🗐 router_top.v 🔯 🗐 router_t

```

Figure 4.9 – Synthesis options summary

```

'| 🧇 || 종 👊 🖆 ᄎ | 역 💌 | 🤊 🗗 🎤 🎤 💯 🎜 🎜 🛛 💹 🚰 🖽 🖽 🖳 🚩 🏕 [ 🚩 🏖 禾 || 🔻

HDL Synthesis Report

Macro Statistics

# Adders/Subtractors

: 12

5-bit adder

6-bit addsub

: 9

1-bit register

144-bit register

2-bit register

5-bit register

6-bit register

8-bit register

# Comparators

: 10

5-bit comparator equal

6-bit comparator greater

8-bit comparator not equal

# Multiplexers

: 68

1-bit 16-to-1 multiplexer

1-bit 4-to-1 multiplexer

: 1

3-bit 4-to-1 multiplexer

: 1

5-bit 2-to-1 multiplexer

6-bit 16-to-1 multiplexer

6-bit 2-to-1 multiplexer

8-bit 16-to-1 multiplexer

8-bit 2-to-1 multiplexer

9-bit 2-to-1 multiplexer

: 48

# FSMs

# Xors

: 2

8-bit xor2

I)INFO:Xst:1767 - HDL ADVISOR - Resource sharing has identified that some arithmetic operations in this

rry (Implemented) | router sync.v | router reg.v | router fifo.v | router top.v | router top.v

```

Figure 4.10 – HDL Synthesis Report

```

|| 🖔 || 🖟 || 🕒 || × || 10 || × || * || 🔑 || 2 || 9 || 9 || # || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 || 10 |

Synthesizing (advanced) Unit <router_sync>.

The following registers are absorbed into counter <counter_0>: 1 register on signal <counter_0>.

The following registers are absorbed into counter <counter_1>: 1 register on signal <counter_1>.

The following registers are absorbed into counter <counter_2>: 1 register on signal <counter_2>.

Unit <router_sync> synthesized (advanced).

Advanced HDL Synthesis Report

Macro Statistics

# Adders/Subtractors

: 3

6-bit addsub

: 3

# Counters

: 9

5-bit up counter

: 9

# Registers

: 527

Flip-Flops

: 527

# Comparators

: 10

5-bit comparator equal

: 6

6-bit comparator greater

: 3

8-bit comparator not equal

: 1

: 477

# Multiplexers

1-bit 16-to-1 multiplexer

1-bit 2-to-1 multiplexer

1-bit 4-to-1 multiplexer

3-bit 4-to-1 multiplexer

6-bit 16-to-1 multiplexer

: 3

6-bit 2-to-1 multiplexer

: 3

8-bit 2-to-1 multiplexer

: 2

# FSMs

: 1

# Xors

: 2

8-bit xor2

router_sync.v 🗵 📋 router_reg.v 🗵 📋 router_ffo.v 🗵 📋 router_top_tb.v 🗵 📋 router_fsm.v

```

Figure 4.11 – Advanced HDL Synthesis Report

**Figure 4.12** – Design Summary

| 4.5 Tools Used:                                                    |    |  |  |  |  |

|--------------------------------------------------------------------|----|--|--|--|--|

| • Xilinx ISE (Integrated Synthesis Environment) 14.7 Design Suite. |    |  |  |  |  |

|                                                                    |    |  |  |  |  |

|                                                                    |    |  |  |  |  |

|                                                                    |    |  |  |  |  |

|                                                                    |    |  |  |  |  |

|                                                                    |    |  |  |  |  |

|                                                                    |    |  |  |  |  |

|                                                                    |    |  |  |  |  |

|                                                                    |    |  |  |  |  |

|                                                                    |    |  |  |  |  |

|                                                                    |    |  |  |  |  |

|                                                                    |    |  |  |  |  |

|                                                                    |    |  |  |  |  |

|                                                                    |    |  |  |  |  |

|                                                                    |    |  |  |  |  |

|                                                                    |    |  |  |  |  |

|                                                                    |    |  |  |  |  |

|                                                                    |    |  |  |  |  |

|                                                                    |    |  |  |  |  |

|                                                                    |    |  |  |  |  |

|                                                                    | 25 |  |  |  |  |

|                                                                    | 35 |  |  |  |  |

# **Chapter 5**

# **Conclusion**

- The Router 1X3 is implemented and verified successfully. During the design part we came across many coding errors and successfully got rid of those errors.

- During verification we try to incorporate every scenario packets with payload length-

- > 8, 16, 14, 17 bytes.

- ➤ Random byte

- · Other scenarios like-

- > Destination network busy

- ➤ Bad/corrupt packet

- These packet lengths were derived from the testbench in order to assess the design's robustness. All the scenarios were considered, inputs were driven through testbench and the Router was able to perform under all conditions successfully.

# **References**

- [1]. Palnitkar, Samir. Verilog HDL: a guide to digital design and synthesis. Pearson Education India, 2003.

- [2]. Spear, Chris. System Verilog for verification: a guide to learning the testbench language features. Springer Science & Business Media, 2008.

- [3]. Arnab Banerjee, Pascal T. Wolkotte, Robert D. Mullins, Simon W. Moore and Gerard J. M. Smit, "An Energy and Performance Exploration of Network-on-Chip Architectures", IEEE Transactions on Very Large Scale Integration Systems, Vol. 17, No. 3, pp. 319-329, 2009.

- [4]. Cota, E., de Morais Amory, A., & Lubaszewski, M. S. (2012). NoC Basics. In Reliability, Availability and Serviceability of Networks-on-Chip (pp.11-24). Springer US.

- [5]. Swapna, S., Swain, A. K., & Mahapatra, K. K. (2012, December). Design and analysis of f5 port router for network on chip. In Microelectronics and Electronics (PrimeA\$ia), 2012 Asia Pacific Conference on Postgraduate Research in (pp. 51-55). IEEE.

- [6]. Choudhari, E. M., & Dakhole, P. K. (2014, April). Design and verification of five port router for network on chip. In Communications and Signal Processing (ICCSP), 2014 International Conference on (pp. 607-611). IEEE [6] Gopal N., Router 1x3 RTL Design Journal of Engineering.

Similarity Report ID: oid:27535:17723633

## 11% Overall Similarity

Top sources found in the following databases:

- · 10% Internet database

- · Crossref database

- · 7% Submitted Works database

- · 4% Publications database

- · Crossref Posted Content database

#### TOP SOURCES

The sources with the highest number of matches within the submission. Overlapping sources will not be displayed.

| docplayer.net<br>Internet                |                                     | 5%           |

|------------------------------------------|-------------------------------------|--------------|

| irjmets.com                              |                                     | <1%          |

| Internet                                 |                                     | 170          |

| electronicstopper.blogspot.c             | com                                 | <1%          |

| Internet                                 |                                     | <176         |

| Texas A & M University, King             | gville on 2018-11-14                | -10          |

| Submitted works                          |                                     | <1%          |

| Aki Vamsi Krishna, E. Prabho<br>Crossref | u. "Chapter 2 Hardware Trojan Detec | ction at <1% |

| doczz.net                                |                                     | <1%          |

| Internet                                 |                                     | ×17          |

| Higher Education Commission              | on Pakistan on 2016-06-21           | .10          |

| Submitted works                          |                                     | <1%          |

| docplayer.nl                             |                                     | -10          |

| Internet                                 | 1 sh esh                            | <1%          |

|                                          | foresh                              |              |

| 9        | South Thames College on 2017-02-24 Submitted works                             | <1% |

|----------|--------------------------------------------------------------------------------|-----|

| 10       | doi.nrct.go.th Internet                                                        | <1% |

| •        | Visvesvaraya National Institute of Technology on 2020-12-22 Submitted works    | <1% |

| 12       | Swansea Metropolitan University on 2012-03-07 Submitted works                  | <1% |

| 13       | Bridgepoint Education on 2021-11-08 Submitted works                            | <1% |

| 14       | K. R. Kashwan, G. Selvaraj. "Implementation and performance analyses  Crossref | <1% |

| 15       | Sharp, D "Component based product line development of avionics sof  Crossref   | <1% |

|          |                                                                                |     |

| 16       | lib.dr.iastate.edu Internet                                                    | <1% |

| 16<br>17 |                                                                                | <1% |