### Implementation of Analog Signal Processing/Generation Circuits Using Modern Active Building Blocks

A Thesis Submitted to the Delhi Technological University for the award of Doctor of Philosophy

in Department of Electrical Engineering

by

**Ajishek Raj** (2K16/Ph.D/EE/09)

Under the Supervision of Prof. Pragati Kumar & Prof. Data Ram Bhaskar

Department of Electrical Engineering Delhi Technological University Delhi-110042, India

DELHI TECHNOLOGICAL UNIVERSITY

ALL RIGHTS RESERVED

July 2021

### Certificate

This is to certify that the thesis entitled "Implementation of Analog Signal Processing/Generation Circuits Using Modern Active Building Blocks" being submitted by Mr. Ajishek Raj (2K16/Ph.D/EE/09) for the award of degree of Doctor of Philosophy in the Department of Electrical Engineering, Delhi Technological University, Delhi, is the record of students own work carried out by him under our supervision. The contents of this research work have not been submitted in part or fully to any other institute or university for the award of any degree.

**Date**: 26 July 2021

Prof. Pragati Kumar

Bongoh. lunar

Department of Electrical Engineering Delhi Technological University

Delhi-110042, India

Bhaskar

Prof. Data Ram Bhaskar

Department of Electrical Engineering

Delhi Technological University

Delhi-110042, India

### Acknowledgment

I take this opportunity to express my significant indebtedness, most profound sense of gratitude and heartiest thanks to my supervisors **Prof. Pragati Kumar** and **Prof. D. R. Bhaskar**, who kindly accepted to take me as Ph. D student and supported me with warm encouragement, patient guidance and fruitful discussions during the entire course of the research work. Their humane and warm personal approaches in all aspects, have given me the strength to carry out this research work on a steady and smooth course. I humbly acknowledge life time gratitude to them.

I would like to express my thanks to **Prof. Uma Nangia**, HOD (EE) for her kind support.

I would like to express my sincere thanks to **Prof. Raj Senani**, NSUT-Delhi and **Prof. Madhusudan Singh**, EED, DTU-Delhi, for their kind support, helpful advice and constructive suggestions.

More personally, I would like to express my sincere thanks to **Dr. Ram Bhagat**, EED, DTU-Delhi, who encouraged me for further education after my M. Tech course. I would also like to thank to **Dr. Alok Kumar Singh**, ECED, DTU-Delhi, **Mrs. Garima**, EED, DTU, Delhi, **Dr. Manoj Kumar**, GBPIET, Pauri (Uttakhand) for rendering valuable help throughout the present work. I am also thankful to my senior **Mr. Hemant Kumar Tiwari**, who always used to put "Dr" suffix before my name before completion of my degree.

I am also grateful to my beloved brother and roompartner Mr. Prabhay who was always with me during my Ph.D. course and tolerated me.

Also, I would like to extend my thanks to Mr. Upendra Kumar, Mr. Jagvir

Singh, Mr. Anil Butola and Mr. Abhishek for providing and arranging all necessary help in LIC Lab for carrying out experimental work.

Without seniors and friends like Deepak Kumar Mahto, Alka, Gurumurthy Sir, Ambrish Sir, Hemant Saxena, Suryakant, Manideep Ranjan, Anisha (Bhabhi Ji), Kamakshi it would have become very difficult to cope-up with the ups and downs faced during the last five years. I am grateful to them for providing me with moral support during the entire course of my research work.

Finally, I would never forget the deepest concern of my grand father Shri Narayan Sah, my father Shri Vijay Shankar Prasad and my mother Smt. Sheela Devi, who had believed in me, my brother Abhishek Raj, sister Pallawi, brother-in-law Mr. Rupesh Kumar and all my family members for their everlasting love and care showered on me during the entire journey of my Ph.D research work.

Last, but not the least, I thank Mother Nature and God Almighty for providing me the opportunity for pursuing doctoral studies.

AJISHEK RAJ

(2K16/PHD/EE/09)

34ishek Ray 2

## Contents

| C) | ertin | cate   |                                                          | 1    |

|----|-------|--------|----------------------------------------------------------|------|

| A  | ckno  | wledgn | nent                                                     | ii   |

| Li | st of | Table  | S                                                        | xix  |

| Li | st of | Symb   | ols                                                      | хх   |

| Li | st of | Abbre  | eviations x                                              | xii  |

| Li | st of | Public | cations                                                  | xiii |

| 1  | Intr  | oducti | ion                                                      | 1    |

|    |       | 1.0.1  | Operational Transconductance Amplifier                   | 3    |

|    |       |        | 1.0.1.1 Bipolar Implementation of OTA                    | 5    |

|    |       |        | 1.0.1.2 CMOS Implementation of OTA                       | 7    |

|    |       |        | 1.0.1.3 DC and Frequency Characteristics of an OTA       | 8    |

|    |       | 1.0.2  | Current Feedback Operational Amplifier                   | 10   |

|    | 1.1   | Resear | rch Objectives                                           | 13   |

|    | 1.2   | Organ  | isation of Thesis                                        | 14   |

| 2  | Vol   | tage N | Iode and Mixed Mode Filter Structures Using OTAs         | 37   |

|    | 2.1   | Introd | luction                                                  | 37   |

|    |       | 2.1.1  | MISO Type Mixed Mode Active Analog Filters Realized with |      |

|    |       |        | ABBs Other than OTAs                                     | 38   |

|   |     | 2.1.2  | MISO type VM and Mixed Mode Analog Active Filters Real-             |

|---|-----|--------|---------------------------------------------------------------------|

|   |     |        | ized with OTAs                                                      |

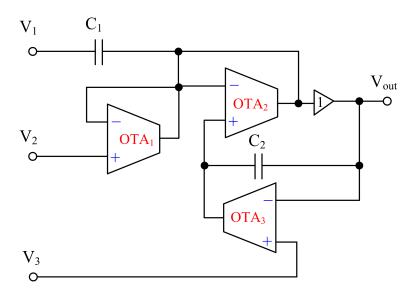

|   | 2.2 | VM U   | niversal Biquad Filter Employing Five OTAs 51                       |

|   |     | 2.2.1  | Sensitivity Analysis                                                |

|   |     | 2.2.2  | Simulation Results                                                  |

|   |     | 2.2.3  | Tuning of $\omega_0$ and $BW$                                       |

|   | 2.3 | VM U   | Iniversal Biquad Filters using Four OTAs                            |

|   |     | 2.3.1  | Sensitivity Analysis                                                |

|   |     | 2.3.2  | Simulation Results                                                  |

|   |     | 2.3.3  | Monte-Carlo Simulations                                             |

|   |     | 2.3.4  | Noise Analysis                                                      |

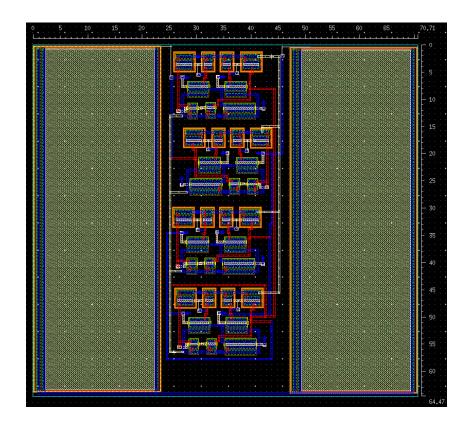

|   |     | 2.3.5  | Layout Design of the Proposed Biquad Filter Circuit of Fig. 2.14 64 |

|   | 2.4 | Mixed  | Mode Universal Biquad Filter Employing Five OTAs and Two            |

|   |     | Groun  | ded Capacitors                                                      |

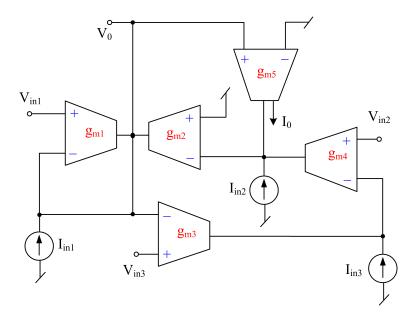

|   |     | 2.4.1  | Proposed Mixed Mode Filter Configuration                            |

|   |     |        | 2.4.1.1 Sensitivity Analysis                                        |

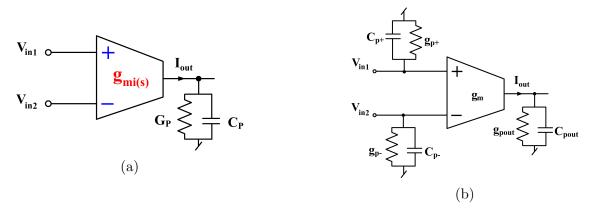

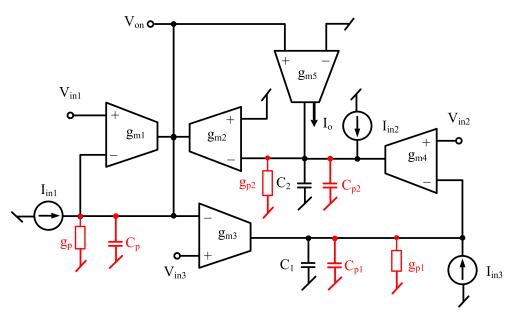

|   |     | 2.4.2  | Non-Ideal Analysis                                                  |

|   |     | 2.4.3  | Simulation Results and Layout Design                                |

|   |     |        | 2.4.3.1 Simulation Results                                          |

|   |     |        | 2.4.3.2 Noise Performance Analysis 79                               |

|   |     |        | 2.4.3.3 Layout Design                                               |

|   | 2.5 | Concl  | uding Remarks                                                       |

| 3 | Thi | rd Ord | ler Quadrature Sinusoidal Oscillators Using OTAs 93                 |

|   | 3.1 |        | luction                                                             |

|   | 3.2 |        | CM Third Order Quadrature Sinusoidal Oscillator Configura-          |

|   |     | ,      | Employing Three OTAs and Three Capacitors                           |

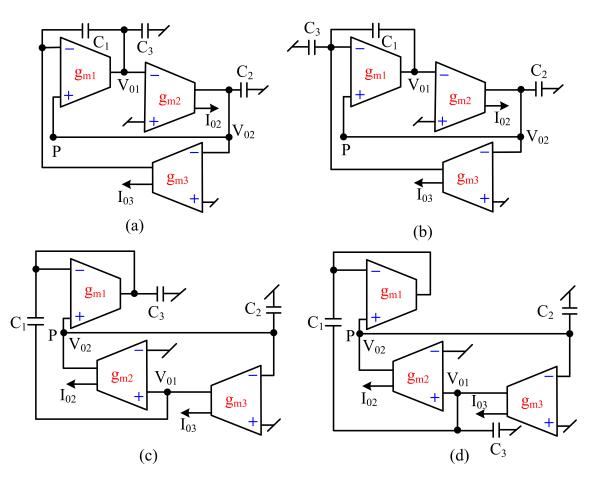

|   |     | 3.2.1  | Proposed Circuits                                                   |

|   |     | 3.2.2  | Non-Ideal Analysis                                                  |

|   |     | 3.2.3  | Phase Noise and Frequency Stability                                 |

|   |     | -      |                                                                     |

|   |     | 3.2.4  | Simulati  | on Results                                            | 108 |

|---|-----|--------|-----------|-------------------------------------------------------|-----|

|   |     | 3.2.5  | Experim   | nental Results                                        | 112 |

|   | 3.3 | Third  | -Order Qu | nadrature Sinusoidal Oscillators Using four OTAs and  |     |

|   |     | Groun  | ided Capa | acitors                                               | 117 |

|   |     | 3.3.1  | TOQSO     | Circuits with Grounded Capacitors                     | 118 |

|   |     | 3.3.2  | Non-Ide   | al Analysis of Proposed TOQSO Structures              | 121 |

|   |     | 3.3.3  | Frequence | cy Stability                                          | 123 |

|   |     | 3.3.4  | Simulati  | on Results                                            | 123 |

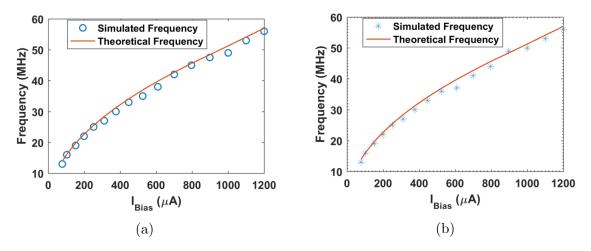

|   |     |        | 3.3.4.1   | Tunability of FO with bias currents                   | 125 |

|   |     | 3.3.5  | Experim   | nental Results                                        | 129 |

|   | 3.4 | Concl  | uding Rer | narks                                                 | 135 |

| 4 | Th: | nd One | lon Cinuc | soidal Oscillators Using CFOAs                        | 143 |

| 4 |     |        |           | G                                                     |     |

|   | 4.1 |        |           |                                                       |     |

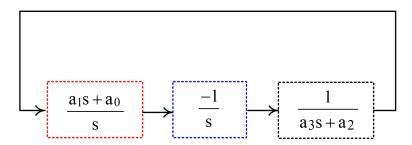

|   | 4.2 |        |           | aches for the Design of TOSOs                         | 143 |

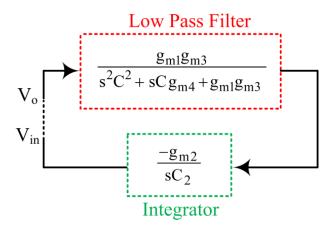

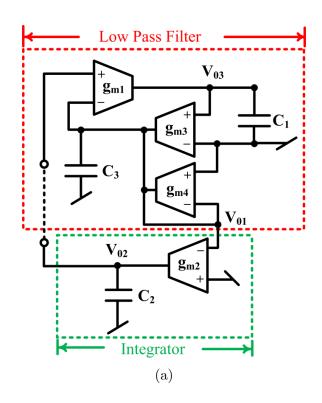

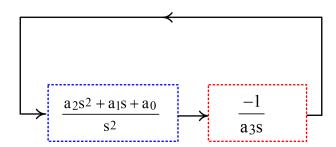

|   |     | 4.2.1  |           | based on Second Order Lowpass Filter and Lossless     |     |

|   |     |        |           | or                                                    | 144 |

|   |     | 4.2.2  | TOSOs     | based on Second Order Highpass Filter and Lossless    |     |

|   |     |        | Different | tiator                                                | 145 |

|   |     | 4.2.3  | Combina   | ation of Two Lossy Integrators and One Lossless In-   |     |

|   |     |        | tegrator  |                                                       | 146 |

|   |     | 4.2.4  | Combina   | ation of Two Lossless Integrators and One Lossy In-   |     |

|   |     |        | tegrator  | based TOSOs                                           | 147 |

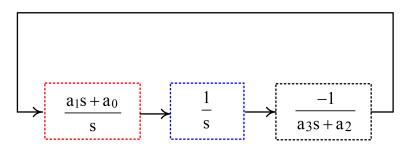

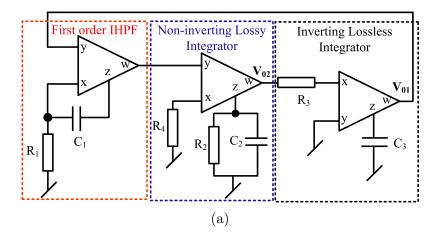

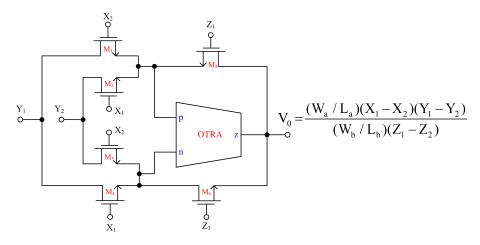

|   | 4.3 | Propo  | sed Appro | oaches Using Inverse Filters for the Design of TOQSOs | 149 |

|   |     | 4.3.1  | First Or  | der Inverse Highpass Filter, One lossy Integrator and |     |

|   |     |        | One Los   | sless Integrator based Realization                    | 149 |

|   |     |        | 4.3.1.1   | Exemplary Implementation of Third-Order Quadra-       |     |

|   |     |        |           | ture Sinusoidal Oscillators Using first order IHPF    |     |

|   |     |        |           | Approach                                              | 150 |

|   |     |        | 4312      | Non-Ideal Analysis                                    | 152 |

|   |     |        | 4.3.1.3          | Experimental Results                                              |

|---|-----|--------|------------------|-------------------------------------------------------------------|

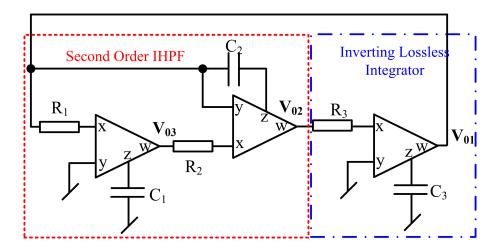

|   |     | 4.3.2  | Second (         | Order Inverse Highpass Filter and Lossless Integrator             |

|   |     |        | based Ap         | pproach                                                           |

|   |     |        | 4.3.2.1          | Exemplary Implementation of TOQSO Using second                    |

|   |     |        |                  | order IHPF Approach                                               |

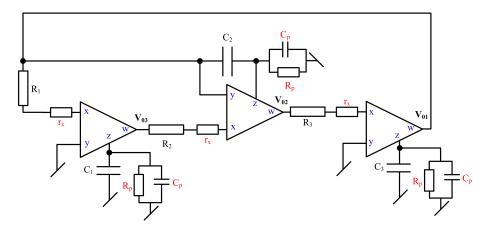

|   |     |        | 4.3.2.2          | Non-Ideal Analysis of the Oscillator Circuit presented            |

|   |     |        |                  | in Fig. 4.12                                                      |

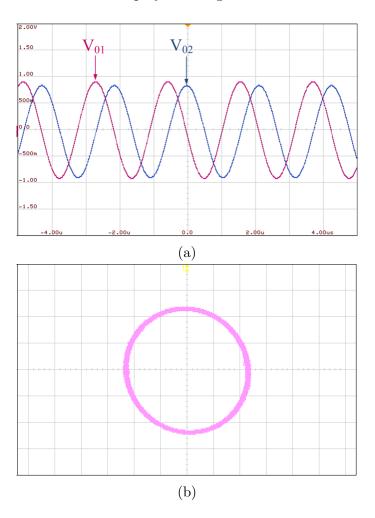

|   |     |        | 4.3.2.3          | Experimental Results                                              |

|   | 4.4 | Low F  | requency         | Third Order Sinusoidal Oscillators with Grounded                  |

|   |     | Capac  | itors            |                                                                   |

|   |     | 4.4.1  | Design o         | f Low Frequency Third Order Sinusoidal Oscillators . 161          |

|   |     | 4.4.2  | Low Free         | quency Oscillators With Independent Control of CO                 |

|   |     |        | and FO           | Using CFOAs                                                       |

|   |     | 4.4.3  | Effect of        | Non-Idealities on LF Oscillators                                  |

|   |     |        | 4.4.3.1          | Sensitivity Analysis                                              |

|   |     |        | 4.4.3.2          | Frequency Stability                                               |

|   |     | 4.4.4  | Experim          | ental Results                                                     |

|   |     |        | 4.4.4.1          | Sensitivity of FO with Power Supply Voltages 173                  |

|   |     |        | 4.4.4.2          | Tunability of FO of Proposed LF Oscillators 174                   |

|   |     |        | 4.4.4.3          | Amplitude Limitation Mechanism of the Proposed                    |

|   |     |        |                  | LF Oscillators                                                    |

|   | 4.5 | Conclu | ıding Ren        | narks                                                             |

| 5 | Nor | -Linea | ır Analog        | g Circuits Using OTA and CFOA 180                                 |

| • | 5.1 |        |                  |                                                                   |

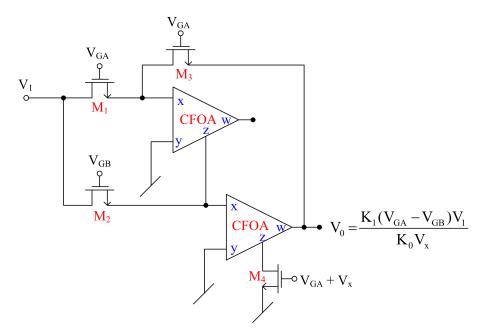

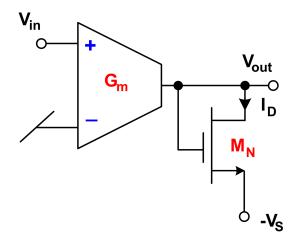

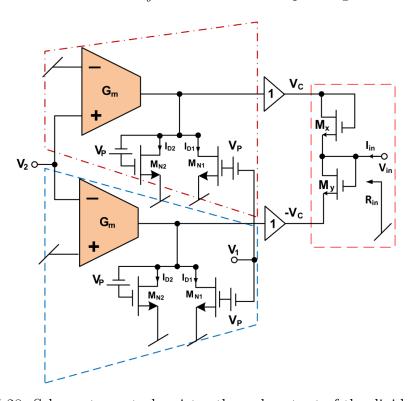

|   | 5.2 |        |                  | g Divider Circuit Using OTA                                       |

|   |     | 5.2.1  |                  | h Analysis                                                        |

|   |     | 0.2.1  | 5.2.1.1          | Mismatch Between Threshold Voltages of $M_{N1}$ and               |

|   |     |        | J. <b>2</b> .1.1 | $M_{N2}$                                                          |

|   |     |        | 5.2.1.2          | Mismatch Between the Aspect Ratios of $M_{N_1}$ and $M_{N_2}$ 191 |

|   |     |        | 0.2.1.2          | This induction of the poor reading of mal may 191                 |

|     | 5.2.2  | Effect of Variation in the Supply Voltage on $V_P$               |

|-----|--------|------------------------------------------------------------------|

|     | 5.2.3  | High-Frequency Response of Divider Circuit                       |

| 5.3 | Invers | e Function                                                       |

| 5.4 | Simula | ation Results of Divider and Inverse Functions                   |

|     | 5.4.1  | Voltage Division Mode                                            |

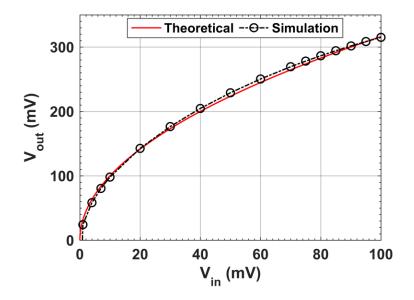

|     |        | 5.4.1.1 DC Characteristics                                       |

|     |        | 5.4.1.2 Frequency and Transient Responses 197                    |

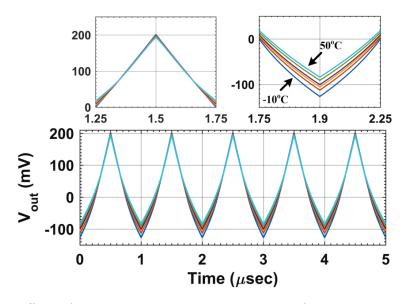

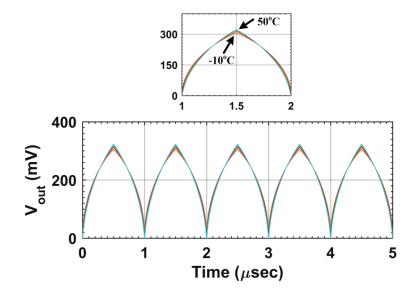

|     |        | 5.4.1.3 Temperature Analysis                                     |

|     | 5.4.2  | Inverse Function Generation Mode                                 |

| 5.5 | Analo  | g Square Root Circuit using OTA                                  |

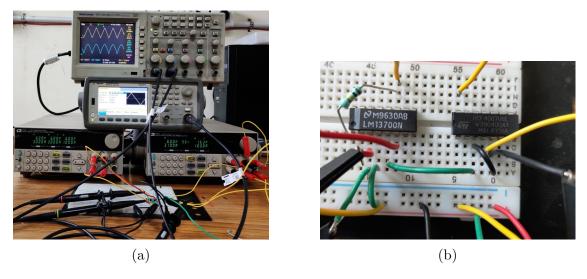

|     | 5.5.1  | Simulation and Experimental Results of Square-Root Circuit . 203 |

|     |        | 5.5.1.1 DC Characteristics                                       |

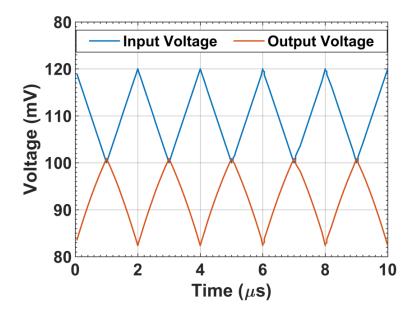

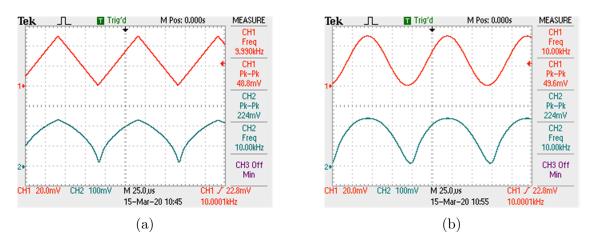

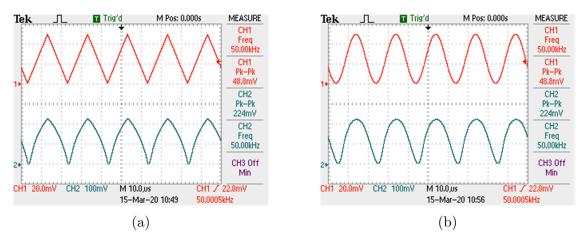

|     |        | 5.5.1.2 Frequency and Transient Responses 204                    |

|     |        | 5.5.1.3 Temperature Analysis                                     |

|     |        | 5.5.1.4 Experimental Results                                     |

| 5.6 | Applio | cation Examples                                                  |

|     | 5.6.1  | Use of Divider Circuit to Linearize Transducer Output 208        |

|     | 5.6.2  | Linear Voltage Controlled Resistor Using Analog Divider Cir-     |

|     |        | cuits                                                            |

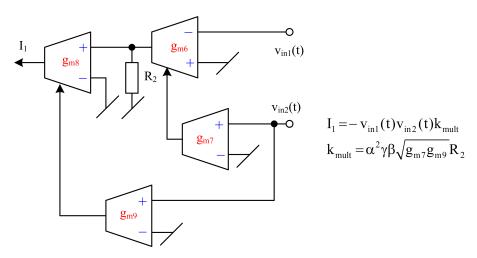

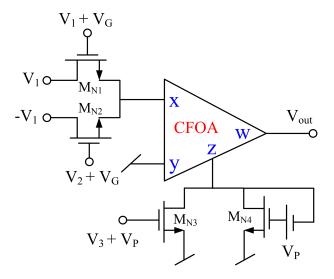

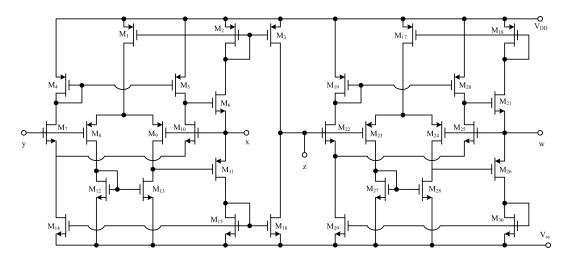

| 5.7 | Multip | olier and Divider Circuit Using a Single CFOA                    |

|     | 5.7.1  | Non-Linear Analog Multiplier and Divider Circuit Using a Sin-    |

|     |        | gle CFOA                                                         |

|     |        | 5.7.1.1 Mismatch Analysis between Threshold Voltages of          |

|     |        | MOSFETs                                                          |

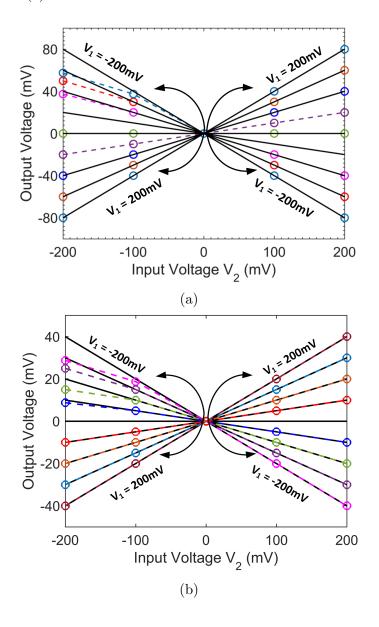

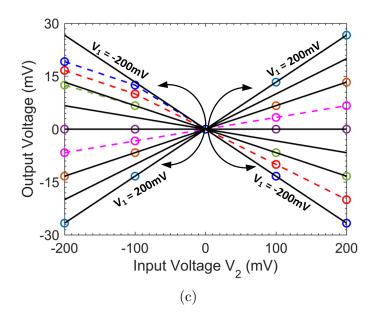

|     | 5.7.2  | Simulation Results                                               |

|     |        | 5.7.2.1 Voltage Multiplication Mode                              |

|     |        | 5.7.2.2 Application Examples of Multiplier Circuit 215           |

|     |        | 5.7.2.3 Voltage Divider Mode                                     |

| 5.8 | Concl  | uding Remarks 224                                                |

| 6 | Conclusions and Future scope |              |     |  |  |  |  |

|---|------------------------------|--------------|-----|--|--|--|--|

|   | 6.1                          | Conclusions  | 233 |  |  |  |  |

|   | 6.2                          | Future Scope | 237 |  |  |  |  |

# List of Figures

| 1.1  | Bipolar implementation of one OTA used in LM13600/LM13700 [175]           | 6  |

|------|---------------------------------------------------------------------------|----|

| 1.2  | Pin diagram of LM13600/LM13700 [175]                                      | 7  |

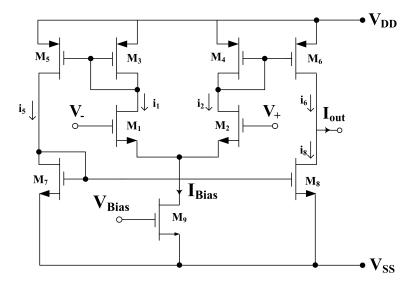

| 1.3  | CMOS implementation of OTA [177]                                          | 7  |

| 1.4  | DC transfer characteristics of (a) Bipolar OTA (b) CMOS OTA $\ . \ . \ .$ | 9  |

| 1.5  | Frequency responses of (a) Bipolar OTA (b) CMOS OTA                       | 9  |

| 1.6  | Schematic of the CFOA AD844 [174]                                         | 11 |

| 1.7  | Pin diagram of AD844 [178]                                                | 11 |

| 1.8  | Symbolic representation of CFOA                                           | 12 |

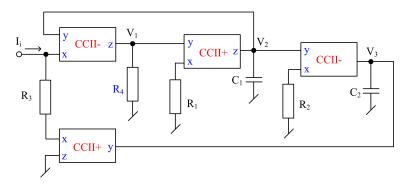

| 2.1  | Mixed mode biquad circuit reported by Soliman [22]                        | 39 |

| 2.2  | Filter configuration reported by Lee and Chang [34]                       | 41 |

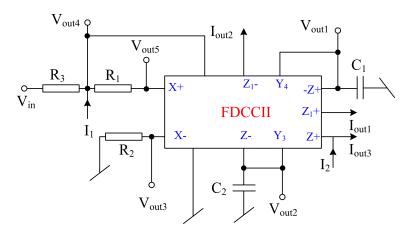

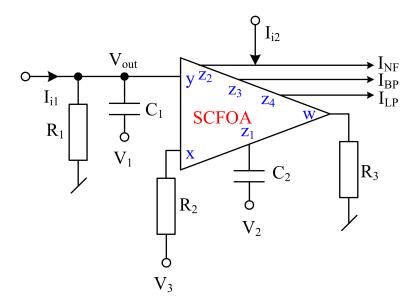

| 2.3  | SCFOA based mixed mode filter circuit proposed by Yuce [39]               | 43 |

| 2.4  | Universal biquad filter circuit using OTAs reported by Khan, Ahmed        |    |

|      | and Minhaj [47]                                                           | 44 |

| 2.5  | Universal biquad filter structure reported by Psychalinos, Kasimis        |    |

|      | and Khateb [51]                                                           | 46 |

| 2.6  | OTA-C filter configuration reported by Bhaskar, Singh, Sharma and         |    |

|      | Senani [54]                                                               | 46 |

| 2.7  | Mixed mode biquad filter circuit using OTAs reported by Chen, Liao        |    |

|      | and Lee [62]                                                              | 48 |

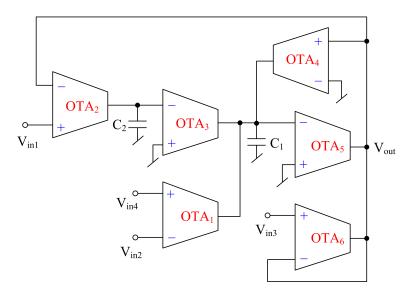

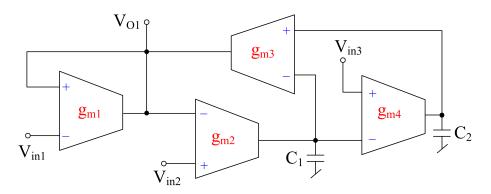

| 2.8  | First proposed configuration of VM biquad filter                          | 51 |

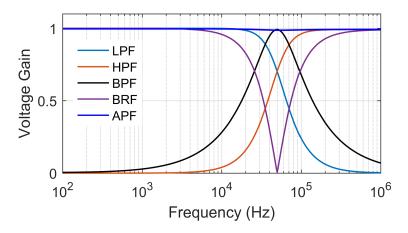

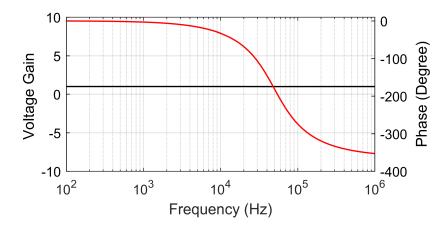

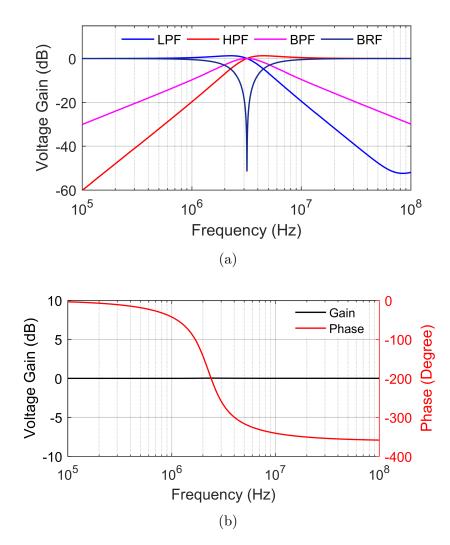

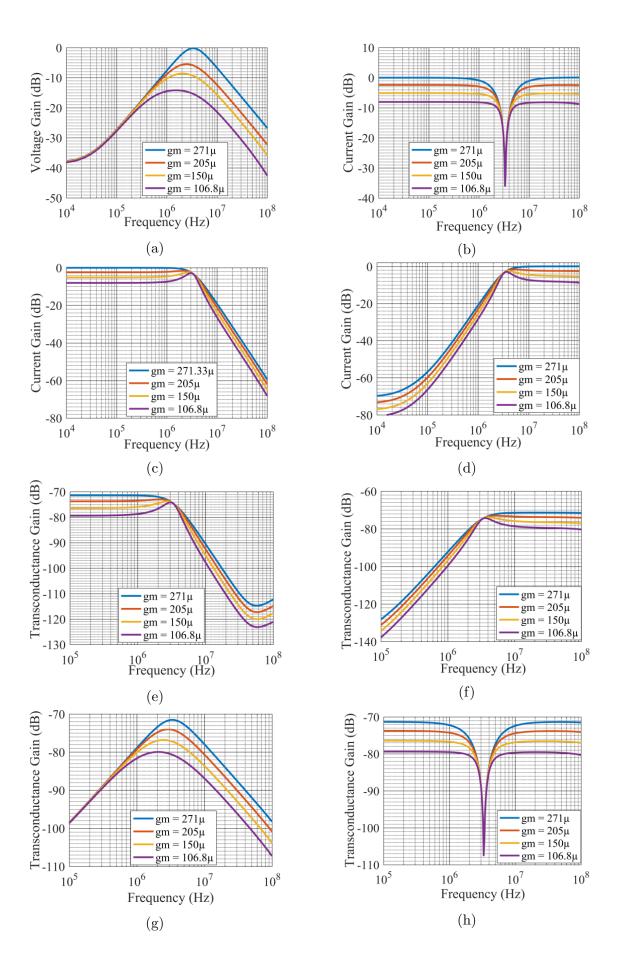

| 2.9  | Frequency responses of filters of Fig. 2.8                                | 54 |

| 2.10 | Phase responses of APF of Fig. 2.8                                        | 54 |

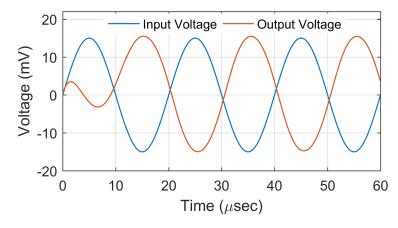

| 2.11 | Input and output transient responses of APF of Fig. 2.8                           | 54 |

|------|-----------------------------------------------------------------------------------|----|

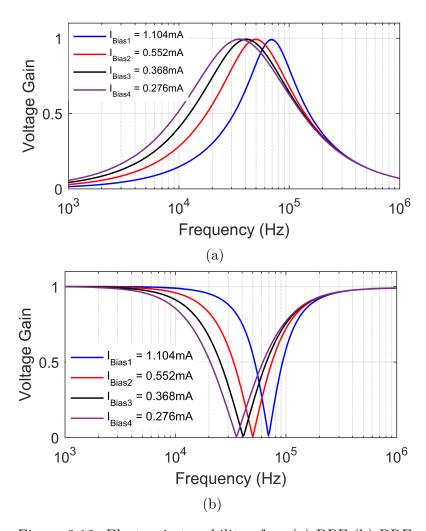

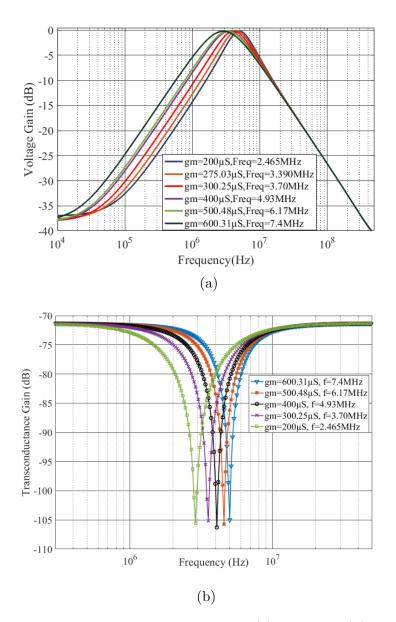

| 2.12 | Electronic tunability of $\omega_0$ (a) BPF (b) BRF                               | 55 |

| 2.13 | Four OTA-based first VM biquad filter structure                                   | 56 |

| 2.14 | Second four OTA-based VM biquad filter topology                                   | 58 |

| 2.15 | Exemplary CMOS implementation of OTA [74]                                         | 60 |

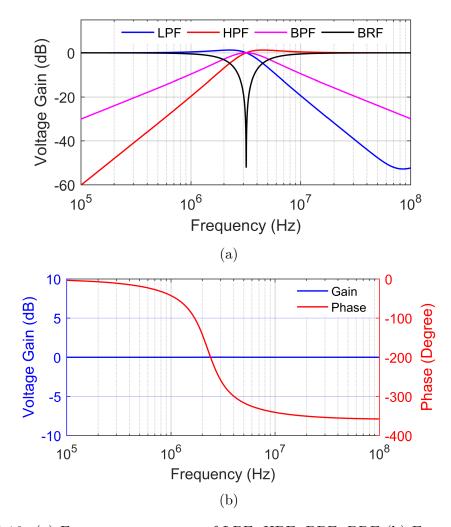

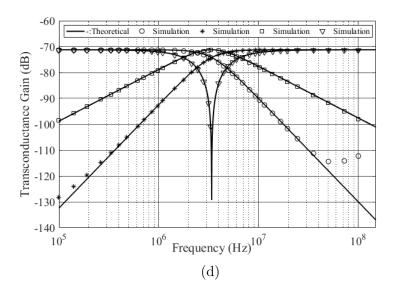

| 2.16 | (a) Frequency responses of LPF, HPF, BPF, BRF (b) Frequency and                   |    |

|      | phase responses of APF of Fig. 2.13                                               | 61 |

| 2.17 | (a) Frequency responses of LPF, HPF, BPF, BRF (b) Frequency and                   |    |

|      | phase responses of APF of Fig. 2.14                                               | 62 |

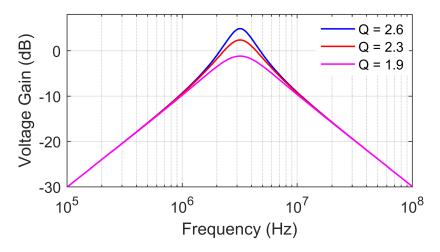

| 2.18 | Tunability of $\omega_1$ with gain and $Q_{01}$ of proposed biquad filter of Fig. |    |

|      | 2.13                                                                              | 62 |

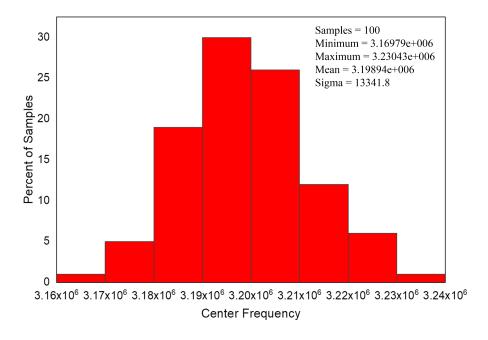

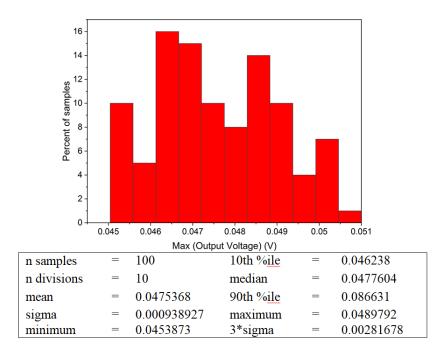

| 2.19 | Monte-Carlo simulation results of BPF of Fig. 2.13                                | 63 |

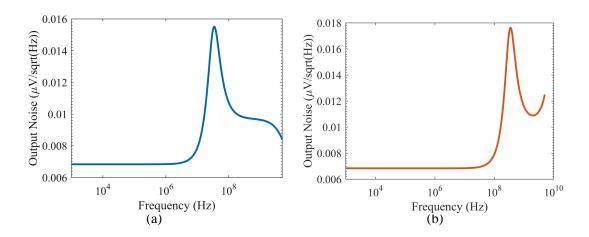

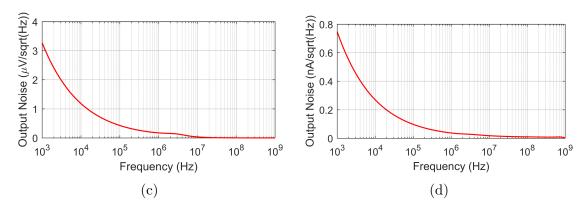

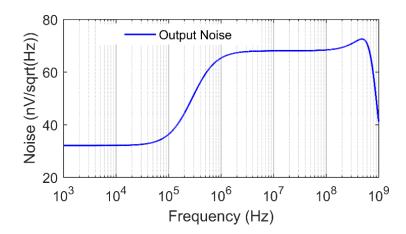

| 2.20 | Simulation results of output noise for (a) Fig 2.13 (b) Fig 2.14 $\dots$          | 64 |

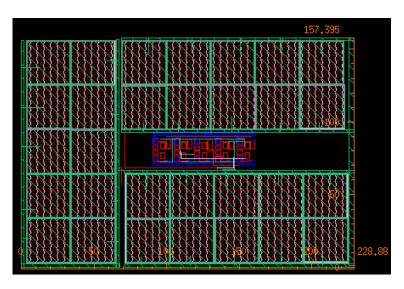

| 2.21 | Layout design of proposed VM filter configuration of Fig. 2.14                    | 65 |

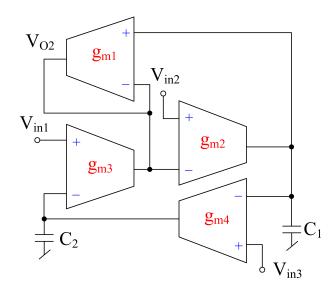

| 2.22 | Proposed mixed mode OTA-C universal biquad filter configuration                   | 66 |

| 2.23 | Non-ideal models of OTA                                                           | 71 |

| 2.24 | Mixed mode filter circuit with parasitic transconductances and ca-                |    |

|      | pacitances                                                                        | 72 |

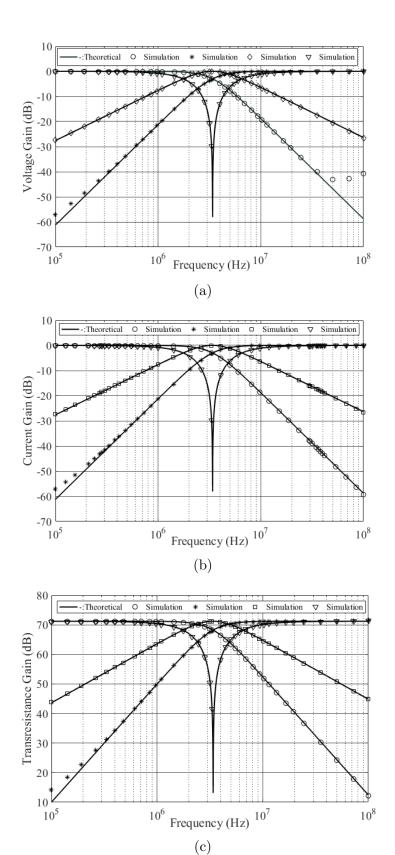

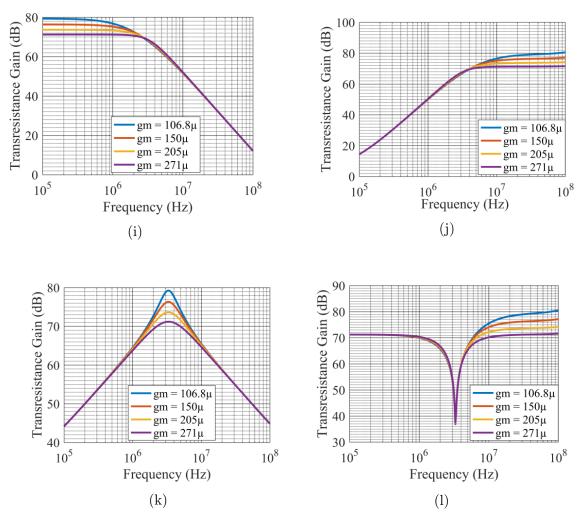

| 2.25 | Frequency responses of (a) VM biquad filter (b) CM biquad filter (c)              |    |

|      | TRM biquad filter (d) TCM biquad filter                                           | 76 |

| 2.26 | Gain and phase responses of APF (a) VM (b) CM (c) TRM (d) TCM                     | 76 |

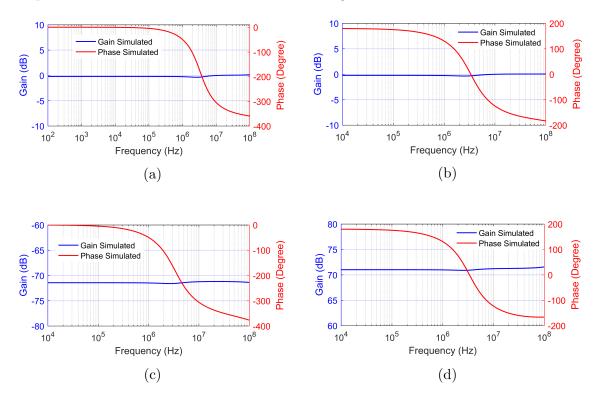

| 2.27 | Variation of gain with transconductance of various filter responses of            |    |

|      | Fig. 2.22                                                                         | 78 |

| 2.28 | Tunability of cut-off frequency for (a) BPF and (b) BRF of Fig. 2.22              | 79 |

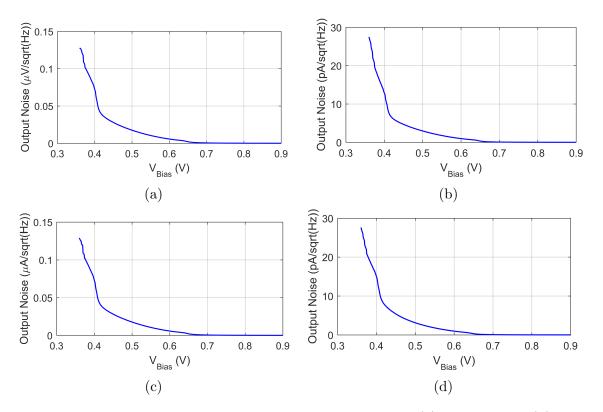

| 2.29 | Output noise simulation results with $V_{Bias}$ (a) VM biquad (b) CM              |    |

|      | biquad (c) TRM Biquad (d) TCM biquad of Fig. 2.22                                 | 80 |

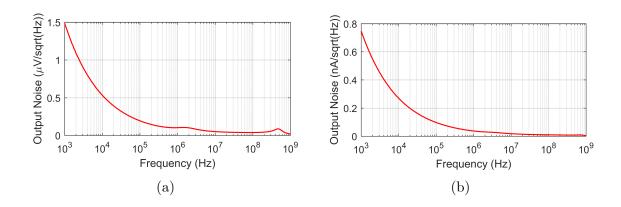

| 2.30 | Output noise simulation results with frequency (a) VM biquad (b)                  |    |

|      | CM biquad (c) TRM Biquad (d) TCM biquad of Fig. 2.22                              | 81 |

| 2.31 | Complete physical layout design of the proposed biquad filter in VM   |

|------|-----------------------------------------------------------------------|

|      | of Fig. 2.22                                                          |

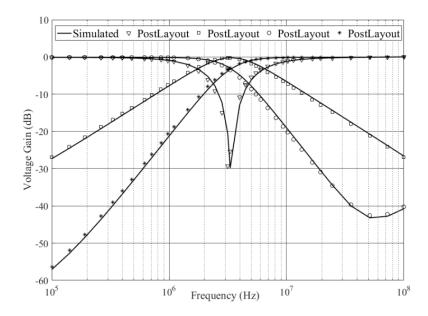

| 2.32 | Pre-layout and post-layout responses of the proposed biquad in VM     |

|      | Fig. 2.22                                                             |

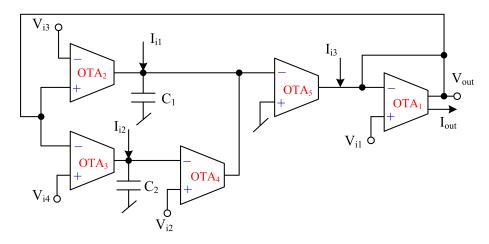

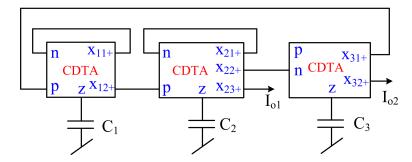

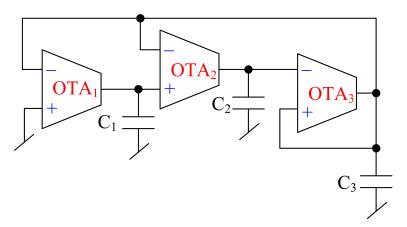

| 3.1  | TOQSO using OTAs reported by Prommee and Dehjan [18] 95               |

| 3.2  | Third-order quadrature sinusoidal oscillator using CDTAs reported     |

|      | by Horng [23]                                                         |

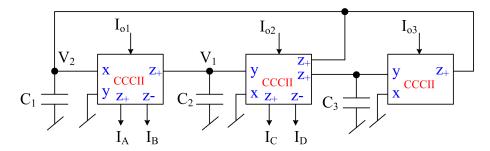

| 3.3  | Third-order sinusoidal oscillators using CCCIIs presented by Mahesh-  |

|      | wari [25]                                                             |

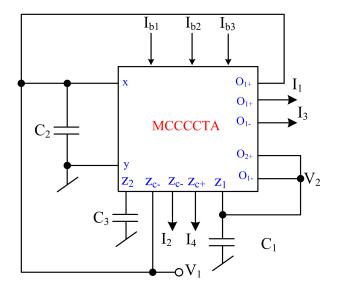

| 3.4  | Third-order quadrature sinusoidal oscillator using MCCCCTAs pre-      |

|      | sented by Kumngern and Chanwutitum [30]                               |

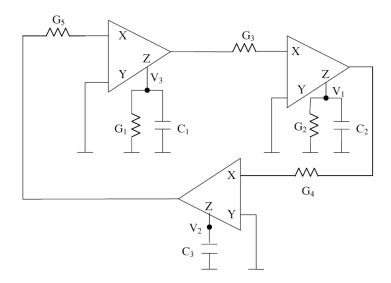

| 3.5  | Third-order sinusoidal oscillators using CFOAs reported by Soliman    |

|      | [34]                                                                  |

| 3.6  | Third-order quadrature sinusoidal oscillator using DVCCTAs pre-       |

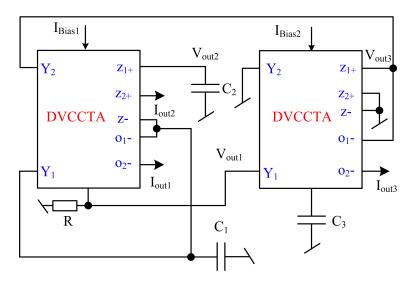

|      | sented by Pandey and Pandey [38]                                      |

| 3.7  | Third-order sinusoidal oscillators using OTAs reported by Komal,      |

|      | Pushkar and Kumar [50]                                                |

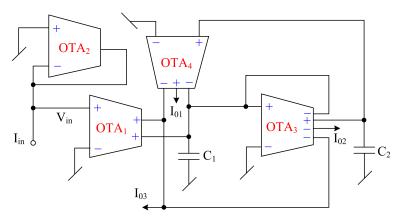

| 3.8  | Proposed third-order quadrature sinusoidal oscillators                |

| 3.9  | Non-ideal model of OTA                                                |

| 3.10 | Exemplary CMOS implementation of OTA[55]                              |

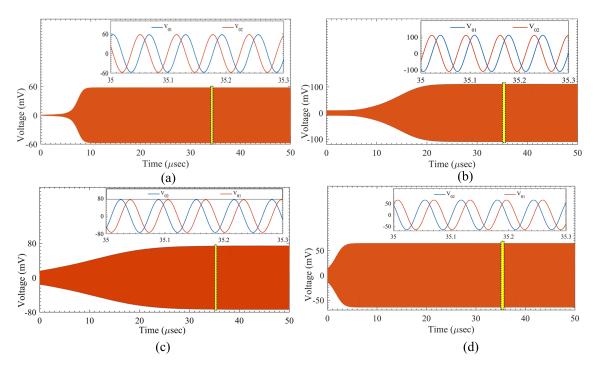

| 3.11 | Simulated transient and steady state responses of the voltages of TO- |

|      | QSOs of Fig. 3.8                                                      |

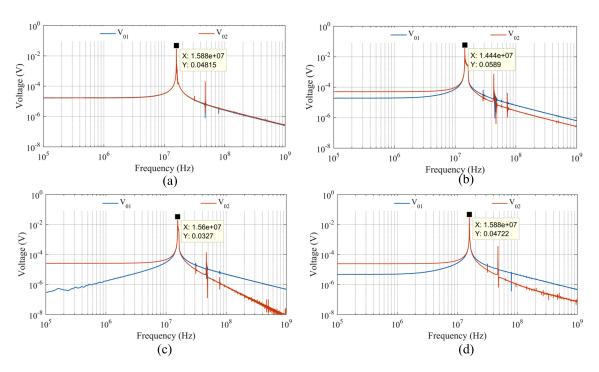

| 3.12 | The simulated spectrum of proposed TOQSOs of Fig. 3.8 110             |

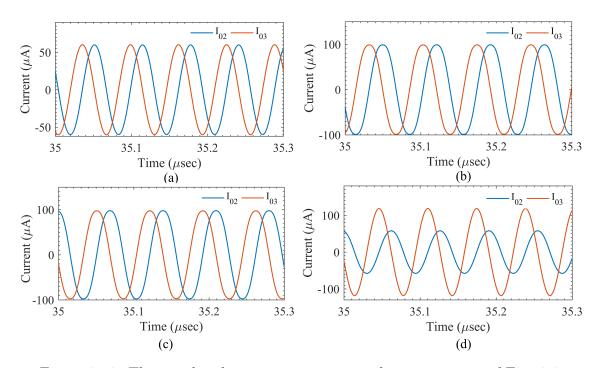

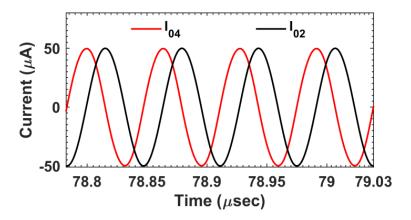

| 3.13 | The simulated transient current quadrature outputs of Fig. 3.8 111    |

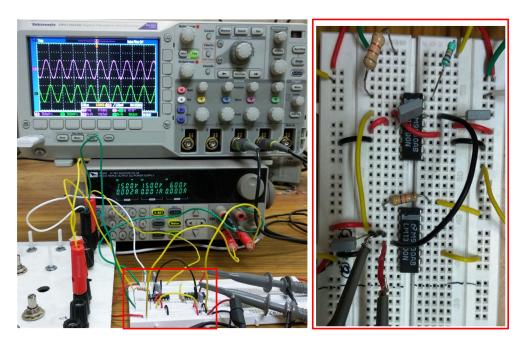

| 3.14 | Experimental setup for TOQSO shown in Fig. 3.8(d)                     |

| 3.15 | The experimental VM quadrature output waveforms and the fre-          |

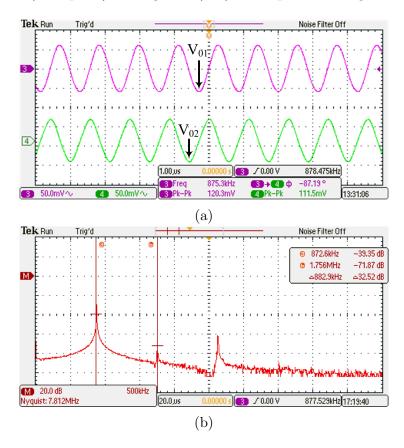

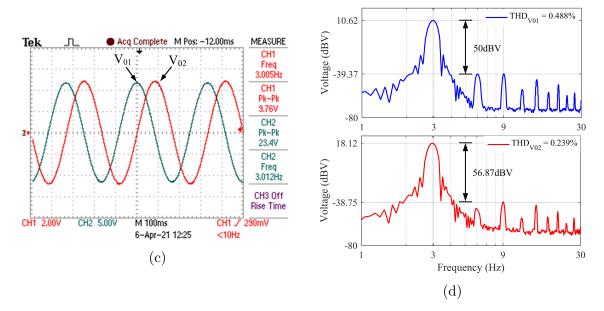

|      | quency spectrum of Fig. 3.8(a)                                        |

| 3.16 | The experimental VM quadrature output waveforms and the fre-          |

|      | quency spectrum of Fig. 3.8(b)                                        |

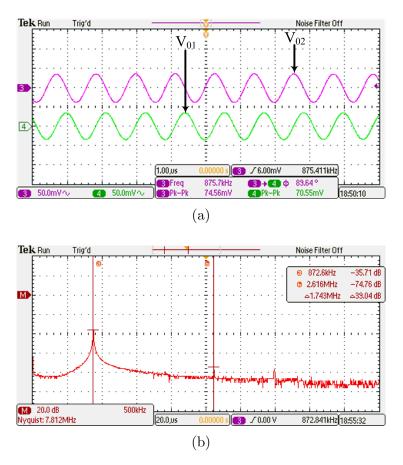

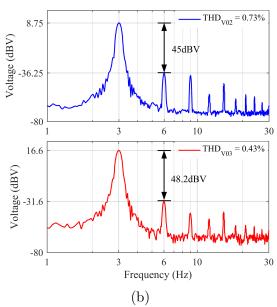

| 3.17 | The experimental VM quadrature output waveforms and the fre-                                    |

|------|-------------------------------------------------------------------------------------------------|

|      | quency spectrum of Fig. 3.8(c)                                                                  |

| 3.18 | The experimental VM quadrature output waveforms and the fre-                                    |

|      | quency spectrum of Fig. 3.8(d)                                                                  |

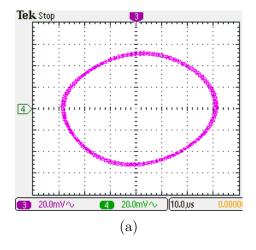

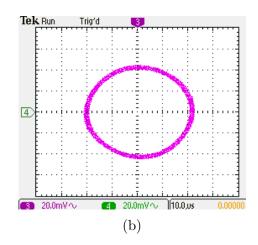

| 3.19 | Lissajous pattern of proposed TOQSOs of Fig. 3.8                                                |

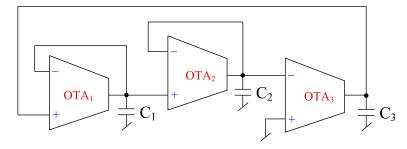

| 3.20 | Functional block diagram used for realizing TOQSO                                               |

| 3.21 | New structures of TOQSOs                                                                        |

| 3.22 | Complete oscillator circuits including parasitic elements of OTAs 121                           |

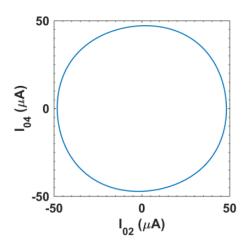

| 3.23 | Simulated steady-state voltage responses of Fig. 3.21a                                          |

| 3.24 | Simulated steady-state voltage responses of Fig. 3.21b                                          |

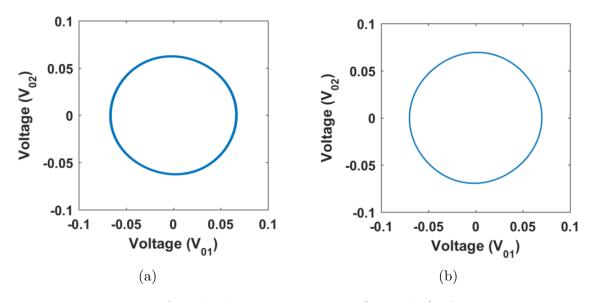

| 3.25 | Simulated Lissajous pattern (X-Y plot) of Fig. 3.21                                             |

| 3.26 | Frequency variation with $I_{Bias}$ for Fig. 3.21                                               |

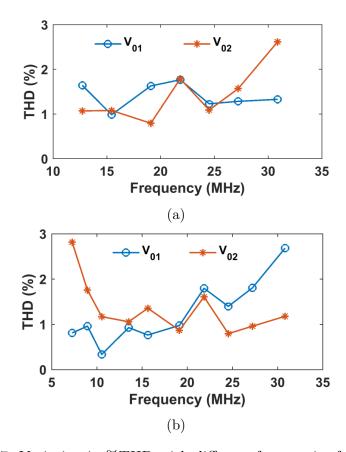

| 3.27 | Variation in %THD with different frequencies for Fig. 3.21 126                                  |

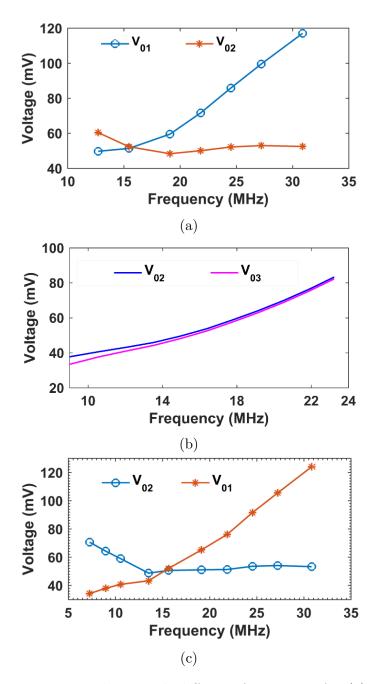

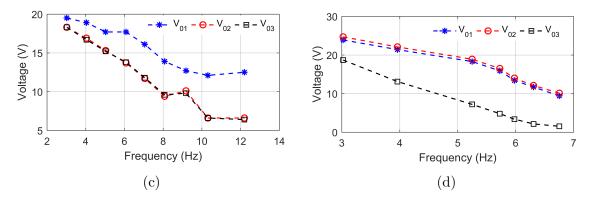

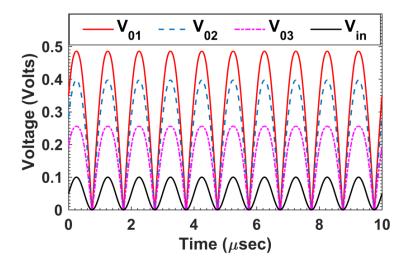

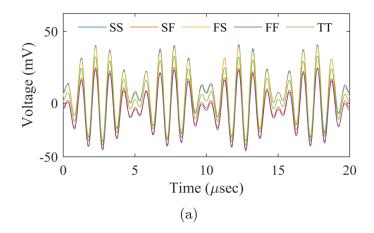

| 3.28 | Variation in voltage with different frequencies for (a) $V_{01}$ and $V_{02}$ of                |

|      | Fig. 3.21a, (b) $V_{02}$ and $V_{03}$ of Fig. 3.21b (c) $V_{01}$ and $V_{02}$ of Fig. 3.21b 127 |

| 3.29 | Simulated steady state quadrature current responses of Fig. $3.21\mathrm{b}$ $128$              |

| 3.30 | Simulated Lissajous pattern (X-Y plot) of Fig. 3.21b                                            |

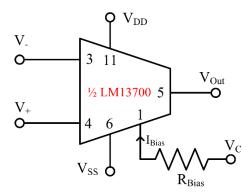

| 3.31 | Pin connection and arrangement for generating $I_{Bias}$                                        |

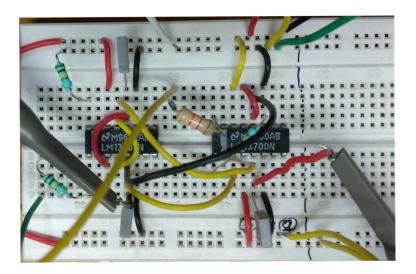

| 3.32 | Experimental setup for TOQSO shown in Fig. 3.21b 129                                            |

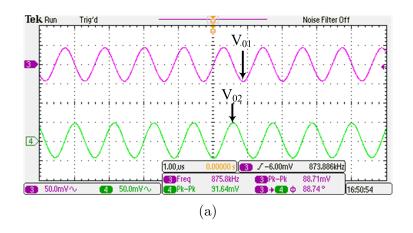

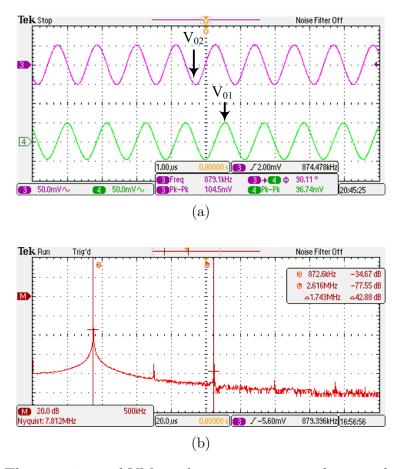

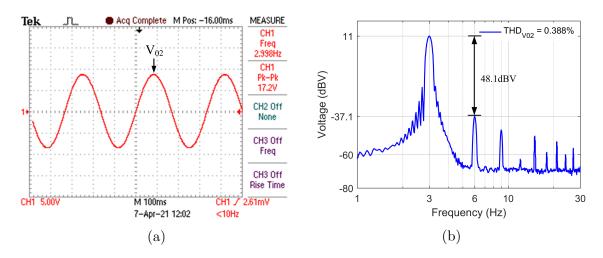

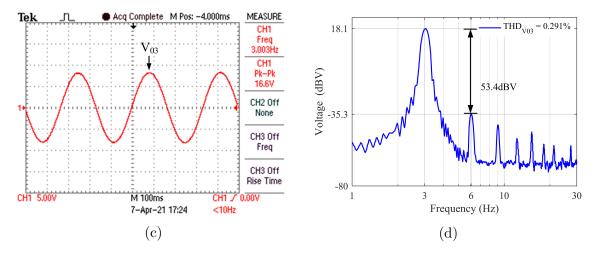

| 3.33 | Experimental quadrature transient output waveforms, XY pattern                                  |

|      | and their frequency spectrum of Fig. 3.21a                                                      |

| 3.34 | Experimental quadrature transient output waveforms, XY pattern                                  |

|      | and their frequency spectrum of Fig. 3.21b                                                      |

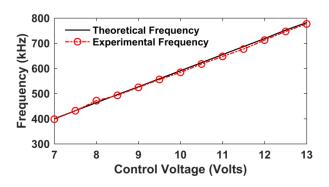

| 3.35 | Variation of frequency with control voltage                                                     |

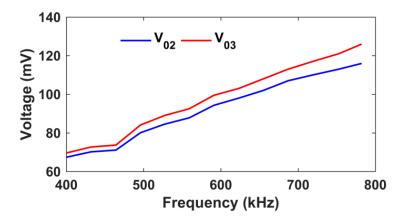

| 3.36 | Experimental voltage variations of the proposed oscillator (3.21b)                              |

|      | with different frequencies                                                                      |

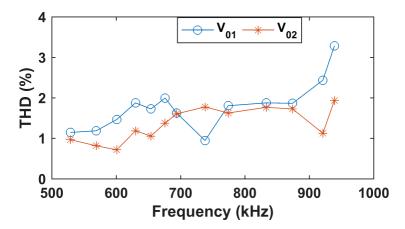

| 3.37 | Experimental %THD variation with different frequencies for Fig. 3.21b134                        |

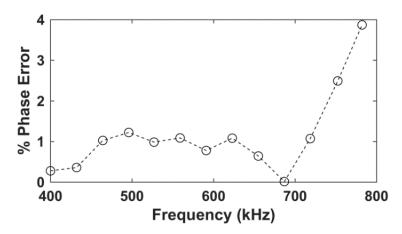

| 3.38 | Error in phase of Fig. 3.21b with different frequencies                                         |

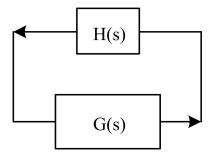

| 4.1  | Generalized block diagram of an autonomous feedback system 144                                  |

|      |                                                                                                 |

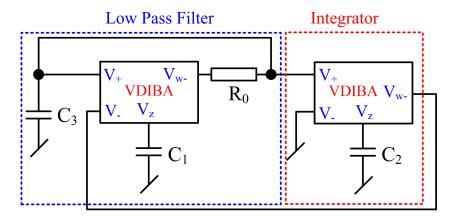

| 4.2  | VDIBA based TOQSO circuit proposed by Pushkar and Bhaskar [7].                 | 145 |

|------|--------------------------------------------------------------------------------|-----|

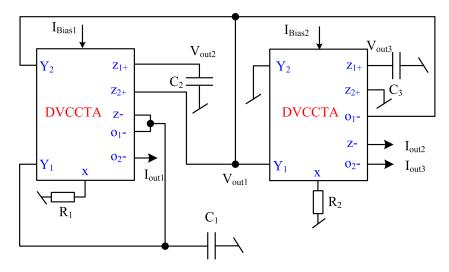

| 4.3  | DVCCTA based TOSO circuit presented by Pandey and Pandey [8]                   | 146 |

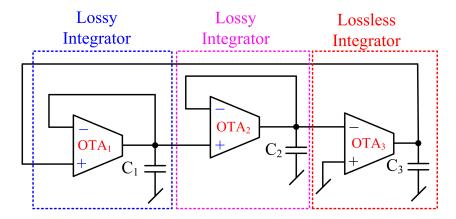

| 4.4  | TOSO circuit reported by Prommee and Dehjan [15]                               | 147 |

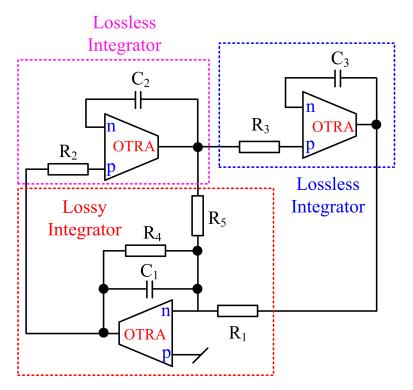

| 4.5  | OTRA based TOSO circuit reported by Pandey, Pandey, Komana-                    |     |

|      | palli and Anurag [6]                                                           | 148 |

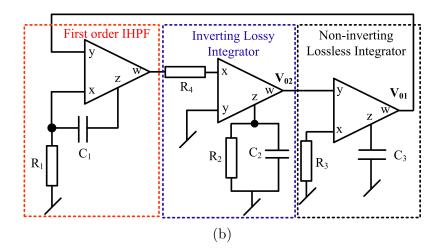

| 4.6  | First order IHPF based TQOSO                                                   | 149 |

| 4.7  | First order IHPF based TQOSO                                                   | 150 |

| 4.8  | Proposed CFOA-based TOQSO configurations using first order IHPF                |     |

|      | approach                                                                       | 151 |

| 4.9  | First order IHPF based TOQSO with parasitic                                    | 152 |

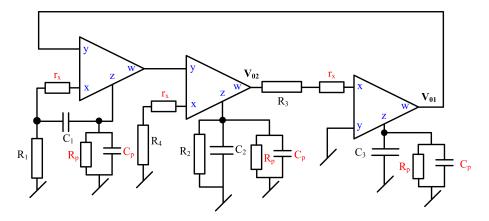

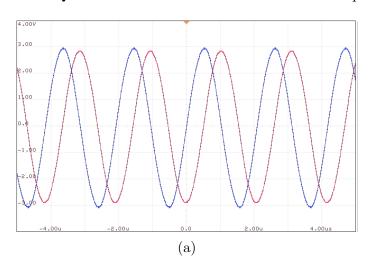

| 4.10 | Experimental results of TOQSO shown in Fig. 4.8a (a) Transient                 |     |

|      | voltage outputs (b) Lissajous pattern (X-Y plot) between $V_{01}$ and $V_{02}$ |     |

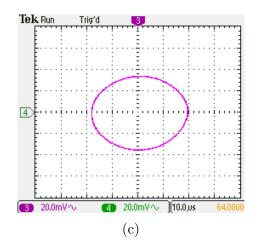

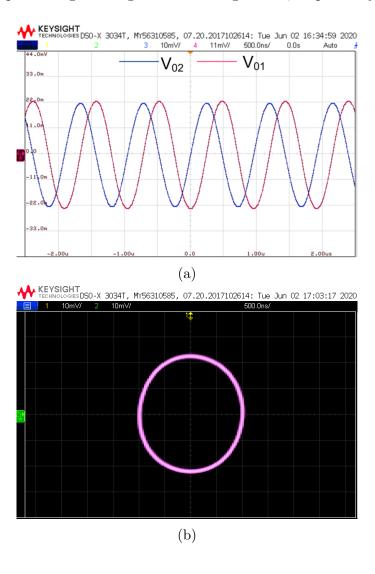

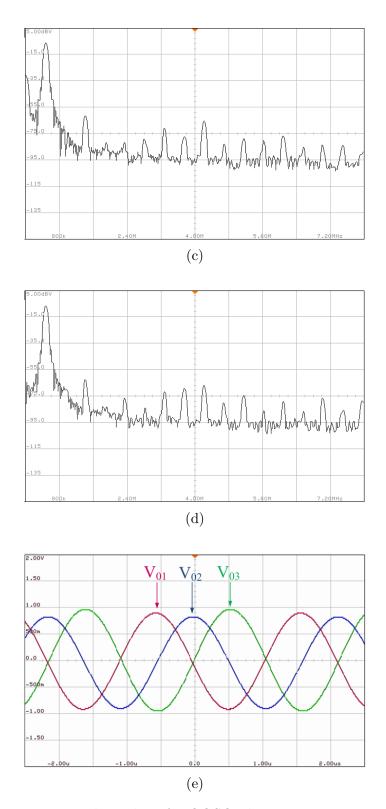

|      | (c) Frequency spectrum of $V_{01}$ and (d) Frequency spectrum of $V_{02}$      | 154 |

| 4.11 | Second order IHPF based TQOSO design approach                                  | 155 |

| 4.12 | CFOA-based TOQSO using second order IHPF approach                              | 156 |

| 4.13 | Second-order IHPF based TOQSO with parasitic                                   | 157 |

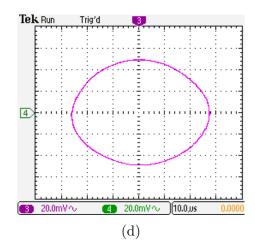

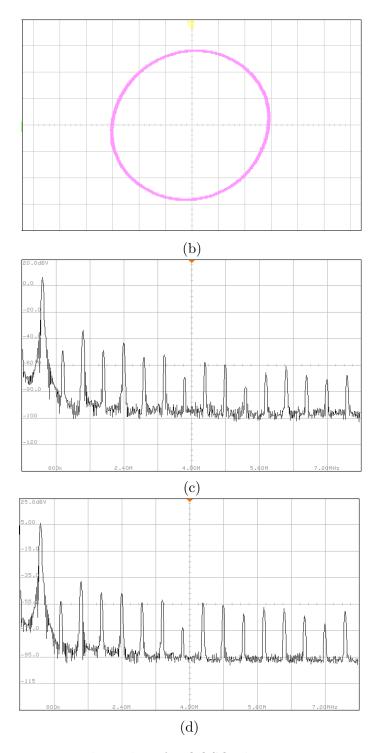

| 4.14 | Experimental results of TOQSO shown in Fig. 4.12 (a) Transient                 |     |

|      | voltage outputs (b) Lissajous pattern (X-Y plot) between $V_{01}$ and $V_{02}$ |     |

|      | (c) Spectrum of $V_{01}$ and (d) Spectrum of $V_{02}$ (e) Transient output     |     |

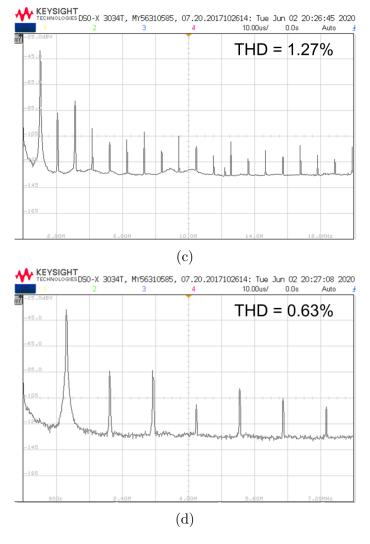

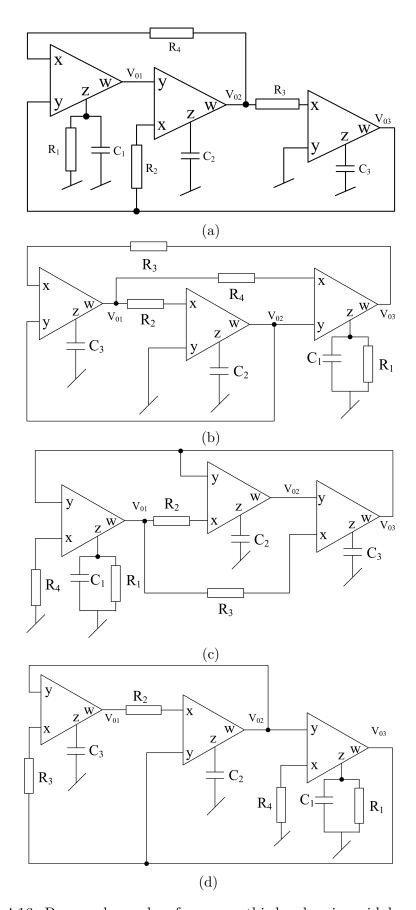

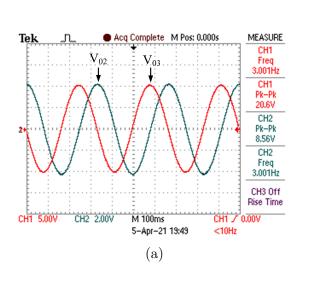

|      | waveforms of three voltages                                                    | 159 |

| 4.15 | Generalized structure for the synthesis of third order oscillators             | 163 |

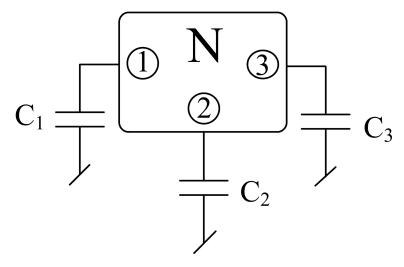

| 4.16 | Proposed very low frequency third order sinusoidal oscillators                 | 167 |

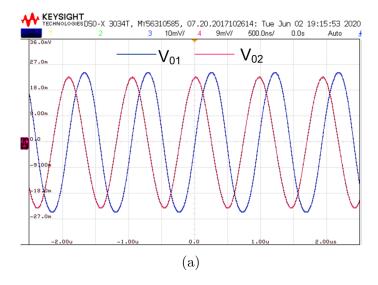

| 4.17 | Experimental quadrature voltage waveforms and frequency spectrum               |     |

|      | of circuits of Fig. 4.16a and Fig. 4.16b                                       | 172 |

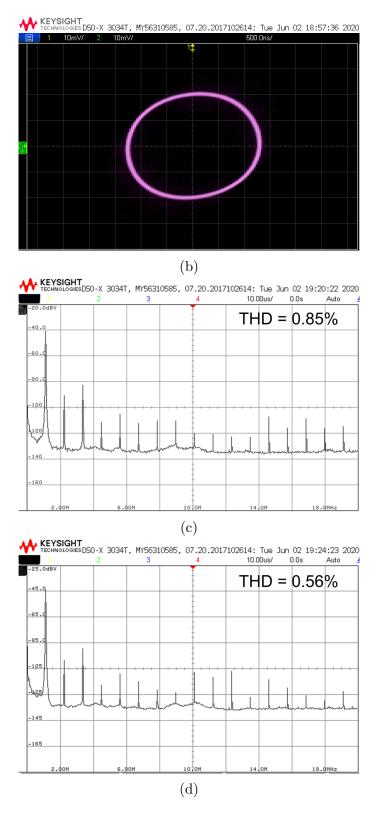

| 4.18 | Experimental transient voltage waveforms and frequency spectrum of             |     |

|      | circuits of Fig. 4.16c and Fig. 4.16d                                          | 173 |

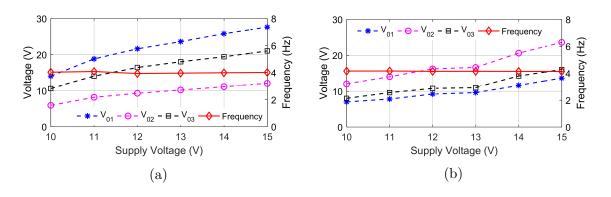

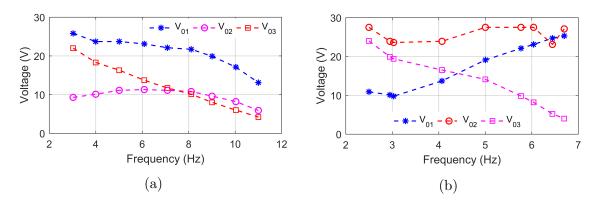

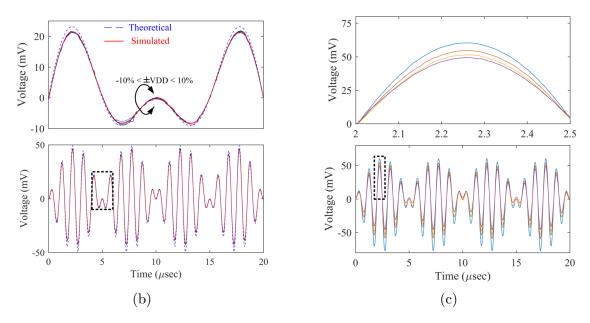

| 4.19 | Variation in the output voltages with power supply voltages (a) Fig.           |     |

|      | 4.16a (b) Fig. 4.16b (c) Fig. 4.16c and (d) Fig. 4.16d                         | 174 |

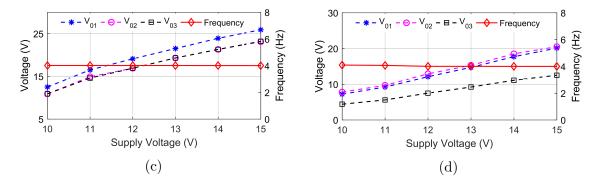

| 4.20 | Variation of frequency with resistance $R_4$ of Fig. 4.16a–Fig. 4.16d          | 174 |

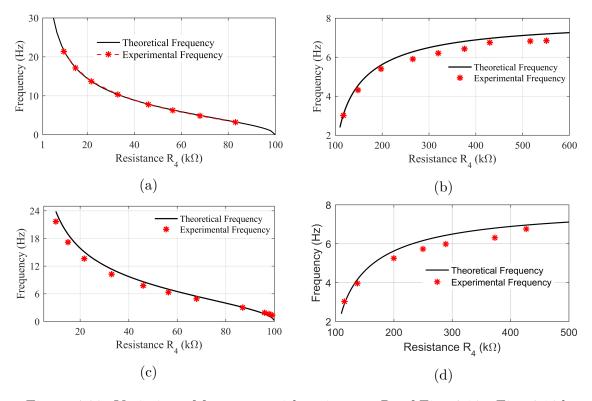

| 4.21 | Variation of output voltages of CFOAs with FO (a) Fig. 4.16a (b)                 |

|------|----------------------------------------------------------------------------------|

|      | Fig. 4.16b (c) Fig. 4.16c and (d) Fig. 4.16d                                     |

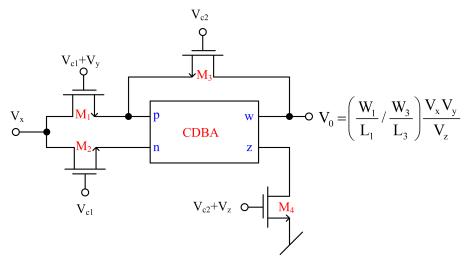

| 5.1  | Analog multiplier reported by Bhanja and Ray [19]                                |

| 5.2  | Analog multiplier reported by Liu and Chen [23]                                  |

| 5.3  | Analog multiplier reported by Chadha and Arora [28]                              |

| 5.4  | Analog multiplier reported by Roy, Paul, Maiti and Pal [33] 184                  |

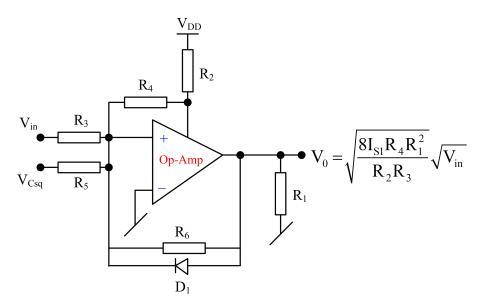

| 5.5  | Op-amp based square root circuit reported by Riewruja and Kamsri                 |

|      | [42]                                                                             |

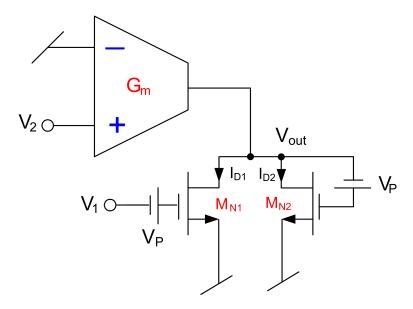

| 5.6  | Proposed new configuration of VM analog divider                                  |

| 5.7  | Generation of floating voltage source [52]                                       |

| 5.8  | Voltage divider circuit                                                          |

| 5.9  | DC transfer curve of $V_{out}$ and $V_1$ with $V_2$ as a variable parameter 196  |

| 5.10 | DC transfer curve of $V_{out}$ and $V_2$ with $V_1$ as a variable parameter 196  |

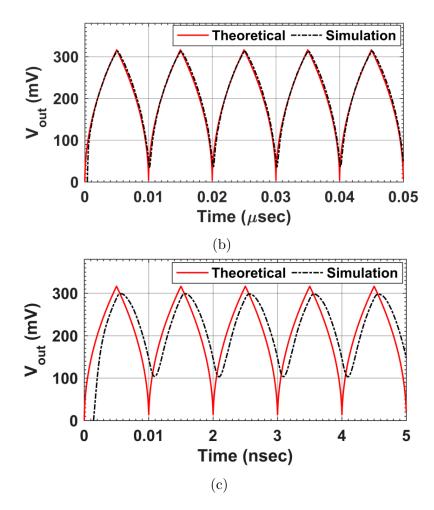

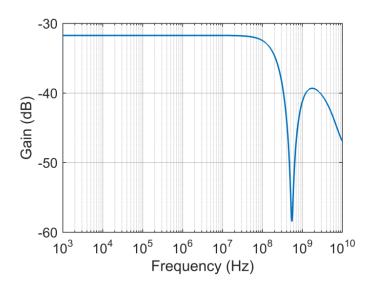

| 5.11 | Frequency response of the proposed analog divider circuit 198                    |

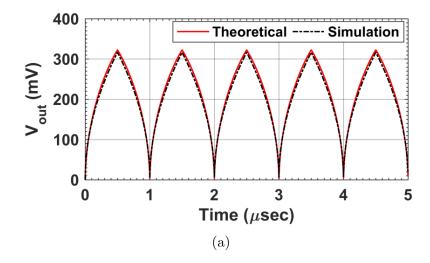

| 5.12 | Transient output responses of the proposed divider circuit at (a) 1              |

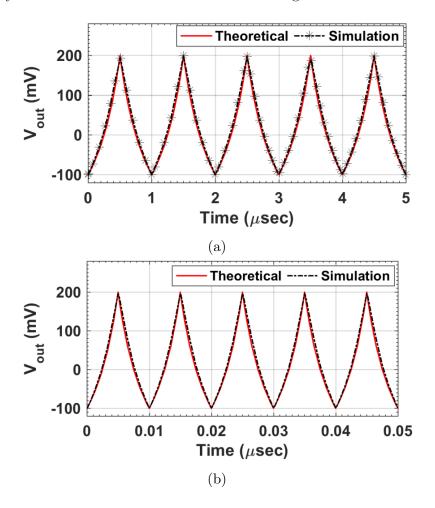

|      | MHz (b) 100 MHz (c) 1 GHz (d) 4 GHz                                              |

| 5.13 | Output voltage of voltage divider circuit with variation in $V_P$ 199            |

| 5.14 | Electronic tunability of output voltage of proposed divider circuit 200          |

| 5.15 | Effect of temperature on output voltage of divider circuit of Fig. $5.6$ . $200$ |

| 5.16 | Input and output transient responses of inverse function of Fig. $5.6$ . $201$   |

| 5.17 | Proposed square-root circuit                                                     |

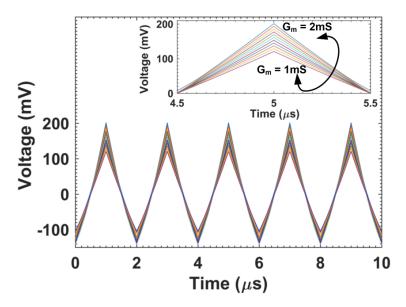

| 5.18 | DC transfer characteristics of output voltage for different bias cur-            |

|      | rents of Fig. 5.17                                                               |

| 5.19 | Frequency response of the proposed square-root circuit of Fig. $5.17$ . $204$    |

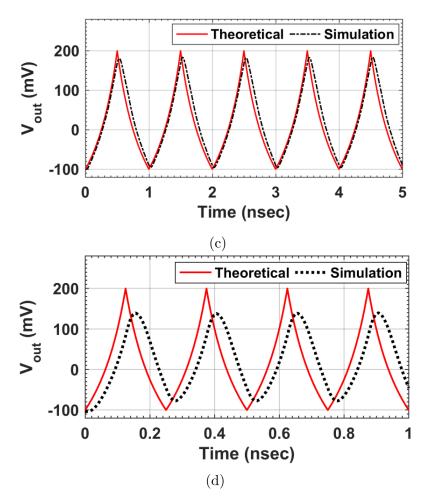

| 5.20 | Transient output responses of the proposed square root circuit at (a)            |

|      | 1 MHz (b) 100 MHz (c) 1 GHz                                                      |

| 5.21 | Transient input and output responses for the sine wave signal of 1 $\rm MHz205$  |

| 5.22 | Effect of temperature on output voltage of square-root circuit 206               |

| 5.23 | Experimental setup for proposed square-root circuit of Fig. 5.17 207             |

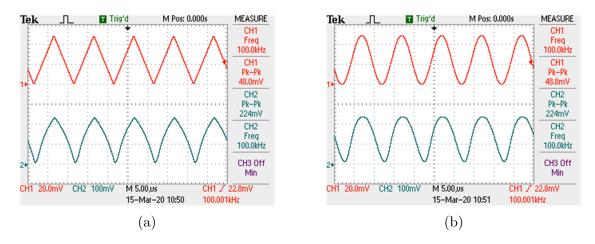

| 5.24 | Experimental input and output transient responses of the proposed                 |     |

|------|-----------------------------------------------------------------------------------|-----|

|      | square-root circuit at 10 kHz (a) triangular wave (b) sinusoidal input 2          | 207 |

| 5.25 | Experimental input and output transient responses of the proposed                 |     |

|      | square-root circuit at 50 kHz (a) triangular wave (b) sinusoidal input 2          | 207 |

| 5.26 | Experimental input and output transient responses of the proposed                 |     |

|      | square-root circuit at 100 kHz (a) triangular wave (b) sinusoidal input $\hat{z}$ | 208 |

| 5.27 | Scheme to linearize transducer output [24]                                        | 208 |

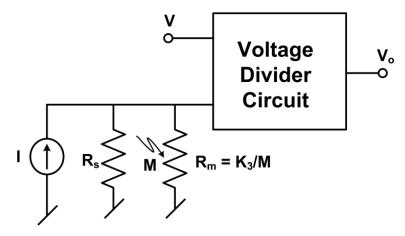

| 5.28 | Scheme to control resistor through output of the divider circuit 2                | 209 |

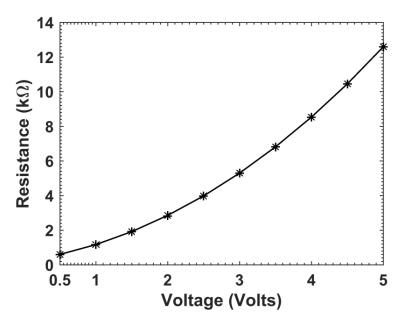

| 5.29 | Variation of $R_{in}$ with $V_1$                                                  | 210 |

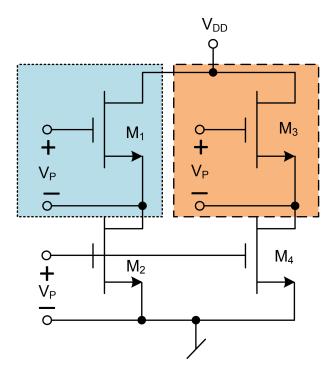

| 5.30 | VM analog multiplier/divider configuration                                        | 211 |

| 5.31 | CMOS implementation of CFOA [54]                                                  | 213 |

| 5.32 | DC analysis curves of $V_{out}$ and $V_2$ with $V_1$ as a variable parameter 2    | 215 |

| 5.33 | Frequency response of proposed multiplier circuit                                 | 216 |

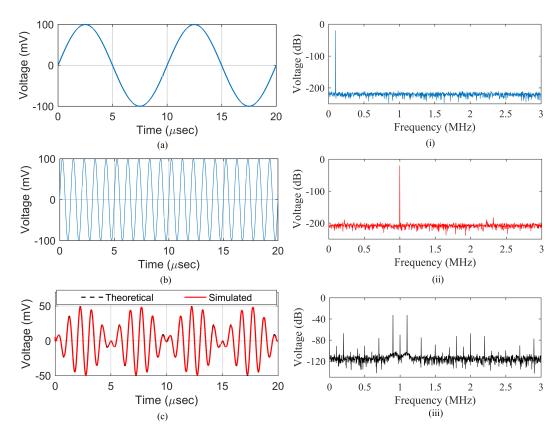

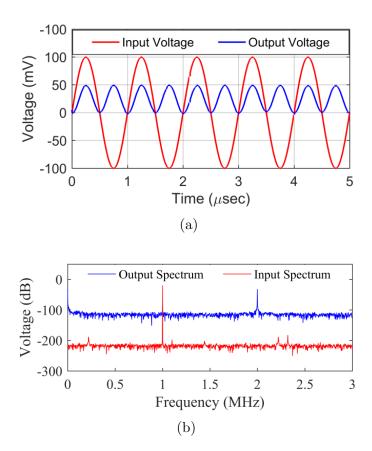

| 5.34 | Transient input-output voltages of modulator circuit and their respec-            |     |

|      | tive frequency spectrums                                                          | 217 |

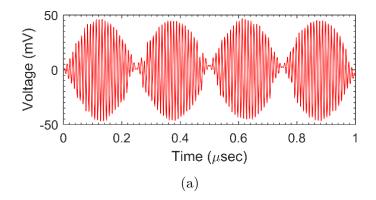

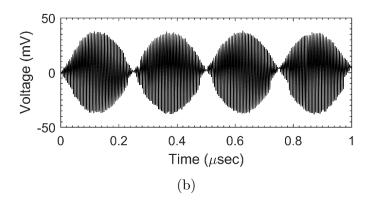

| 5.35 | Simulated transient output voltage of modulator circuit at (a) 100                |     |

|      | MHz and (b) 200 MHz                                                               | 218 |

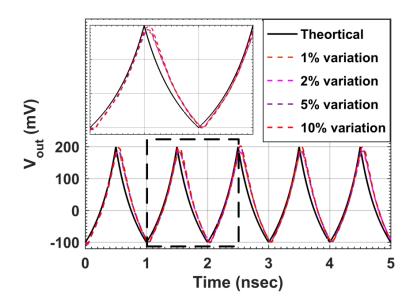

| 5.36 | Output voltage of amplitude modulator with variation in aspect ratio              |     |

|      | of MOSFETs                                                                        | 218 |

| 5.37 | Histogram of the amplitude modulator                                              | 219 |

| 5.38 | Output voltage of amplitude modulator corresponding to (a) process                |     |

|      | variations (b) supply voltage variations and (c) temperature varia-               |     |

|      | tions                                                                             | 220 |

| 5.39 | Output noise of amplitude modulator                                               | 220 |

| 5.40 | Transient input and output voltages of squarer circuit and its fre-               |     |

|      | quency spectrums                                                                  | 221 |

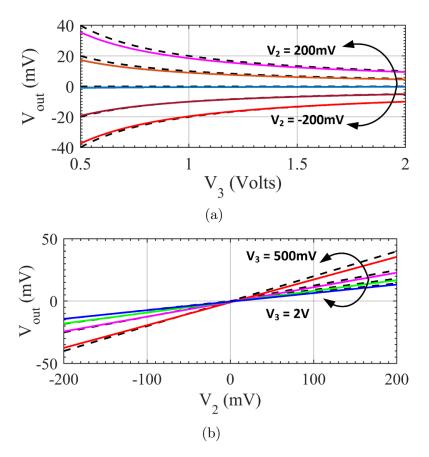

| 5.41 | DC response of analog divider circuit (a) when $V_2$ is varied (b) when           |     |

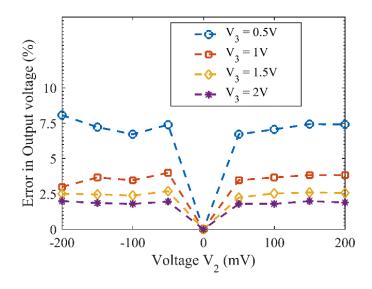

|      | $V_3$ is varied                                                                   | 222 |

| 5.42 | Error in output voltage of divider for different values of $V_2$ and $V_3$ 2      | 222 |

| 5.43 | Time response of the circuit in division mode                        | 223 |

|------|----------------------------------------------------------------------|-----|

| 5.44 | (a) Frequency responses of proposed divider circuit (b) Variation in |     |

|      | temperature on divider circuit (c) Output noise of analog divider    |     |

|      | circuit                                                              | 224 |

## List of Tables

| 1.3  | Aspect ratios of MOSFETs                                                       |

|------|--------------------------------------------------------------------------------|

| 1.4  | Various parameters of bipolar and CMOS OTAs                                    |

| 1.5  | Parameters of AD844 [178]                                                      |

| 2.1  | Active and passive sensivities of $\omega_0$ , $Q_{0i}$ and $BW_{0i}$          |

| 2.2  | Aspect ratio of MOSFETs shown in Fig. 2.15 60                                  |

| 2.3  | Gain of the various filter functions                                           |

| 3.1  | CO and FO of circuit of Fig. 3.8                                               |

| 3.2  | Quadrature relationship between voltages $V_{01}$ and $V_{02}$                 |

| 3.3  | Quadrature relationship between voltages $I_{01}$ and $I_{02}$ 105             |

| 3.4  | Phase noise power spectral density and frequency stability factor 108          |

| 3.5  | Aspect ratios of MOSFETs shown in Fig. 3.10                                    |

| 3.6  | Various transconductance values used for Fig. 3.8                              |

| 3.7  | Simulated frequency, %THD, and phase $(\phi)$ for the circuits of Fig. 3.8.111 |

| 3.8  | Various biasing resistors used for experimental setup                          |

| 3.9  | Error in experimental FO and phase of proposed TOQSOs 116                      |

| 3.10 | Simulated frequency, %THD, $P_D$ , and phase $(\phi)$ of Fig. 3.21 128         |

| 4.1  | Sensitivity of $\omega$ with respect to passive components                     |

| 4.2  | Frequency stability factors of the proposed low frequency sinusoidal           |

|      | oscillators                                                                    |

| 5.1  | Theoretical and simulated output voltages with error for different             |

|      | values of $V_1$ and $V_2$                                                      |

| 5.2 | Theoretical and simulated output voltage and $\%$ error in output voltage<br>203 |

|-----|----------------------------------------------------------------------------------|

| 5.3 | Aspect ratios of MOSFETs as shown in Fig. 5.31                                   |

## List of Symbols

$g_m$  Transconductance

R Resistor

C Capacitor

$I_{Bias}$  Bias Current

$\omega$  Pole Frequency

Q Quality Factor

BW Bandwidth

H Voltage Gain

S Sensitivity

$\Omega$  Ohm

υ Mho

$g_p$  Parasitic Transconductance

$R_p$  Parasitic Resistance

$C_p$  Parasitic Capacitance

$r_o$  Output Resistance

$C_o$  Output Capacitance

$\phi$  Phase

$S^F$  Stability Factor

$I_D$  Drain Current

$V_{DS}$  Drain to Source Voltage

$V_{GS}$  Gate to Source Voltage

$V_{TH}$  Threshold Voltage

$\mu_n$  Surface Mobility

$C_{ox}$  Gate Oxide Capacitance per Unit Area

W Width

L Length

### List of Abbreviations

ABB Active Building Block

IC Integrated Circuit

Op-Amp Operational Amplifier

OTA Operational Transconductance Amplifier

CC Current Conveyor

CCII Second Generation Current Conveyor

MCCCII Multiple Outputs Current Controlled Conveyor

DO-CCCII Dual Output Current Controlled Current Conveyor

DDCC Differential Difference Current Conveyor

FDCCII Fully Differential Current Conveyor

DVCC Differential Voltage Current Conveyor

CFOA Current Feedback Operational Amplifier

FTFN Four Terminal Floating Nullors

VDTA Voltage Differencing Transconductance Amplifier

CDTA Current Differencing Transconductance Amplifier

CCCCTA Current Controlled Current Conveyor Transconductance Amplifier

DVCCTA Differential Voltage Current Conveyor Transconductance Amplifier

CFTA Current Follower Transconductance Amplifier

CDCTA Current Differencing Cascaded Transconductance Amplifier

MCCTA Modified Current Conveyor Transconductance Amplifier

MISO Multiple-Input Single-Output

A/D Analog to Digital Converter

D/A Digital to Analog Converter

VM Voltage Mode

CM Current Mode

TRM Transresistance Mode

TCM Transconductance Mode

TOQSO Third Order Quadrature Sinusoidal Oscillator

BJT Bipolar Junction Transistor

MOSFET Metal Oxide Semiconductor Field Effect Transistor

CMOS Complementary Metal Oxide Semiconductor

GC Grounded Capacitor

LPF Low Pass Filter

APF High Pass Filter

BPF Band Pass Filter

BRF Band Reject Filter

APF All Pass Filter

TOQSO Third Order Quadrature Sinusoidal Oscillator

CO Condition of Oscillation

FO Frequency of Oscillation

### Chapter 1

#### Introduction

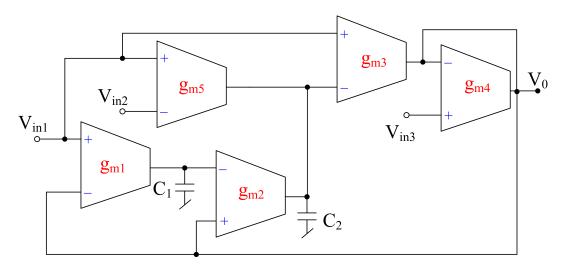

This thesis deals with the "Implementation of signal processing/generation circuits using modern active building blocks". Several new analog signal processing circuits, both linear as well as non-linear and signal generation circuits employing operational transconductance amplifiers (OTAs) and current feedback operational amplifiers (CFOAs) have been presented.

The integrated circuit (IC) op-amp has been the most-widely used analog circuit building block to design analog functions as, during the initial years of development of analog ICs, most of the signal processing was done in the so called "voltage mode". Since, IC op-amp  $\mu$ A741, which was among the most widely produced integrated circuits, was the circuit implementation of a differential voltage controlled voltage source (DVCVS). It was used for different signal processing/generation circuits to implement both linear and non-linear functions. However, in general, the op-amp circuits exhibit: (i) gain bandwidth conflict (except when configured as current controlled voltage source) (ii) limited frequency range of operation (due to finite gain bandwidth product) on one hand and due to the slew-induced distortion (because of finite slew rate of op-amp) on the other hand (iii) requirement of more than the canonic number of passive elements and (iv) requirement of perfect component matching conditions in many cases.

To alleviate the limitations of conventional op-amp circuits and to utilize the advances made in the semiconductor fabrication technologies, both, bipolar as well as CMOS, researchers and circuit designers worldwide have proposed several al-

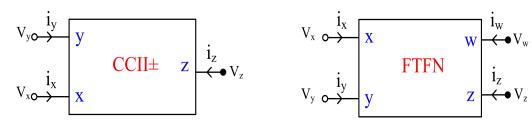

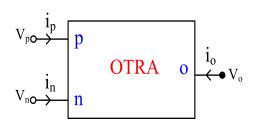

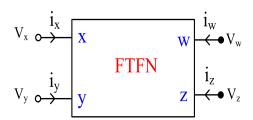

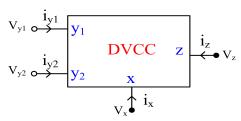

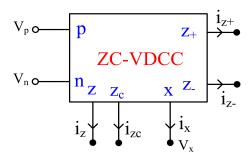

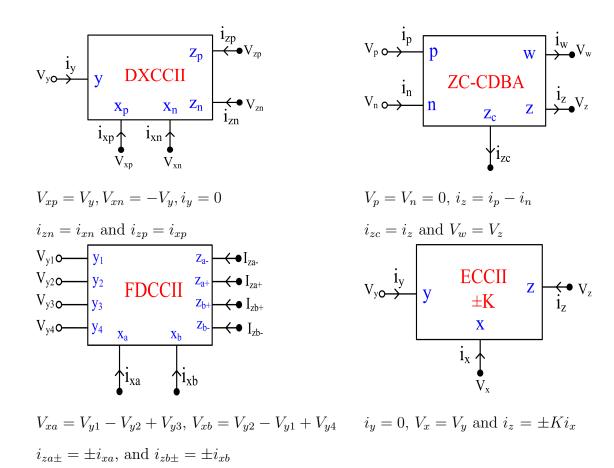

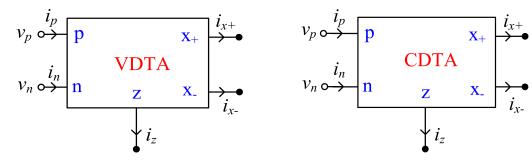

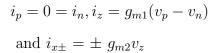

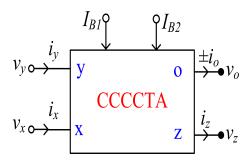

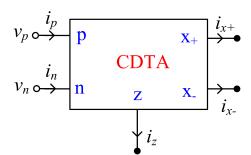

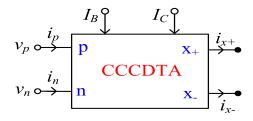

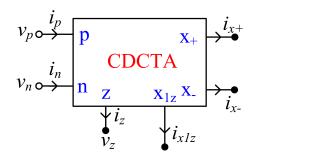

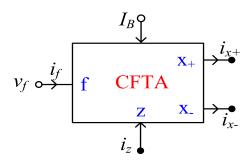

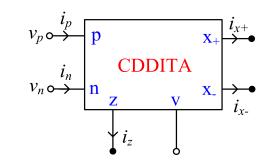

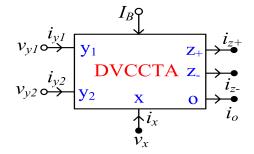

ternative new analog active building blocks (ABBs) from time to time during the past four decades [1–13]. These building blocks have been used to realize (a) active filters in: (i) voltage mode (VM) [14–29], (ii) current mode (CM) [29–32], (iii) transimepedance mode [30, 33], (iv) mixed mode [34–63], (v) MOS-C [64–69], (vi) frequency agile [70–73], (vii) memristor-based [74–77] (b) oscillators (i) second order harmonic and quadrature sinusoidal oscillators [78–93] (ii) third order sinusoidal oscillators [94–128], and also in non-linear function generator circuits [129–173]. The functional block diagrams and port realtionships of some of the important modern active building blocks are shown below:

$$i_y = 0, V_x = V_y$$

and  $i_z = \pm i_x$

$$V_p = 0, V_n = 0 \ and$$

$$V_0 = R_m(i_p - i_n)$$

$$V_p = 0 = V_n, i_z = i_{zc} = (i_p - i_n)$$

$i_{x+} = + g_m V_z \text{ and } i_{x-} = - g_m V_z$

$$V_x = V_y = 0, i_x = 0, i_y = 0$$

$$i_w = i_z$$

and  $V_w, V_z = arbitary$

$$i_{y1} = i_{y2} = 0, V_x = (V_{y1} - V_{y2}), i_{z\pm} = \pm i_x$$

$$i_z = g_m(V_p - V_n), i_{z\pm} = \pm i_x$$

and  $V_x = V_z$

Among the large number of new analog ABBs, only the operational transconductance amplifiers (OTA), current conveyors (CC) and current feedback operational amplifiers (CFOA) have been made available as off-the-shelf ICs [174].

Since the work presented in this thesis deals with a modern active building blocks viz. OTAs and CFOAs, it is worthwhile to present a brief overview of these ABBs.

#### 1.0.1 Operational Transconductance Amplifier

The operational transconductance amplifier, which is the circuit implementation of a differential voltage controlled current source, is a very useful active building block and is available as an off-the-shelf IC from manufacturers e.g. Radio Corporation of America (CA3080), National Semiconductor (LM13700), Maxim (MAX435). Several integrable, both bipolar as well as CMOS implementations of OTA are available in an open literature [175–177]. The most striking feature of an OTA is its very simple architecture (an actively loaded differential pair), and easy programmability of

the parameters of the realized circuits acheived by varying its transconductance gain  $(g_m)$ . Also, the OTA-based circuits can be designed without employing passive resistors! With the emergence of the current-mode techniques in analog circuit design, OTAs have become more relevant as the output of an OTA is a current, which is available at a very high impedance node (ideally infinite) in the circuit (providing ease of cascadability).

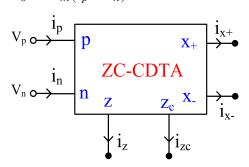

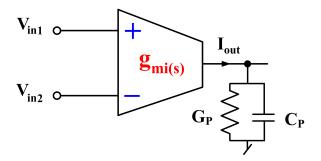

OTAs have also been employed as sub-blocks in many of the recently proposed analog active building blocks (ABBs), like voltage differencing transconductance amplifiers (VDTA), current differencing transconductance amplifiers (CDTA), current controlled current conveyor transconductance amplifiers (CCCCTA), differential voltage current conveyor transconductance amplifiers (DVCCTA), current follower transconductance amplifiers (CFTA), current differencing cascaded transconductance amplifiers (CDCTA) etc [1]. The symbolic representation and characteristic equation of the important ABBs employing OTAs are given below.

$$i_y = 0, v_x = i_x R_x + v_y, i_z = i_x$$

and  $i_o = g_m v_z$

$$v_p=v_n=0, i_z=(i_p-i_n)$$

and  $i_{x+}=\pm g_m v_z$

$$v_p = R_p i_p, v_n = R_n i_n, i_z = i_p - i_n$$

and  $i_x = \pm g_m v_z$

$$V_p = V_n = 0, I_z = I_p - I_n, \text{ and } I_{x1} = g_{m1}V_z$$

$$v_f = 0, i_z = i_f$$

and  $i_{x\pm} = \pm g_m v_{x\pm}$

$$v_p = v_n = 0, i_z = (i_p - i_n),$$

and  $i_{x\pm} = \pm g_m(v_z - v_v)$

$$i_{y1} = i_{y2} = 0$$

,  $i_{z\pm} = \pm i_x$

$v_x = v_{y1} - v_{y2}$ , and  $i_{0\pm} = g_m v_{z\pm}$

#### 1.0.1.1 Bipolar Implementation of OTA

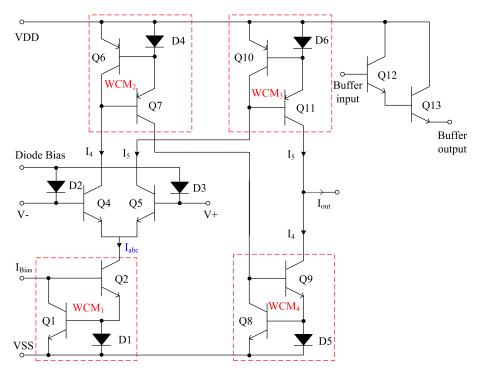

The bipolar implementation of OTA [175] used in the design of off-the-shelf IC LM13600/LM13700 is shown in Fig. 1.1.

The differential transistor pair  $Q_4$  and  $Q_5$  shown in Fig. 1.1 form a transconductance stage in that the ratio of their collector currents is defined in terms of differential input voltage  $V_{id}$  as:

$$V_{id} = (V_{+} - V_{-}) = \frac{kT}{q} ln \frac{I_5}{I_4}$$

(1.1)

where  $\frac{kT}{q} = V_T$  = thermal voltage, k is the Boltzmann's constant (1.3806485210<sup>-23</sup> $m^2kgs^{-2}K^{-1}$ ), T is temperature in Kelvin and q is the charge on electron (-1.6 x 10<sup>-19</sup> Coloumb). At room temperature (300K),  $V_T$  is equal to 26mV.

Transistors  $Q_1$ ,  $Q_2$  with diode  $D_1$  form a Wilson current mirror (WCM) which is used to bias the differential pair. For large  $\beta_0$  transistors,  $I_{abc}$  can be approximated

Figure 1.1: Bipolar implementation of one OTA used in LM13600/LM13700 [175]

as:

$$I_{abc} \approx (I_4 + I_5) \tag{1.2}$$

where  $I_{abc}$  is the amplifier bias current applied to the gain pin.

The active load for the differential pair is constituted by another WCM, formed by  $Q_6$ ,  $Q_7$  and  $D_4$ . The output current of OTA  $(I_{out})$  is obtained by the current differencing action provided by  $WCM_3$   $(Q_{10}, Q_{11} \text{ and } D_6)$  and  $WCM_4$   $(Q_8, Q_9 \text{ and } D_5)$ . Therefore, the output current  $I_{out}$  becomes:

$$I_{out} = 2\left(\frac{I_{abc}}{4V_T}\right)V_{id}$$

$$= \left(\frac{I_{abc}}{2V_T}\right)V_{id} = g_m V_{id}$$

(1.3)

where  $g_m = \frac{I_{abc}}{2V_T}$  is the transconductace of OTA.

Diode linearization scheme [177], has been used in LM13700 ( $D_2$  and  $D_3$ ) to enhance the input linear range, which is otherwise restricted to  $\pm 2V_T$ .

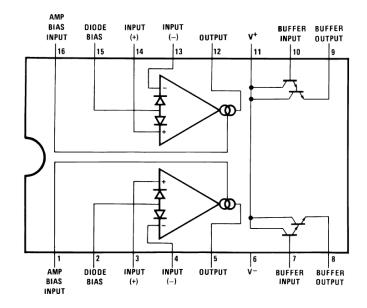

The IC LM13600/LM13700 contains two OTAs and two voltage buffers in the package and its pin diagram is shown in Fig. 1.2.

Figure 1.2: Pin diagram of LM13600/LM13700 [175]

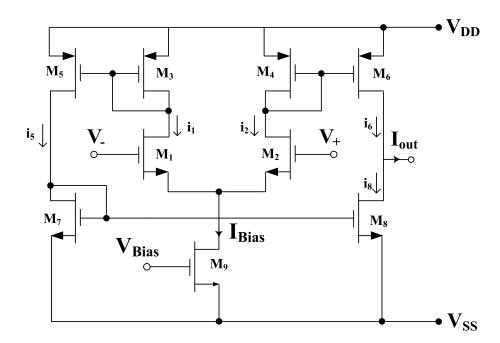

#### 1.0.1.2 CMOS Implementation of OTA

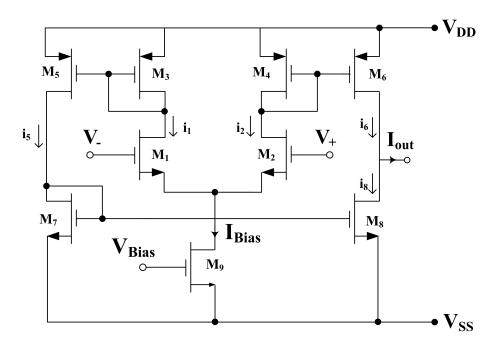

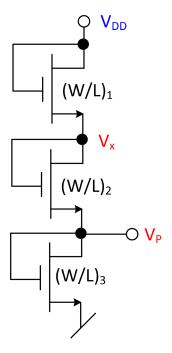

In Fig. 1.3, CMOS implementation of OTA [177] has been shown (assuming all MOSFETs are operating in saturation region).

Figure 1.3: CMOS implementation of OTA [177]

From the circuit shown in Fig. 1.3 (negelecting channel length modulation), it is found that:

$$I_{out} = (i_6 - i_8) = (i_2 - i_1) (1.4)$$

as  $i_1 = i_5$  (for identical MOSFETs  $M_1$  and  $M_5$ ),  $i_2 = i_6$  (for identical MOSFETs  $M_4$  and  $M_6$ , and  $i_5 = i_8$  (for matched devices  $M_7$  and  $M_8$ . It can be shown that  $(i_1 - i_2) \propto (V_+ - V_-)$ , then the output current becomes:

$$I_{out} = g_m V_{id} (1.5)$$

where  $g_m = \sqrt{\mu_n C'_{ox}(W/L)_n I_{Bias}}$ ,  $\mu_n$  is is the surface mobility,  $C'_{ox}$  is the gate oxide capacitance per unit area and W/L is the aspect ratio of MOSFETs  $M_1$  and  $M_2$ .

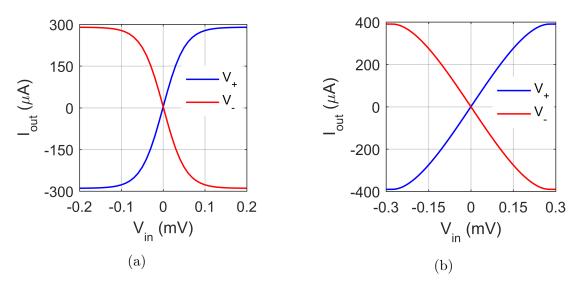

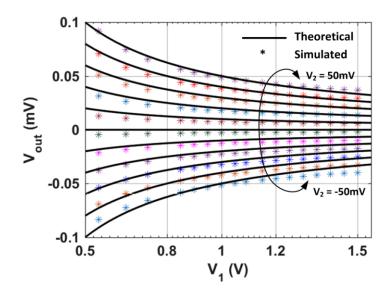

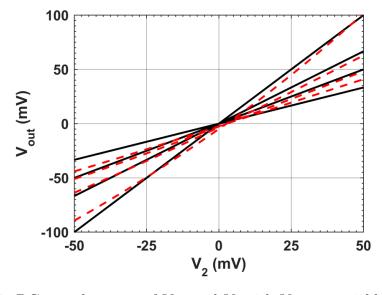

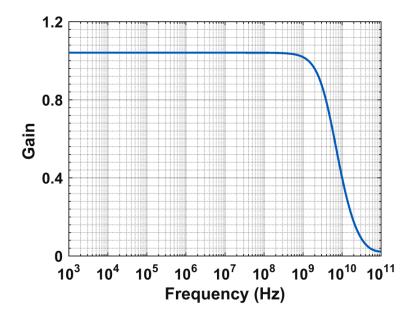

#### 1.0.1.3 DC and Frequency Characteristics of an OTA

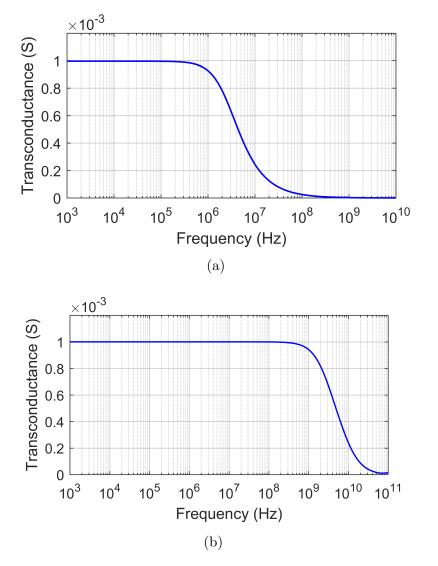

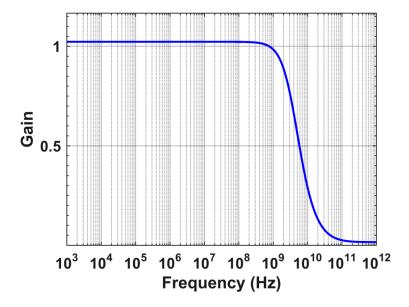

The DC transfer characteristics (differential input voltage versus output current) and frequency response of bipolar OTA and CMOS OTA have been displayed in Fig. 1.4 and Fig.1.5 respectively, when one of the input voltage of OTA is at ground (i.e. either  $V_+$  or  $V_-$ ). The macro model of LM13600/LM13700 has been used for bipolar OTA, whereas, the CMOS OTA has been simulated with 0.18 $\mu$ m CMOS technology parameters. The aspect ratios of different transistors used for Fig. 1.3 are given in Table 1.3.

Table 1.3: Aspect ratios of MOSFETs

| MOSFETs        | Aspect Ratio (W/L) |

|----------------|--------------------|

| M1, M2         | 3.6/0.36           |

| M3, M4, M7, M8 | 1.44/0.36          |

| M5, M6         | 2.88/0.36          |

| M9             | 5.4/0.36           |

The operating range of differential input voltage of an OTA can be obtained from Fig. 1.4 and the maximum bandwidth of the OTA can be determined from Fig. 1.5. The various parameters such as linearity range, bandwidth, DC power dissipation, minimum and maximum values of bias current of bipolar and CMOS OTAs shown in Fig. 1.1 and Fig. 1.3 are given in Table 1.4.

Figure 1.4: DC transfer characteristics of (a) Bipolar OTA (b) CMOS OTA

Figure 1.5: Frequency responses of (a) Bipolar OTA (b) CMOS OTA

Table 1.4: Various parameters of bipolar and CMOS OTAs

| Parameters                  | Bipolar OTA*       | CMOS OTA             |

|-----------------------------|--------------------|----------------------|

| Linearity range             | -50 mV  to  +50 mV | -150 mV  to  +150 mV |

| Bandwidth                   | $2 \mathrm{~MHz}$  | $2.84~\mathrm{GHz}$  |

| DC power dissipation        | 570  mW            | $0.365~\mathrm{mW}$  |

| Minimum value of $I_{Bias}$ | 5.4/0.36           | $50\mu\mathrm{A}$    |

| Maximum value of $I_{Bias}$ | $2\mathrm{mA}$     | $1.5 \mathrm{mA}$    |

| Supply voltage              | ±15V               | ±0.9V                |

<sup>\*(</sup>We have not biased the linearising diodes  $D_1$  and  $D_2$  in our research work)

#### 1.0.2 Current Feedback Operational Amplifier

Current feedback operational amplifiers are also seeking attention of the researchers, in implementation of linear and non-linear signal processing and signal generation circuits, because of better AC performance, high linearity and excellent pulse response. Because of its very high slew rate, of the order of several hundreds to several thousands  $V/\mu$ sec, CFOAs could lead to circuits capable of operating over much wider frequency range than those possible with traditional operational amplifiers.

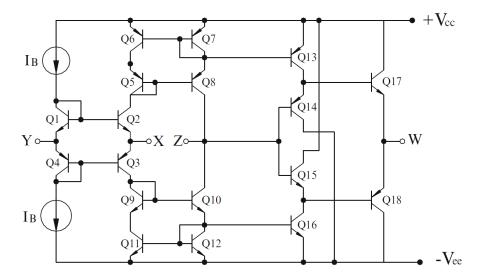

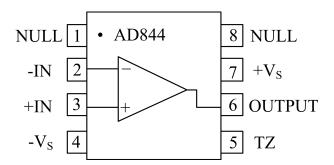

The CFOAs have been manufactured in IC form by several manufacturers including Analog Devices (AD844) [178] whose bipolar implementation has been shown in Fig. 1.6 [174] and its pin diagram is shown in Fig. 1.7.

In the internal architecture of the CFOA, transistors Q1–Q4 are configured as a mixed translinear cell (MTC) while the collector currents of transistors Q2 and Q3 are sensed by two modified p-n-p and n-p-n Wilson current mirrors consisting of transistors Q5–Q8 and Q9–Q12 respectively to create a replica of current  $i_X$  at the terminal - Z thereby yielding  $i_Z = i_X$ . The two constant current sources, each equal to  $I_B$ , force equal emitter currents in transistors Q1 and Q4 thereby forcing input current  $i_Y = 0$  when a voltage  $V_Y$  is applied at the input terminal -Y. It can be easily shown that with  $i_X = 0$ ,  $V_X = V_Y$  and the Z-port current  $i_Z$  will be zero [174].

Figure 1.6: Schematic of the CFOA AD844 [174]

Figure 1.7: Pin diagram of AD844 [178]

However, for the case if  $i_X \neq 0$ , an exact analysis of the circuit using exponential relations between collector currents and base-emitter voltages for the transistors Q1–Q4 yields:

$$i_Z = i_X = -2I_B Sinh\left(\frac{V_Y - V_X}{V_T}\right) \tag{1.6}$$

An approximate relation between  $V_X$ ,  $V_Y$  and  $r_X$  (for  $i_X << 2I_B$ ) can be expressed as:

$$V_X \approx (V_Y + r_X i_X) \tag{1.7}$$

where  $r_X = \frac{V_T}{2I_B}$

If terminal - Z is terminated into an external impedance/load  $Z_L$ , a voltage  $V_Z$  is created which passes through the voltage follower made from another MTC composed of transistors Q13–Q18 for which transistors Q13 and Q16 provide the DC bias currents. The last stage is characterized by an equation similar to (1.7) which

provides  $V_W \approx V_Z$ .

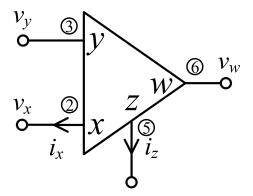

The defining equations of an ideal CFOA shown in Fig. 1.8 are given in matrix form as:

$$\begin{bmatrix} i_Y \\ v_X \\ i_Z \\ v_W \end{bmatrix} = \begin{bmatrix} 0 & 0 & 0 & 0 \\ 1 & 0 & 0 & 0 \\ 0 & 1 & 0 & 0 \\ 0 & 0 & 1 & 0 \end{bmatrix} \begin{bmatrix} v_Y \\ i_X \\ v_Z \\ i_W \end{bmatrix}$$

(1.8)

The symbolic representation of an ideal CFOA has been presented in Fig. 1.8.

Figure 1.8: Symbolic representation of CFOA

The various parameters of AD844 type CFOA have been provided in Table 1.5

Table 1.5: Parameters of AD844 [178]

| Parameters                 | Bipolar CFOA                    |

|----------------------------|---------------------------------|

| Operating range            | ±18V                            |

| Bandwidth                  | $60 \mathrm{\ MHz}$             |

| DC power dissipation       | 1.1 Watt                        |

| Input common mode voltage  | $\pm 18V$                       |

| Quiescent current          | $6.5 \mathrm{mA}$               |

| Differential input voltage | 6 V                             |

| Slew rate                  | $2000~\mathrm{V}/\mu\mathrm{s}$ |

#### 1.1 Research Objectives

Though, OTAs have been used to design various types of active filters with different features [3], a careful perusal of the available research work done on the realization of OTA-based filters, it has been observed that compared to other types of universal active filters, relatively less work has been reported on the realization of multiple input single output (MISO) type universal active filters in voltage mode [14–16, 18–28] and MISO type universal active filters in mixed-mode [56–63].

Applications of different ABBs [94–128] including OTAs and CFOAs, in the realization of third order quadrature sinusoidal oscillators, have also been reported by various researchers because of many advantageous features such as lesser harmonic distortions, lower noise, better accuracy and high quality factor, as compared to second order harmonic oscillators. An extensive literature survey on third order sinusoidal oscillators realized with different ABBs, has revealed that only two circuits employing only OTAs [94] and [126] and only one third order sinusoidal oscillator circuit employing CFOAs [128] have been reported in the open literature.

Analog multipliers, dividers and square root circuits [129–145, 147–154, 156–163, 165–170, 172, 173] also play an important role in analog signal processing, telecommunications, and electronic systems, A/D and D/A converters, peak detectors, phase detectors, synthesizers as well as in analog computational systems based on biological 'neural' paradigms [179]. In open literature, various ABBs have been used for the design of voltage mode (VM) analog dividers and square root circuits. CFOAs have also been employed to implement non-linear functions (differential multiplier and divider circuits) [173] uses an excessively large number of components (five CFOAs, six MOSFETs and four identical capacitors).

From a detailed observance of the research works reported above, it has been found that:

(i) There are no circuits available in open literature which can provide all five filter functions in VM based on MISO topology with five or less than five single output OTAs.

- (ii) No mixed mode universal active filters have been reported yet, which can provide all five generic filter functions in all four modes with one type of ABBs.

- (iii) Though there are a number of third order sinusoidal oscillators available in the open literature, very few OTA-based realizations of third order quadrature sinusoidal oscillator (TOQSO) circuits exist.

- (iv) Compared to the available topologies for generation of third order quadrature sinusoidal oscillators with different properties, very few topologies exist in open literature for the generation of TOQSOs.

- (v) No third order sinusoidal oscillator circuits are available in open literature which can generate low frequency sinusoidal oscillations.

- (vi) Though there are a number of VM divider and square root circuits reported, yet no circuit exists which has single ABB and lesser number of MOSFETs.

- (vii) No work has been presented on the realization of single CFOA-based analog multiplier and divider function from the same topology.

Based upon the above discussions, the following research objectives were identified:

#### Realization of:

- (i) OTA-based universal biquad filters with properties and features which were not available in previously reported OTA- based universal filters.

- (ii) new OTA-based third order quadrature sinusoidal oscillator circuits.

- (iii) new CFOA-based third order sinusoidal oscillator circuits.

- (iv) OTA-based non-linear function generation circuits with lesser components count.

- (v) CFOA-based non-linear function generation circuit with lesser components count.

### 1.2 Organisation of Thesis

The work presented in the thesis has been organized in the following manner:

In Chapter 2, we have presented three circuits of VM universal biquad filters based

on MISO topology employing OTAs. All five filter functions are realizable from the proposed filter structures by appropriate selection(s) of input voltages. A mixed mode universal active filter configuration using OTAs has also been presented which realizes all five filter functions in all four modes. Macro-model of LM13600/LM13700 and exemplary CMOS OTA have been used to validate the workability of proposed configurations. Sample layout designs have also been included.

Chapter 3 dealt with four new configurations of TOQSOs using three OTAs and three capacitors. All the presented circuits offer independent electronic control of CO and FO. Also, a systematic realization of TOQSO has been presented and based upon this topology, two different TOQSOs employing OTAs and three grounded capacitors have been proposed. Simulation and experimental results have been provided to validate the theory.

In Chapter 4, two new topologies for the realization of TOQSO have been presented. Exemplary TOQSOs based on the proposed topology have also been derived. Systematic realization of low frequency third order sinusoidal oscillators using minimal active and passive components have also been presented in this chapter. Validation of the proposed circuits has been confirmed through experimental results.

Chapter 5 presents new configurations of analog divider and square root circuits using single OTA and two MOSFETs. A four quadrant analog multiplier/two quadrant divider circuit using a single CFOA has also been presented.

Chapter 6 of the thesis presents a summary of the research work presented and some suggestions for future work on the ideas explored.

## **Bibliography**

[1] D. Biolek, R. Senani, V. Biolkova, and Z. Kolka, "Active elements for analog signal processing: classification, review, and new proposals," *Radioengineering*, vol. 17, no. 4, pp. 15–32, 2008.

- [2] H. H. Kuntman and A. Uygur, "New possibilities and trends in circuit design for analog signal processing," in 2012 International Conference on Applied Electronics. IEEE, 2012, pp. 1–9.

- [3] H. Kuntman, "New trends in circuit design for analog signal processing," in 2011 7th International Conference on Electrical and Electronics Engineering (ELECO). IEEE, 2011, pp. II–26.

- [4] F. Kaçar, B. Metin, H. Kuntman, and O. Cicekoglu, "A new high-performance CMOS fully differential second-generation current conveyor with application example of biquad filter realisation," *International Journal of Electronics*, vol. 97, no. 5, pp. 499–510, 2010.

- [5] A. Güney, F. Kaçar, and H. Kuntman, "CMOS realization of electronically tunable VDCC based single-input-dual-output filter," AEU-International Journal of Electronics and Communications, vol. 132, p. 153627, 2021.

- [6] F. Kacar, B. Metin, and H. Kuntman, "A new CMOS dual-x second generation current conveyor (DXCCII) with an FDNR circuit application," AEU-International Journal of Electronics and Communications, vol. 64, no. 8, pp. 774–778, 2010.

- [7] E. Alaybeyoğlu and H. Kuntman, "A new implementation of the reconfigurable analog baseband low pass filter with cell-based variable transconductance amplifier," *Analog Integrated Circuits and Signal Processing*, vol. 97, no. 1, pp. 87–96, 2018.

- [8] F. Kacar and H. H. Kuntman, "A new, improved CMOS realization of CDTA and its filter applications," *Turkish Journal of Electrical Engineering & Computer Sciences*, vol. 19, no. 4, pp. 631–642, 2011.

- [9] E. Alaybeyoğlu, A. Güney, M. Altun, and H. Kuntman, "Design of positive feedback driven current-mode amplifiers Z-Copy CDBA and CDTA, and filter

- applications," Analog Integrated Circuits and Signal Processing, vol. 81, no. 1, pp. 109–120, 2014.

- [10] A. Uygur and H. Kuntman, "DTMOS-based 0.4 V ultra low-voltage low-power VDTA design and its application to EEG data processing," *Radioengineering*, vol. 22, no. 2, pp. 458–466, 2013.

- [11] S. Keleş, F. Kaçar, H. Kuntman, and F. Keleş, "A new FGMOS FDCCII and filter applications," *Informacije Midem*, vol. 44, no. 3, pp. 242–253, 2014.

- [12] A. Uygur and H. Kuntman, "A very compact, 0.4 V DTMOS CCII employed in an audio-frequency filter," Analog Integrated Circuits and Signal Processing, vol. 81, no. 1, pp. 89–98, 2014.

- [13] E. ALAYBEYOĞLU and H. H. Kuntman, "A new CMOS ZC-CDTA realization and its filter applications," *Turkish Journal of Electrical Engineering & Computer Sciences*, vol. 24, no. 3, pp. 746–761, 2016.

- [14] I. A. Khan, M. T. Ahmed, and N. Minhaj, "A simple realisation scheme for OTA-C universal biquadratic filter," *International Journal of Electronics*, vol. 72, no. 3, pp. 419–429, 1992.

- [15] J.-W. Horng, "Voltage-mode universal biquadratic filter using two OTAs,"

Active and Passive Electronic Components, vol. 27, pp. 85–89, 2004.

- [16] M. Kumngern and K. Dejhan, "Electronically tunable voltage-mode universal filter with three-input single-output," in 2010 International Conference on Electronic Devices, Systems and Applications. IEEE, 2010, pp. 7–10.

- [17] C. Acar, F. Anday, and H. Kuntman, "On the realization of OTA-C filters," International Journal of Circuit Theory and Applications, vol. 21, no. 4, pp. 331–341, 1993.

- [18] M. Kumngern, B. Knobnob, and K. Dejhan, "Electronically tunable highinput impedance voltage-mode universal biquadratic filter based on simple

- CMOS OTAs," AEU-International Journal of Electronics and Communications, vol. 64, no. 10, pp. 934–939, 2010.

- [19] M. Kumngern and U. Torteanchai, "Voltage-mode MISO OTA-C biquad filter," in 2011 IEEE Symposium on Industrial Electronics and Applications. IEEE, 2011, pp. 79–82.

- [20] G. Singh, D. R. Bhaskar, and D. Prasad, "Three-input one-output voltage-mode MISO-type biquad using OTAs," International Journal of Electronics, Electrical and Computer Systems, vol. 4, pp. 42–347, 2015.

- [21] M. Kumngern and S. Junnapiya, "Tunable voltage-mode multifunction biquadratic filter with three inputs single output using three single-ended OTAs and two capacitors," in 2013 4th International Conference on Intelligent Systems, Modelling and Simulation. IEEE, 2013, pp. 642–645.

- [22] M. Bhanja and B. Ray, "Design of configurable  $g_m$ -C biquadratic filter," Journal of Circuits, Systems and Computers, vol. 26, no. 03, p. 1750036, 2017.

- [23] M. Kumngern, P. Suksaibul, and B. Knobnob, "High-input impedance four-input one-output voltage-mode universal filter using OTAs," in *The 4th Joint International Conference on Information and Communication Technology, Electronic and Electrical Engineering (JICTEE)*. IEEE, 2014, pp. 1–4.

- [24] N. Wattikornsirikul and M. Kumngern, "Three-input one-output voltage-mode universal filter using simple OTAs," in 2014 Twelfth International Conference on ICT and Knowledge Engineering. IEEE, 2014, pp. 28–31.

- [25] B. Knobnob, P. Suksaibul, and M. Kumngern, "Five-input one-output universal filter using simple CMOS OTAs," in 2018 4th International Conference on Electrical, Electronics and System Engineering (ICEESE). IEEE, 2018, pp. 87–90.

- [26] C. Psychalinos, C. Kasimis, and F. Khateb, "Multiple-input single-output universal biquad filter using single output operational transconductance ampli-

- fiers," AEU-International Journal of Electronics and Communications, vol. 93, pp. 360–367, 2018.

- [27] M. Kumngern, P. Suksaibul, and F. Khateb, "Four-input one-output voltage-mode universal filter using simple OTAs," Journal of Circuits, Systems and Computers, vol. 28, no. 05, p. 1950078, 2019.

- [28] S.-F. Wang, H.-P. Chen, Y. Ku, and C.-M. Yang, "A voltage-mode universal filter using five single-ended OTAs with two grounded capacitors and a quadrature oscillator using the voltage-mode universal filter," *Optik*, vol. 192, p. 162950, 2019.

- [29] S. V. Singh, S. Maheshwari, and D. S. Chauhan, "Electronically tunable current/voltage-mode universal biquad filter using CCCCTA," *International Journal of Recent Trends in Engineering and Technology*, vol. 3, no. 3, pp. 71–76, 2010.

- [30] J.-W. Horng, "Current-mode and transimpedance-mode universal biquadratic filter using multiple outputs CCIIs," *Indian Journal of Engineering & Material Sciences*, vol. 17, no. 03, pp. 169–174, 2010.

- [31] F. Kacar, A. Yesil, and H. Kuntman, "Current-mode biquad filters employing single FDCCII," *Radioengineering*, vol. 21, no. 4, pp. 1269–1278, 2012.

- [32] M. Altun, H. Kuntman, S. Minaei, and O. K. Sayin, "Realisation of n thorder current transfer function employing ecciis and application examples," *International journal of electronics*, vol. 96, no. 11, pp. 1115–1126, 2009.

- [33] I. Cevik, B. Metin, N. Herencsar, O. Cicekoglu, and H. H. Kuntman, "Transimpedance type MOS-C bandpass analog filter core circuits," Analog Integrated Circuits and Signal Processing, vol. 106, no. 3, pp. 543–551, 2021.

- [34] A. M. Soliman, "Mixed-mode biquad circuits," Microelectronics Journal, vol. 27, no. 6, pp. 591–594, 1996.

- [35] M. T. Abuelma'atti, "A novel mixed-mode current-controlled current-conveyor-based filter," Active and Passive Electronic Components, vol. 26, no. 3, pp. 185–191, 2003.

- [36] M. T. Abuelma'atti, A. Bentrcia, and S. M. Al-Shahrani, "A novel mixed-mode current-conveyor-based filter," *International Journal of Electronics*, vol. 91, no. 3, pp. 191–197, 2004.

- [37] M. T. Abuelma'atti and A. Bentrcia, "A novel mixed-mode CCII-based filter,"

Active and Passive Electronic Components, vol. 27, pp. 197–205, 2004.

- [38] N. Pandey, S. K. Paul, A. Bhattacharyya, and J. SB, "A new mixed mode biquad using reduced number of active and passive elements," *IEICE Electronics Express*, vol. 3, no. 6, pp. 115–121, 2006.

- [39] M. Siripruchyanun and W. Jaikla, "Three-input single-output electronically controllable dual-mode universal biquad filter using DO-CCCIIs," *Active and Passive Electronic Components*, vol. 2007, 2007.

- [40] L. Zhijun, "Mixed-mode universal filter using MCCCII," AEU-International Journal of Electronics and Communications, vol. 63, no. 12, pp. 1072–1075, 2009.

- [41] N. Pandey and S. K. Paul, "Mixed mode universal filter," Journal of Circuits, Systems and Computers, vol. 22, no. 01, p. 1250064, 2013.

- [42] D. Singh and N. Afzal, "Digitally programmable current-conveyor based mixed-mode universal filter," *International Journal of Electronics Letters*, vol. 3, no. 3, pp. 170–185, 2015.

- [43] C.-M. Chang, C.-N. Lee, C.-L. Hou, J.-W. Horng, and C. K. Tu, "High-order DDCC-based general mixed-mode universal filter," *IEE Proceedings-Circuits*, *Devices and Systems*, vol. 153, no. 5, pp. 511–516, 2006.

- [44] C.-N. Lee, "Fully cascadable mixed-mode universal filter biquad using DD-CCs and grounded passive components," *Journal of Circuits, Systems, and Computers*, vol. 20, no. 04, pp. 607–620, 2011.

- [45] W.-B. Liao and J.-C. Gu, "Simo type universal mixed-mode biquadratic filter," Indian Journal of Engineering & Material Sciences, vol. 18, no. 06, pp. 443–448, 2011.

- [46] C.-N. Lee and C.-M. Chang, "Single FDCCII-based mixed-mode biquad filter with eight outputs," AEU-International Journal of Electronics and Communications, vol. 63, no. 9, pp. 736–742, 2009.

- [47] A. M. Soliman, "Modified mixed-mode universal filters using DVCC," *Journal of Active and Passive Electronic Devices*, vol. 6, pp. 129–139, 2011.

- [48] C.-N. Lee, "Mixed-mode universal biquadratic filter with no need of matching conditions," *Journal of Circuits, Systems and Computers*, vol. 25, no. 09, p. 1650106, 2016.

- [49] S. Minaei and M. A. Ibrahim, "A mixed-mode khn-biquad using DVCC and grounded passive elements suitable for direct cascading," *International Jour*nal of Circuit Theory and Applications, vol. 37, no. 7, pp. 793–810, 2009.

- [50] C.-N. Lee, "Independently tunable mixed-mode universal biquad filter with versatile input/output functions," AEU-International Journal of Electronics and Communications, vol. 70, no. 8, pp. 1006–1019, 2016.

- [51] E. Yuce and S. Tokat, "Design and stability analysis of mixed-mode filters containing only grounded capacitors," *Journal of Circuits, Systems, and Com*puters, vol. 19, no. 06, pp. 1345–1363, 2010.

- [52] S. V. Singh, S. Maheshwari, and D. S. Chauhan, "Novel electronically tunable mixed-mode biquad filter," in *Electronics and Signal Processing*. Springer, 2011, pp. 735–742.

- [53] S. Maheshwari, S. V. Singh, and D. S. Chauhan, "Electronically tunable low-voltage mixed-mode universal biquad filter," *IET Circuits, Devices & Systems*, vol. 5, no. 3, pp. 149–158, 2011.

- [54] S. V. Singh, R. S. Tomar, and D. S. Chauhan, "A new electronically tunable universal mixed-mode biquad filter," *Journal of Engineering Research*, vol. 2, no. 4, pp. 1–21, 2016.

- [55] A. Yeşil and F. Kaçar, "Electronically tunable resistorless mixed mode biquad filters," *Radioengineering*, vol. 22, no. 4, pp. 1016–1025, 2013.

- [56] M. T. Abuelma'atti and A. Bentrcia, "A novel mixed-mode OTA-C universal filter," *International Journal of Electronics*, vol. 92, no. 7, pp. 375–383, 2005.

- [57] D. R. Bhaskar, A. K. Singh, R. K. Sharma, and R. Senani, "New OTA-C universal current-mode/trans-admittance biquads," *IEICE Electronics Express*, vol. 2, no. 1, pp. 8–13, 2005.

- [58] M. A. Ibrahim, "Design and analysis of a mixed-mode universal filter using dual-output operational transconductance amplifiers (DO-OTAs)," in 2008 International Conference on Computer and Communication Engineering. IEEE, 2008, pp. 915–918.

- [59] C. N. Lee and C. M. Chang, "High-order mixed-mode OTA-C universal filter," AEU-International Journal of Electronics and Communications, vol. 63, no. 6, pp. 517–521, 2009.

- [60] H.-P. Chen, Y.-Z. Liao, and W.-T. Lee, "Tunable mixed-mode OTA-C universal filter," Analog Integrated Circuits and Signal Processing, vol. 58, no. 2, pp. 135–141, 2009.

- [61] C. N. Lee, "Multiple-mode OTA-C universal biquad filters," Circuits, Systems and Signal Processing, vol. 29, no. 2, pp. 263–274, 2010.

- [62] M. Parvizi, "Design of a new low power MISO multi-mode universal biquad OTA-C filter," *International Journal of Electronics*, vol. 106, no. 3, pp. 440– 454, 2019.

- [63] C. N. Lee, "High-order multiple-mode and transadmittance-mode OTA-C universal filters," *Journal of Circuits, Systems, and Computers*, vol. 21, no. 05, p. 1250048, 2012.

- [64] M. Atasoyu, B. Metin, H. Kuntman, and O. Cicekoglu, "Simple realization of a third order Butterworth filter with MOS-only technique," AEU-International Journal of Electronics and Communications, vol. 81, pp. 205–208, 2017.

- [65] E. Arslan, B. Metin, H. Kuntman, and O. Cicekoglu, "MOS-only second order current-mode LP/BP filter," Analog Integrated Circuits and Signal Processing, vol. 74, no. 1, pp. 105–109, 2013.

- [66] A. Yesil, D. Ozenli, E. Arslan, and H. Kuntman, "Current mode single-input multi-output MOSFET-only filter," AEU-International Journal of Electronics and Communications, vol. 80, pp. 157–164, 2017.

- [67] A. Uygur, B. Metin, H. Kuntman, and O. Cicekoglu, "Current mode MOSFET-only third order butterworth low pass filter with dtmos tuning technique," Analog Integrated Circuits and Signal Processing, vol. 89, no. 3, pp. 645–654, 2016.

- [68] D. Ozenli, E. Alaybeyoglu, H. Kuntman, and O. Cicekoglu, "MOSFET-Only filter design automation based on polynomial regression with exemplary circuits," AEU-International Journal of Electronics and Communications, vol. 84, pp. 342–354, 2018.

- [69] D. Ozenli and H. H. Kuntman, "A novel low power MOSFET-C band pass filter for low frequency applications with subthreshold models based on polynomial regression," Analog Integrated Circuits and Signal Processing, vol. 97, no. 1, pp. 97–105, 2018.

- [70] E. Alaybeyoğlu and H. Kuntman, "New realization methods of frequency agile filters for encrypted communications and multi-standard transceivers," in 2017 International Conference on Infocom Technologies and Unmanned Systems (Trends and Future Directions)(ICTUS). IEEE, 2017, pp. 99–112.

- [71] —, "CMOS implementations of VDTA based frequency agile filters for encrypted communications," *Analog Integrated Circuits and Signal Processing*, vol. 89, no. 3, pp. 675–684, 2016.

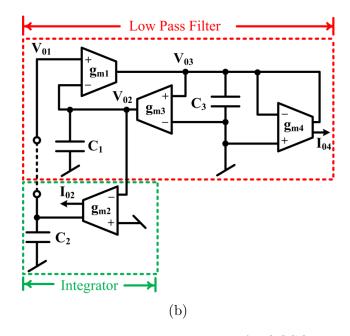

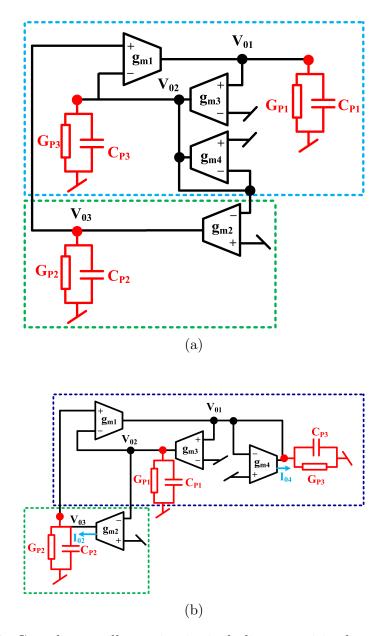

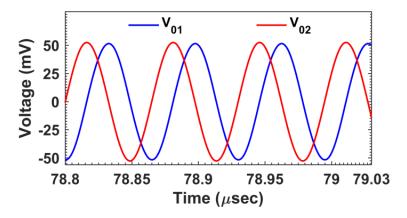

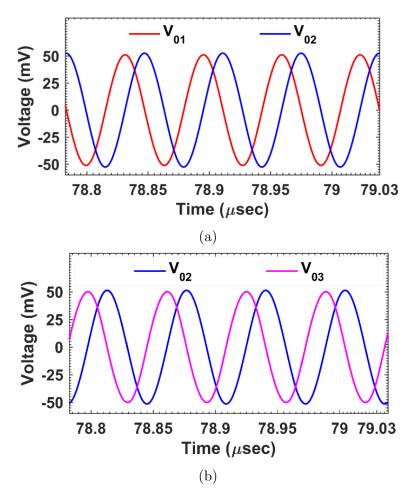

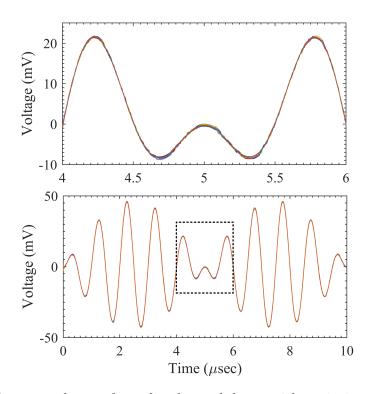

- [72] M. Atasoyu, B. M. Metin, H. Kuntman, and N. Herencsar, "New current-mode class 1 frequency-agile filter for multi protocol GPS application," *Elektronika* ir *Elektrotechnika*, vol. 21, no. 5, pp. 35–39, 2015.