### Technological Computer Aided Design and Simulation of Novel Ferroelectric-Dual Material Oxide Stack-Double Gate FET

A DISSERTATION REPORT

SUBMITTED IN PARTIAL FULFILLMENT OF THE REQUIREMENTS

FOR THE AWARD OF THE DEGREE

OF

MASTER OF SCIENCE

IN

**PHYSICS**

Submitted by

ISHA DAHIYA (2K19/MSCPHY/07)

Under the supervision of

DR. RISHU CHAUJAR

**Associate Professor**

DEPARTMENT OF APPLIED PHYSICS

### **DELHI TECHNOLOGICAL UNIVERSITY**

(Formerly Delhi College of Engineering)

Bawana Road, Delhi-110042

MAY, 2021

DEPARTMENT OF APPLIED PHYSICS

**DELHI TECHNOLOGICAL UNIVERSITY**

(Formerly Delhi College of Engineering)

Bawana Road, Delhi-110042

**CANDIDATE'S DECLARATION**

I, ISHA DAHIYA (2K19/MSCPHY/07), student of M.Sc. (Physics), hereby declare that the

project Dissertation titled "TECHNOLOGICAL COMPUTER AIDED DESIGN AND

SIMULATION OF NOVEL FERROELECTRIC-DUAL MATERIAL OXIDE STACK-

DOUBLE GATE FET" which is submitted by me to the Department of Applied Physics,

Delhi Technological University, Delhi in partial fulfilment of the requirement for the award

of the degree of Master of Science, is original and not copied from any source without proper

citation. This work has not previously formed the basis for the award of any Degree, Diploma

Associateship, Fellowship or other similar title or recognition.

Place: Sonipat

Date: May 29, 2021

ISHA DAHIYA

2

## DEPARTMENT OF APPLIED PHYSICS

**DELHI TECHNOLOGICAL UNIVERSITY**

(Formerly Delhi College of Engineering)

Bawana Road, Delhi-110042

**CERTIFICATE**

I hereby certify that the Project Dissertation titled "TECHNOLOGICAL COMPUTER

AIDED DESIGN AND SIMULATION OF NOVEL FERROELECTRIC-DUAL

MATERIAL OXIDE STACK-DOUBLE GATE FET" which is submitted by ISHA

DAHIYA (2K19/MSCPHY/07) Department of Applied Physics, Delhi Technological

University, Delhi in partial fulfilment of the requirement for the award of the degree of

Master of Science, is a record of the project work carried out by the student under my

supervision. To the best of my knowledge this work has not been submitted in part or full for

any Degree or Diploma to this University or elsewhere.

Place:

Date:

DR. RISHU CHAUJAR

**SUPERVISOR**

**Associate Professor**

**Department of Applied Physics**

**Delhi Technological University**

3

### **Acceptance** Letter

6th International Conference on Communication and Electronics Systems (ICCES 2021)

8-10, July 2021 | icoers.org/2021/ | iccces2019@gmail.com

#### Acceptance Letter

: ICCES158 Paper ID

: Analog Analysis of Novel Ferroelectric-Dual Material Oxide Manuscript Title

Stack-Double Gate FET

Author/s : Isha Dahiya, Rishu Chaujar, Department of Applied Physics,

Delhi Technological University, Main Bawana Road, Delhi, 110042, India.

Subject: Acceptance to the International Conference on Communication and Electronics Systems ICCES 2021- 8-10, July 2021

On behalf of the Conference committee, I would like to congratulate you on your to the ICCES 2021 IEEE Conference, which will be held from 8-10, July 2021 at PPG Institute of Technology, Coimbatore, India. You have been selected to deliver your oral presentation at the International Conference on Communication and Electronics Systems.

ICCES 2021 is an internationally-recognized IEEE Xplore IEEE conference, which dedicated solely for publication in IEEE provides SCOPUS with all of the IEEE Xplore digital library. Please visit the conference website for further updates [ icoecs.org/2021].

As a result of the review and results, we are pleased inform that you can now submit the full-length paper for inclusion into the IEEE Xplore ICCES proceedings. We appreciate if you could send the final version of your research paper at your earliest convenience, in order to ensure the timely publication. When submitting your final paper, please highlight the changes made according to the review comments.

Yours sincerely, V.Bil

Dr. V. Bindhu

[ICCES 2021 - Conference Chair]

Professor and Head, ECE Dept, PPG Institute of Technology Coimbatore, India

Previous ICCES Publications

ICCES 2020

ICCES 2019 ICCES 2018

ICCES 2017

**PIEEE**

### **Registration for Conference**

### Your Receipt for 6th International **Conference on Communication and Electronics Systems!**

#### Hi Isha Dahiya,

You just purchased 1 ticket(s) for event - 6th International Conference on Communication and Electronics Systems.

Your receipt details are as follows:

Order Id: 400641620313920506 Booking Date: 05/06/2021 20:43(IST)

NAME TYPE PRICE DISCOUNT

Research

Scholars Non Ieee INR 6500.00 Isha Dahiya via NA

members

Grand Total: INR 6500.00

Event Details:

♣ Organizer : ICCCES

: PPG Institute of Technology,pharmacy, Coimbatore, India

**≡** Event 6th International Conference on Communication and Electronics Systems

# DEPARTMENT OF APPLIED PHYSICS DELHI TECHNOLOGICAL UNIVERSITY

(Formerly Delhi College of Engineering)

Bawana Road, Delhi-110042

### **ACKNOWLEDGEMENT**

I would like to convey my special thanks and gratitude towards Dr. Rishu Chaujar, Associate Professor, Department of Applied Physics, Delhi Technological University under whose valuable guidance I have been able to work on this dissertation. While doing this project, I have done a lot of research work and I learnt about so many new things, for that I am always thankful. I am deeply grateful to my family and friends for their continuous support and suggestions in various phases for accomplishing this task.

#### **ABSTRACT**

In this work, the analog performance for Ferroelectric-Dual Material Oxide Stack-Double Gate FET (Fe-DMOS-DG FET) has been assessed and its effectiveness in reducing short channel effects (SCEs) has been analyzed. The derived parameters and results have been analysed in comparison with the conventional bulk MOSFET having same channel length. We are using gate metal comprising of two different materials to have better control over the channel. To reduce the injection of hot carriers, in one case we have used a ferroelectric layer on a thin SiO<sub>2</sub> interface layer, and in another case, we have used a ferroelectric layer on an oxide stack consisting of high k-dielectric and SiO<sub>2</sub> as gate insulator material. Parameters like ON current, OFF current, Id vs. Vg plot, Transconductance vs. Vg plot, threshold voltage, and value of sub-threshold slope are considered. It has been concluded that the new device has less subthreshold current, resulting in a lower subthreshold slope when compared to bulk MOSFET. Also, the electric field and carrier concentration along the channel are investigated, and it has been found that the novel device enhances carrier transport in the channel. The silvaco ATLAS device simulation software is used to do the numerical calculations in order to validate the results.

### **CONTENTS**

| I.  |    | Cover Page & Title Page                                        |

|-----|----|----------------------------------------------------------------|

| 2.  |    | Candidate's Declaration                                        |

| 3.  |    | Certificate3                                                   |

| 4.  |    | Acceptance Letter4                                             |

| 5.  |    | Registration of conference5                                    |

| 6.  |    | Acknowledgement6                                               |

| 7.  |    | Abstract7                                                      |

| 8.  |    | Contents8-9                                                    |

| 9.  |    | List of Figures                                                |

| 10. |    | List of Tables                                                 |

| 11. |    | List of Symbols, Abbreviations and Nomenclature12              |

| 12. |    | Chapters                                                       |

|     | 1. | INTRODUCTION13                                                 |

|     |    | 1.1 Motivation                                                 |

|     |    | 1.2 Metal-oxide-semiconductor field effect transistor (MOSFET) |

|     |    | 1.2.1 MOSFET operation                                         |

|     |    | 1.2.2 Enhancement mode                                         |

|     |    | 1.2.3 Depletion mode                                           |

|     |    | 1.3 Drawback and limitations of conventional MOSFET            |

|     |    | 1.3.1 Short channel effect                                     |

|     |    | 1.3.2 Velocity saturation                                      |

|     |    | 1.3.3 Drain induced barrier lowering (DIBL)                    |

|     |    | 1.3.4 Surface scattering                                       |

|     |    | 1.3.5 Hot carrier effects                                      |

|     |    | 1.4 Double Gate FET                                            |

|     |    | 1.4.1 Modifications in Double gate FET                         |

|     |    | 1.4.2 Problems with Double gate FET structure                  |

|     |    | 1.5 Ferroelectric FET                                          |

|     |    | 1.5.1 Ferroelectric material                                   |

|     |    | 1.5.2 Fe-FET device and operation                              |

|     |    | •                                                              |

|     | 2. | Simulation of MOSFET and FE-FET in ATLAS software21            |

|     |    | 2.1 ATLAS overview                                             |

|     |    | 2.2 Device Description                                         |

|     |    |                                                                |

|     | 3. | 1100 0110 0110 2 10 0 00 0 10 11 11 11 11 11 11 11 11 11       |

|     |    | 3.1 Id vs Vg plot (Transfer characteristics)                   |

|     |    | 3.2 Transconductance                                           |

|     |    | 3.3 Electrical characteristics                                 |

|     |    | 3.4 Electric field                                             |

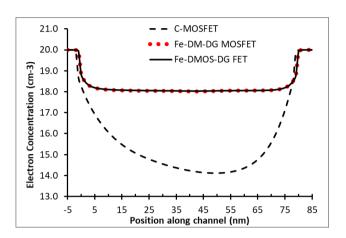

#### 3.5 Electron concentration

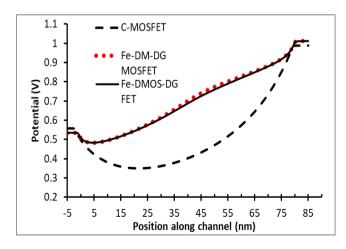

#### 3.6 Potential

| 11. Conclusion        | 31    |

|-----------------------|-------|

| 12. References.       | 32-33 |

| 13. Plagiarism Report | 34-35 |

| 14. Conference paper  | 36-40 |

### **List of Figures**

| S.no. | Figure                                                                 |  |  |  |  |  |

|-------|------------------------------------------------------------------------|--|--|--|--|--|

| 1     | N-MOS structure                                                        |  |  |  |  |  |

| 2     | Representation of Hot carrier effects                                  |  |  |  |  |  |

| 3     | Schematic of Double gate MOSFET                                        |  |  |  |  |  |

| 4     | Hysteresis loop for ferroelectric material                             |  |  |  |  |  |

| 5     | Simulation flow in ATLAS                                               |  |  |  |  |  |

| 6     | Schematic structure of Fe-DM-DG MOSFET                                 |  |  |  |  |  |

| 7     | Schematic structure of Fe-DMOS-DG FET                                  |  |  |  |  |  |

| 8     | Drain Current vs. Gate Voltage (transfer characteristics) obtained for |  |  |  |  |  |

|       | drain voltage=0.5V                                                     |  |  |  |  |  |

| 9     | Variation of electric field along the channel for C-MOSFET, Fe-DM-     |  |  |  |  |  |

|       | DG MOSFET and Fe-DMOS-DG FET                                           |  |  |  |  |  |

| 10    | Transconductance vs. Gate voltage                                      |  |  |  |  |  |

| 11    | Variation of electron concentration along the channel for C-MOSFET,    |  |  |  |  |  |

|       | Fe-DM-DG MOSFET and Fe-DMOS-DG FET                                     |  |  |  |  |  |

| 12    | Variation of potential (V) along the channel                           |  |  |  |  |  |

### **List of Table**

| S.no. | Table                                            |

|-------|--------------------------------------------------|

| 1     | Order of commands in ATLAS                       |

| 2     | Electrical characteristics extracted at Vds=0.5V |

### List of Symbols, abbreviations and Nomenclature

CMOS Complementary metal oxide semiconductor

CLM Channel length modulation

MOSFET Metal-oxide-semiconductor field effect transistor

DG Double gate

SCE Short channel effect

DM Dual material

Fe-FET Ferroelectric field effect transistor

Fe-DM-DG MOSFET Ferroelectric-Dual Material-Double Gate MOSFET

Fe-DMOS-DG FET Ferroelectric-Dual Material Oxide Stack-Double Gate FET

DIBL Drain induced barrier lowering

#### 1. Introduction

The continuous reduction of device size has allowed considerable technical advancement, resulting in denser, faster, and more practical integrated circuits. Developing devices that can perform massive computations while having a limited footprint (in terms of size) has been a significant motivator. Most of this has been made possible by the fact that the size of ordinary MOSFET has diminished by a magnitude of around 20 over the last two decades, and the MOS transistors that are being fabricated these days have a channel of length less than 100 nm. [1]. The elementary planar structure of the MOSFET has stayed mainly unaltered but its size has decreased by many orders of magnitude in the last three decades. These days the numbers of components/devices on an integrated circuit are increasing exponentially and the law that explains this trend is Moore's Law. Moore in 1965 predicted this trend and gave a law, according to which the number of transistors in an integrated circuit doubles after two years. This law seems to be applicable since then. In conventional MOSFET, short channel effects like injection of hot carriers into insulator layer, charge carriers' velocity saturation, drain induced barrier lowering (DIBL), carrier multiplication due to impact ionization hence causing various leakage currents and surface scattering have increased due to downscaling of the device. Therefore, the significant issue faced these days during transistor development is the reduction of short channel effects while improving the device's performance. For low-power and high-speed processes, the subthreshold swing and the DIBL should be as small as possible. However, at room temperature, the bulk MOSFET subthreshold swing has a theoretical limit of 60 mV/dec [11].

#### 1.1 Motivation

Various alternatives, including the multiple-gate structure and advanced technologies such as gate oxide engineering, gate work function engineering, and so on, are being used these days to suppress short channel effects. [2]-[3]. Out of the various gate geometries, double gate geometry is the most promising. Two gates offer better controllability from both sides of the channel, subsequently resulting in stronger switching signals [4]. The short channel effect suppression capability of such a Dual Material Gate (DMG) design has been discovered to be very effective [5]. In gate workfunction engineering, the gate metal of appropriate work function is used in such a way that charge carriers are accelerated rapidly in the channel [2].

The material's workfunction at the source side is higher in a dual material gate configuration than the workfunction of the gate electrode near the source. Gate stack architecture is being incorporated to reduce high fringing fields and gate tunneling [9]. The most prominent motive in current literature and system design discussions is to improve switching speed and attain ultra-low power operation. The threshold voltage regulates the lower bound of the operating voltage, and in a traditional bulk MOSFET, lowering the threshold voltage increases the off-state current (Ioff), and hence the static power consumption [6]. To minimize power consumption, abrupt-turn-on devices are being extensively researched. Also, ferroelectric based insulator design is found to improve the short channel immunity in conventional dual metal gate device [13] and use of high-k dielectric as interfacial layer improves endurance and retention in FeFET devices during operation at lower switching voltages [14]. Hence, it is anticipated that the use ferroelectric as insulator in dual gate structure along with an interface layer will improve device performance as compared to conventional MOSFET structure.

#### 1.2 Metal Oxide Semiconductor Field Effect Transistors (MOSFETs)

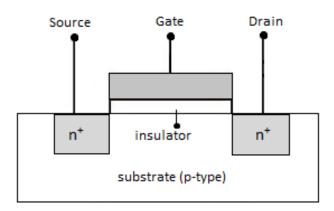

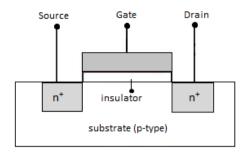

MOSFET consists of two heavily doped regions, source and drain, separated by a mildly doped substrate. The schematic of n-MOSFET is represented in figure 1. The voltage applied to the gate terminal generates the channel by inversion of the semiconductor beneath the gate terminal. The distance between the source region and drain region is called channel length. Inside the transistor, two electric fields govern its operation: the vertical electric field generated due to applied gate voltage and lateral electric field because of source-to-drain voltage. A dielectric material is needed to insulate the gate contact from the conducting channel; generally, SiO<sub>2</sub> is used. Since flow of current is limited to 10-100 Å at the semiconductor's surface, the bulk of the semiconductor, known as the substrate, is usually inactive [1].

Figure 1. N-MOS structure

#### 1.2.1 MOSFET Operation

The MOS transistor's operation is dependent on the MOS capacitor, which consists of gate metal contact, the substrate and the dielectric insulator that separates both of them. The applied voltage will induce charges in the metal and the counter charges in the interfacial layer of the semiconductor, as we would anticipate in the metal plates of a traditional parallel plate capacitor. The ability of the MOSFET to generate and modify a conducting layer consisting of minority carriers at the semiconductor—oxide interface is the fundamental of its operation. On applying voltage to the gate contact, charges are induced at the silicon-insulator interface in the semiconductor. For n-MOS transistor, p-type substrate is used, therefore on applying Vg>0, holes start moving away from the Si-Insulator interface, forming a depletion layer that consists of immovable negative charge carriers. On further increasing the gate voltage, the depletion layer reaches the substrate further, and for a particular gate voltage, i.e. for the threshold voltage, electrons start injecting from the source to the drain, hence forming a channel. For p-MOS transistor, channel formed is of holes for n-type substrate. According to the mode of operation, MOSFETs are categorized in two types.

#### 1.2.2 Enhancement Mode

In enhancement-mode MOSFET, a conducting channel doesn't exist in-between source and drain region when no voltage is given to the gate electrode. To induce the channel, a certain minimum gate voltage must be applied which will turn the device on.

#### 1.2.3 Depletion Mode

In depletion-mode MOSFET, a conducting channel (inversion layer) is present even when no gate voltage has been applied. Threshold voltage in this case, will turn the device off.

#### 1.3 Drawbacks and Limitations of Conventional MOSFETs

Conventional bulk MOSFETs have been a fundamental component for very large scale integration in semiconductor technology. However, as its size is reduced to nano-scale, various short channel effects poses a limitation on the size of the device. Due to the reduction of the MOS transistor's size, there is an appreciable gate-source and gate-drain overlap causing edge effects leading to an increase in longitudinal field, which was negligible compared to the perpendicular field in long channel transistor. Various parasitic capacitances also increases making the device unsustainable, consumes more energy along with increase in the time delay. Downscaling of MOSFET requires proper scaling of the gate length and width, thickness of oxide layer along with the other dimensions.

#### 1.3.1 Short Channel Effects (SCEs)

In long channel MOSFET, electrostatics of the channel of device are controlled by gate electrode but in short channel MOSFET source and drain also appreciably controls the electrostatics of channel. Also, Drain current increases on decreasing the channel length which makes switching easier but this also decreases the threshold voltage to a greater extent.

#### 1.3.2 Velocity Saturation

In short channel device, value of lateral electric field increases which leads to saturation of velocity for charge carriers at about 10<sup>7</sup> cm/sec. Consequently, the obtained value of device current is lesser than the drain current value expected from mobility model.

#### 1.3.3 Drain Induced Barrier Lowering (DIBL)

This is a phenomenon in which threshold voltage is reduced for the applied high value of drain voltage (Vds). The potential barrier between the source region and channel in reduced as Vds is increased. DIBL is determined as  $|\Delta V th|/|\Delta V ds|$  for Vds changing from 0.05V to 1.0V.

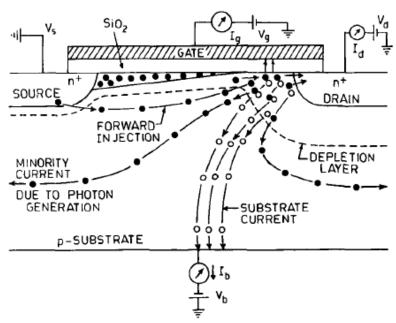

Figure 2. Representation of Hot carrier effects

### 1.3.4 Surface Scattering

The inversion layer formed in the device is confined to a very narrow region in the silicon near the silicon-insulator interface. Due to the increased value of lateral electric field inside the channel of short channel MOSFET and also the electric field applied vertically, charge carriers experience collision among them while accelerating towards the drain region causing degradation of mobility. This is known as surface scattering which lead to reduction in drain current.

#### 1.3.5 Hot Carrier Effects

In short channel device, value of electric increases in the channel regions causing the carriers to move at high velocity. This acquired high kinetic energy could cause impact ionization which ultimately leads to degradation of insulator layer causing gate leakage current. These

high energy charge carriers are called hot-carriers. These can also lead to undesirable substrate current.

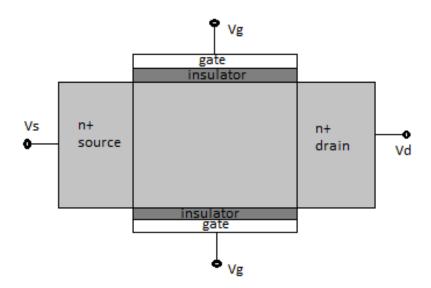

#### 1.4 Double Gate FETs

To overcome the shortcomings of the conventional MOSFET, double gate structure is found to be effective. Schematic of Double gate MOSFET is shown in figure 3. In this, the body is replaced by a back gate which reduces the leakage current and size is also reduced. Two gates offer better controllability from both sides of the channel, subsequently resulting in stronger switching signals. Operation of double gate MOSFET is similar to conventional MOSFET; the applied gate voltage forward biases the source-body junction hence causing the movement of carriers into the channel towards drain.

Figure 3. Schematic of Double gate MOSFET

#### 1.4.1 Modifications in Double Gate Structure

Variations used in double gate FET structure include the use of Dual Metal or Triple Metal gate. By using gate material consisting of a combination of metal having different workfunction, we can have more control over the channel. Using a metal of higher workfunction near the source causes the carriers to move speedily in the channel; and to slow down the carriers near the drain, metal of lower workfunction is used for the gate. This reduces the injection of hot carriers in the insulator layer.

#### 1.4.2 Problems with Double Gate FET structure

While dual gate FET structure improves device performance like increased drain current and transconductance, better short channel reliability; at the same time, the misalignment of two gates can degrade device performance as compared to single gate structure. Overlapping of any of gate electrode with source or drain can affect the device properties, as the overlapped part of source or drain is now controlled by the gate. The deviation from expected behaviour caused by the misalignment of gates can come from either the overlapped regions or non-overlapped regions. In this project, symmetric dual gate structure is considered.

#### 1.5 Ferroelectric Field Effect Transistor

The main difference between ferroelectric FETs and MOSFETs is found in the gate stack of the device. MOSFETs have an insulating dielectric layer between the gate and the channel, typically SiO<sub>2</sub>, whereas FeFETs use ferroelectric materials.

#### 1.5.1 Ferroelectric materials

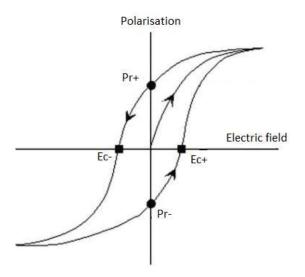

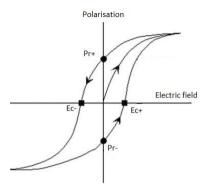

Ferroelectric materials are the material that becomes spontaneously polarized on application of electric field. All materials experience polarization on application of external electric field, which is proportional to the intensity of the applied field. However, ferroelectric dielectric crystals show a spontaneous electric polarization and have two stable polarized states, and polarization state can be reversed using electric field. These materials are ideal candidates for memory applications because of their switching efficiency. Digital bits, 0 or 1, are stored using the direction of spontaneous polarization, and the memory is non-volatile and electrically switchable. Typical hysteretic response of ferroelectric material is as shown figure 4. On the y-axis, the remnant polarization charges, denoted by PR+ and PR-, are shown, and on the x-axis, Ec+ and Ec- are marked, which represents the coercive fields.

Figure 4. Hysteresis loop for ferroelectric material

#### 1.5.2 FeFET device and operation

Ferroelectric films are currently being studied in order to achieve ultra-low power operation in devices that incorporate them. When doped with La, Sr, Si, Gd, Zr, Y, and Al, CMOScompliant HfO<sub>2</sub>-based films exhibit ferroelectric properties and are also lead-free [7]. Working of ferroelectric FETs is quite similar to MOSFETs', with the primary differences being in the device's gate stack. However, there are specific challenges in interfacing Si and ferroelectrics, like intermixing of the two layers, and regardless of the application, all Fe FETs experience a substantial field drop across the low-k interface layer, raising the power requirement for reversing the polarization while decreasing lifetime [8]. Several buffer layer configurations and alternative gate stack layouts have been using different combinations of metal, ferroelectric and dielectric insulator. However, the immediate deposition of ferroelectric layer over silicon is complicated due to the chemical reaction [10]. Therefore, to shrink the chip's size for artificial intelligence operation, combinations of an oxide layer, a thin ferroelectric material layer, a semiconductor and a fatigue-free electrode should be widely examined [10]. The approach to hysteresis-free FeFET architecture is aligning the positive capacitance of intrinsic MOSFET so as to stabilize the negative capacitance of ferroelectric; and experimentally ferroelectric-dielectric bilayer shows non-hysteretic electrical characteristics [12].

#### 2 Simulation of MOSFET and FeFET in ATLAS software

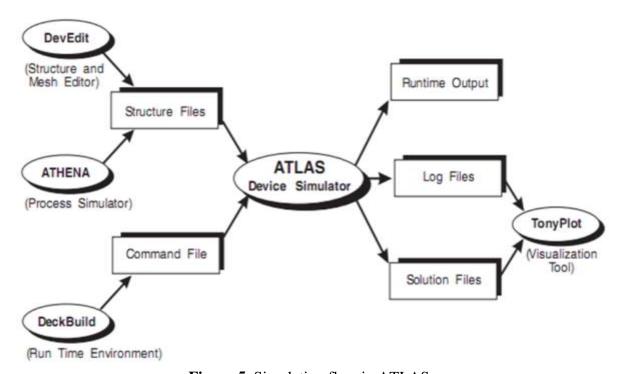

There are various sub-packages in Silvaco for device simulation. They are DevEdit, ATHENA, ATLAS, DeckBuild, TonyPlot. Out of these ATALS is main device simulator and Tonyplot is used to plot the simulation results.

#### 2.2 ATLAS overview

Simulation in ALTLAS is done through an input text file which is written in DeckBuild. The text file comprises information of all the parameters like doping, composition of different regions, biasing of electrodes and physical dimensions of the device. To create a structure, a mesh is defined; and solution of differential equations to find the values of all the required parameters is evaluated at these grid points also called nodes. Program is written in DeckBuild and after loading it in ATLAS, log file and structure files are generated. Sequence followed to write the program is given in the figure 5. The table 1 provides the sequence of commands to be followed in ATLAS.

**Figure 5.** Simulation flow in ATLAS

| Group                                | Statements                                 |

|--------------------------------------|--------------------------------------------|

| 1. Structure Specification ———       | MESH<br>REGION<br>ELECTRODE<br>DOPING      |

| 2. Material Models Specification ——— | MATERIAL<br>MODELS<br>CONTACT<br>INTERFACE |

| 3. Numerical Method Selection ———    | METHOD                                     |

| 4. Solution Specification            | LOG<br>SOLVE<br>LOAD<br>SAVE               |

| 5. Results Analysis                  | EXTRACT<br>TONYPLOT                        |

**Table 1.** Order of commands in ATLAS

Types of input and output files for ATLAS:

- a) Input files

- ATLAS commands written in text file

- structure file made in DevEdit or ATHENA

- b) Output files

- After loading the input, a runtime time output window giving error warnings

- file storing information of current and voltages-log file

- files storing 2D and 3D output data structure file

### 2.3 Device description

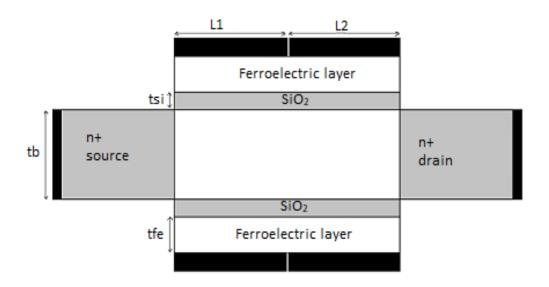

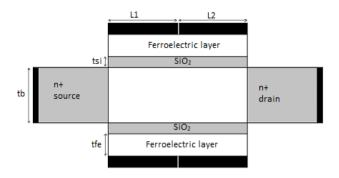

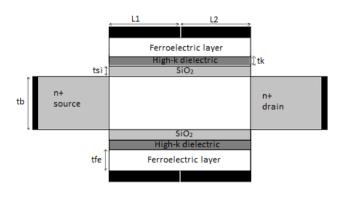

Figure 6. Schematic structure of Fe-DM-DG MOSFET

Figure 6 depicts a cross-sectional illustration of a Ferroelectric-Dual Material-Double Gate MOSFET with ferroelectric material as a gate insulator and SiO<sub>2</sub> as an interface layer. The overall purpose of using an interface layer is to minimize inter-diffusion between the ferroelectric layer and the semiconductor. The thickness assumed for the ferroelectric and SiO<sub>2</sub> layer is 4nm (tfe) and 2nm (tsi), respectively. The simulations are performed for top and bottom gate of length (L1 + L2) 80nm and each gate are divided into two equal parts. Workfunction of gate regions near the source is taken to be 4.8eV and for the parts near the drain, it's 4.4eV. The thickness of the substrate (tb) used is 10nm with uniform doping of 10<sup>18</sup> cm<sup>-3</sup>. The doping of source and drain regions is uniform and value is 10<sup>20</sup> cm<sup>-3</sup>.

For the conventional MOSFET, work function is 4.6eV for gate electrode; substrate thickness is 30nm and the parameters like channel length and source/drain doping are the same as above. Schematic of conventional MOSFET is represented in Figure 1.

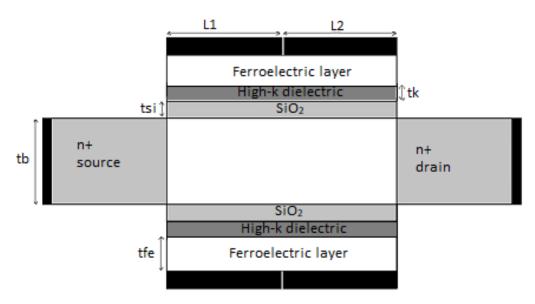

Figure 7 shows the cross-sectional structure of Ferroelectric-Dual Material Oxide Stack-Double Gate FET (Fe-DMOS-DG FET). Except for the gate oxide, which consists of a 1.5nm high-k material layer (tk) with dielectric constant 25, on a 1.5nm thick SiO<sub>2</sub> layer of dielectric constant 3.9, all other parameters are the same as above for Ferroelectric-Dual Material Oxide Stack-Double Gate FET.

**Figure 7.** Schematic structure of Fe-DMOS-DG FET

#### 3 Results

This section presents the performance analysis of Ferroelectric-Dual Material-Double Gate MOSFET (Fe-DM-DG MOSFET) and Ferroelectric-Dual Material Oxide Stack-Double Gate FET (Fe-DMOS-DG FET) in comparison with conventional MOSFET (C-MOSFET).

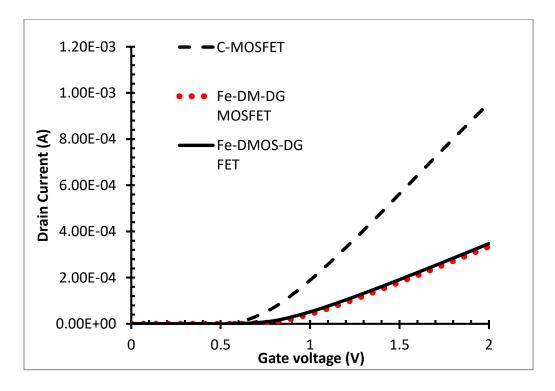

#### 3.1 Transfer Characteristics

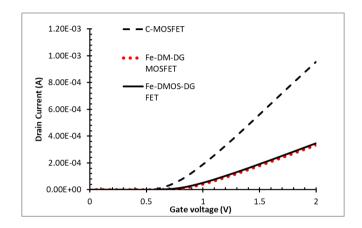

Figure 8 represents the transfer characteristics of the Fe-DM-DG MOSFET, Fe-DMOS-DG FET and C-MOSFET at Vds=0.5V. The threshold voltage for both the devices having ferroelectric material as gate insulator is higher as compared to the conventional MOSFET, which indicates the reduction of OFF state current.

**Figure 8.** Drain Current vs. Gate Voltage (transfer characteristics) obtained for drain voltage=0.5V

#### 3.2 Transconductance

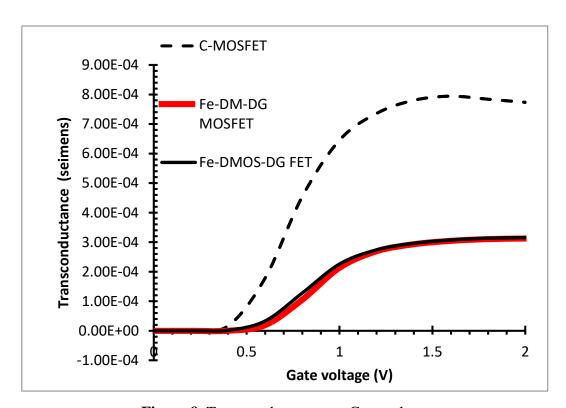

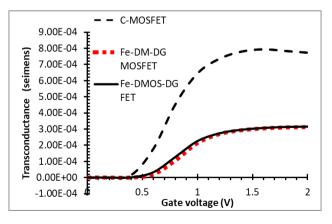

Figure 9 shows transconductance vs. gate voltage plot for the three devices. Gate transconductance is expressed as the ratio of change in the output drain current to change in the applied gate voltage while maintaining the drain and substrate voltages constant. Transconductance is a crucial parameter since it evaluates device gain and controls device switching speed. Devices with high gain can operate at low gate voltages. From the figure, transconductance increases at lower gate voltage; at higher gate voltage, it starts decreasing for C-MOSFET, however for the Fe-DM-DG MOSFET and Fe-DMOS-DG FET transconductance becomes independent of the gate voltage.

Figure 9. Transconductance vs. Gate voltage

#### 3.3 Electrical Characteristics

Table 2 compares electrical characteristics of C-MOSFET, Fe-DM-DG MOSFET and Fe-DMOS-DG FET for drain voltage (Vds) equal to 0.5V. Fe-DM-DG MOSFET gives the lowest off-state current with highest ratio of Ion and Ioff. Both the ferroelectric devices have lower sub-threshold slope values than the conventional MOSFET; and threshold voltage increases implying better short channel immunity. However, a minimal increase in values of DIBL can be seen for both the new devices, which is defined as  $|\Delta V th|/|\Delta V ds|$ . The values of Vth at Vds= 0.05V and 1.0V are taken to derive  $\Delta V th$  in this study.

| Model              | Sub-Threshold<br>slope (V/dec) | Vth      | Ion(Vg=1V) | Ioff(Vg=0V) | Ion/Ioff | DIBL     |

|--------------------|--------------------------------|----------|------------|-------------|----------|----------|

| C-MOSFET           | 0.0929308                      | 0.541862 | 0.000189   | 3.56E-10    | 530834   | 0.473247 |

| Fe-DM-DG<br>MOSFET | 0.0785244                      | 0.679169 | 4.24E-05   | 6.01E-15    | 7.06E+09 | 0.494781 |

| Fe-DMOS-<br>DG FET | 0.0853542                      | 0.648264 | 5.17E-05   | 1.08E-13    | 4.79E+08 | 0.504489 |

**Table 2.** Electrical characteristics extracted at Vds=0.5V

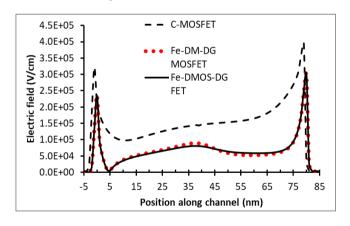

#### 3.4 Electric Field

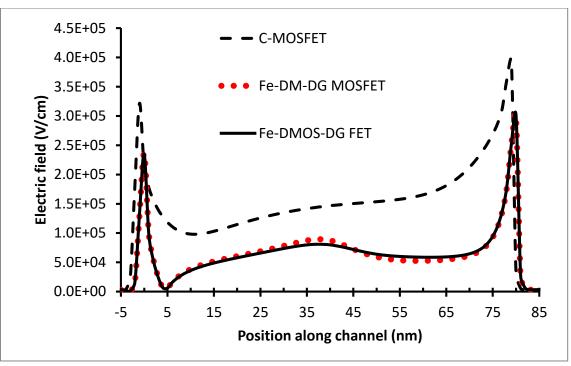

From the figure 10, in C-MOSFET, the electric field in the channel is higher as compared to the Fe-DM-DG MOSFET and Fe-DMOS-DG FET. The high value of field towards the drain terminal of the device, which leads to pronounced hot carrier effects in conventional MOSFET, has been decreased with the introduction of a ferroelectric layer as gate insulator. No significant impact of introducing an oxide stack in place of the SiO<sub>2</sub> layer in Fe-DM-DG MOSFET is observed on the electric field variation along the channel.

**Figure 10.** Variation of electric field along the channel for C-MOSFET, Fe-DM-DG MOSFET and Fe-DMOS-DG FET

#### 3.5 Electron Concertation

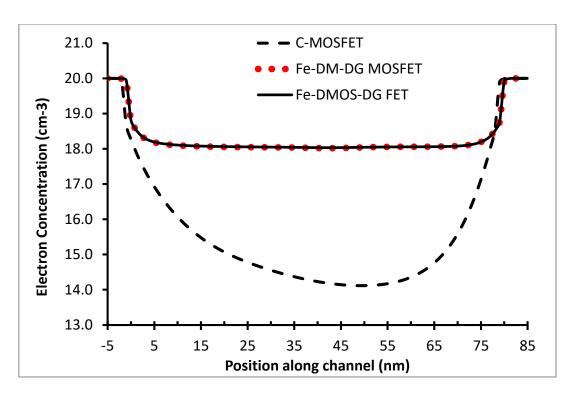

From Figure 11, it is observed that the carriers are distributed non-uniformly in the C-MOSFET, which leads to mobility ( $\mu$ ) degradation, and the exact thickness of the conducting channel could be challenging to determine. Meanwhile, the gate controllability over the carriers in the channel would be reduced, and high carrier concentration towards the drain side could increase the hot carrier effects in the device. The introduction of ferroelectric layer has improved the electron density towards the source end, and the carrier concentration becomes more uniform along the channel compared to the C-MOSFET. However, variation of electron concentration is the same for Fe-DM-DG MOSFET and Fe-DMOS-DG FET.

**Figure 11.** Variation of electron concentration along the channel for C-MOSFET, Fe-DM-DG MOSFET and Fe-DMOS-DG FET

#### 3.6 Potential

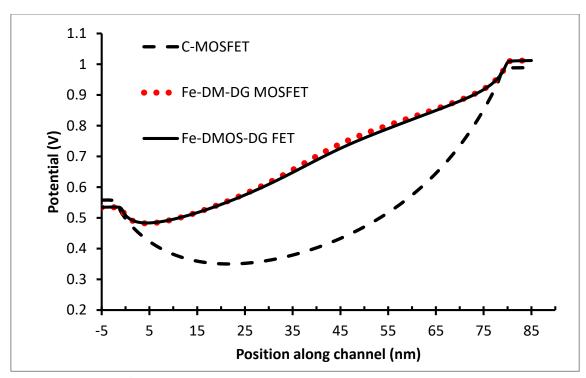

Figure 12 shows potential distribution along the channel for three of the devices. In C-MOSFET, there is a formation of potential well which spans whole of the channel length, whereas in both of the ferroelectric devices, a potential barrier near the source is formed because of negative capacitance effect of ferroelectric layer. The higher potential towards source in Fe-DM-DG MOSFET and Fe-DMOS-DG FET causes injection of carrier from the source into channel at higher speed as compared to C-MOSFET. This results in improved short channel immunity.

Figure 12. Variation of potential (V) along the channel

#### **CONCLUSION**

A 2-D analytical model for Ferroelectric-Dual Material-Double Gate MOSFET (Fe-DM-DG MOSFET) and Ferroelectric-Dual Material Oxide Stack-Double Gate FET (Fe-DMOS-DG FET) has been developed to diminish short-channel effects (SCEs) in nano-scale bulk MOSFETs, as well as to improve device reliability. Fe-DM-DG MOSFET improves nearly all of the parameters such as off current, sub-threshold slope, variation of carrier concentration along channel when compared to conventional short channel MOSFET; and is found to be effective for reduction of HCEs. Further, the parameters like variation of electric field, potential and carrier concentration along the channel obtained for Fe-DM-DG MOSFET and Fe-DMOS-DG FET are nearly identical. Thus, it has been illustrated that incorporating a ferroelectric layer along with the SiO<sub>2</sub> layer as insulator for dual metal gate electrode configuration improves hot carrier reliability and short channel immunity, resulting in improved performance and better carrier transport efficiency when compared to conventional bulk MOSFET design.

Dual Gate FETs have assuring future in VLSI and IC design as they have notably small structures. Other advantages include less power consumption, high reliability, and mostly nano-scale size, making them very valuable for CMOS circuits. Incorporating ferroelectric material and Dual Gate structure in FETs can provide promising results in fast programming, high ON/OFF ratio, low power dissipation, and other applications, which makes them suitable to be used as an electronics synapse.

#### References

- [1] Arora, Narain, ed. Mosfet modeling for VLSI simulation: theory and practice. World Scientific, 2007.

- [2] Oh, Sang-Hyun, Don Monroe, and J. M. Hergenrother. "Analytic description of short-channel effects in fully-depleted double-gate and cylindrical, surrounding-gate MOSFETs." *IEEE electron device letters* 21, no. 9 (2000): 445-447.

- [3] Long, Wei, and Ken K. Chin. "Dual material gate field effect transistor (DMGFET)." In *International Electron Devices Meeting. IEDM Technical Digest*, pp. 549-552. IEEE, 1997.

- [4] Jung, Hak Kee, and Sima Dimitrijev. "Analysis of subthreshold carrier transport for ultimate DGMOSFET." *IEEE transactions on electron devices* 53, no. 4 (2006): 685-691.

- [5] Reddy, G. Venkateshwar, and M. Jagadesh Kumar. "A new dual-material double-gate (DMDG) nanoscale SOI MOSFET-two-dimensional analytical modeling and simulation." *IEEE Transactions on Nanotechnology* 4, no. 2 (2005): 260-268.

- [6] Cristoloveanu, Sorin, Jing Wan, and Alexander Zaslavsky. "A review of sharp-switching devices for ultra-low power applications." *IEEE Journal of the Electron Devices Society* 4, no. 5 (2016): 215-226.

- [7] Upadhyay, Navnidhi K., Hao Jiang, Zhongrui Wang, Shiva Asapu, Qiangfei Xia, and J. Joshua Yang. "Emerging memory devices for neuromorphic computing." *Advanced Materials Technologies* 4, no. 4 (2019): 1800589.

- [8] Winkler, Felix. "Through Silicon Via Field-Effect Transistor with Hafnia-based Ferroelectrics and the Doping of Silicon by Gallium Implantation Utilizing a Focused Ion Beam System." (2020).

- [9] Gupta, Neha, and Rishu Chaujar. "Optimization of high-k and gate metal workfunction for improved analog and intermodulation performance of Gate Stack (GS)-GEWE-SiNW MOSFET." *Superlattices and Microstructures* 97 (2016): 630-641.

- [10] Oh, S., H. Hwang, and I. K. Yoo. "Ferroelectric materials for neuromorphic computing." *APL Materials* 7, no. 9 (2019): 091109.

- [11] Madan, Jaya, R. S. Gupta, and Rishu Chaujar. "Performance investigation of heterogeneous gate dielectric-gate metal engineered—gate all around-tunnel FET for RF applications." *Microsystem Technologies* 23, no. 9 (2017): 4081-4090.

- [12] Li, Yang, Yong Lian, Kui Yao, and Ganesh S. Samudra. "Evaluation and optimization of short channel ferroelectric MOSFET for low power circuit application with BSIM4 and Landau theory." Solid-State Electronics 114 (2015): 17-22.

- [13] Mehta, Hema, and Harsupreet Kaur. "Subthreshold analytical model for dual-material double gate ferroelectric field effect transistor (DMGFeFET)." Semiconductor Science and Technology 34, no. 6 (2019): 065008.

- [14] Ali, T., P. Polakowski, S. Riedel, T. Büttner, T. Kämpfe, M. Rudolph, B. Pätzold et al. "High endurance ferroelectric hafnium oxide-based FeFET memory without retention penalty." *IEEE Transactions on Electron Devices* 65, no. 9 (2018): 3769-3774.

- [15] Solomon, P. M., K. W. Guarini, Y. Zhang, K. Chan, E. C. Jones, G. M. Cohen, A. Krasnoperova et al. "Two gates are better than one [double-gate MOSFET process]." *IEEE Circuits and Devices Magazine* 19, no. 1 (2003): 48-62.

- [16] Sharma, Rupendra Kumar, Ritesh Gupta, Mridula Gupta, and R. S. Gupta. "Dual-material double-gate SOI n-MOSFET: gate misalignment analysis." *IEEE transactions on electron devices* 56, no. 6 (2009): 1284-1291.

- [19] Silvaco Atlas User's Manual

Dissertation Report - EDIT (2).docx Jun 1, 2021 4437 words / 25793 characters

## Dissertation Report - EDIT (2).docx

### **Sources Overview**

8%

OVERALL SIMILARITY

| 1  | qmro.qmul.ac.uk INTERNET                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | <1% |

|----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 2  | eprints.hud.ac.uk INTERNET                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | <1% |

| 3  | R. Ramesh. "Influence of gate and channel engineering on multigate MOSFETs-A review", Microelectronics Journal, 2017 CROSSREF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | <1% |

| 4  | Biswajit Baral, Aloke Kumar Das, Debashis De, Angsuman Sarkar. "An analytical model of triple-material double-gate metal-oxide-semi  CROSSREF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | <1% |

| 5  | Narain Arora. "MOSFET Models for VLSI Circuit Simulation", Springer Science and Business Media LLC, 1993 CROSSREF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | <1% |

| 6  | Amity University on 2018-07-20 SUBMITTED WORKS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | <1% |

| 7  | Aligarh Muslim University, Aligarh on 2019-08-06 SUBMITTED WORKS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | <1% |

| 8  | thesis.library.caltech.edu  INTERNET                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | <1% |

| 9  | TINTERNET TO THE PROPERTY OF T | <1% |

| 10 | University of Maryland, University College on 2005-02-28 SUBMITTED WORKS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | <1% |

| 11 | University of Surrey on 2013-05-13 SUBMITTED WORKS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | <1% |

| 12 | portal.research.lu.se INTERNET                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | <1% |

| 13 | www.lib.utexas.edu<br>INTERNET                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | <1% |

| 14 | National Institute of Technology, Hamirpur on 2017-10-11 SUBMITTED WORKS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | <1% |

| 15 | SASTRA University on 2016-04-08 SUBMITTED WORKS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | <1% |

| 16 | nith on 2021-05-15 SUBMITTED WORKS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | <1% |

| 17 | xdaq.web.cern.ch INTERNET                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | <1% |

| 18 | "IEEE-ICDCS conference proceeding", 2012 International Conference on Devices Circuits and Systems (ICDCS), 03/2012 CROSSREF                     | <1% |

|----|-------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 19 | Arighna Basak, Angsuman Sarkar. "Analytical Study of Unipolar Junction Transistor as a Novel Dual Material Double Gate MOSFET to                | <1% |

| 20 | Madheswaran, M., R. Ramesh, and K. Kannan. "Hot-carrier reliability on the optical characteristics of gate stack gate all-around (GSGA CROSSREF | <1% |

| 21 | Tohru Shiga. "Deformation and Viscoelastic Behavior of Polymer Gels in Electric Fields", Advances in Polymer Science, 1997 CROSSREF             | <1% |

| 22 | UT, Dallas on 2010-09-29 SUBMITTED WORKS                                                                                                        | <1% |

| 23 | Varun Mishra, Yogesh K. Verma, Santosh K. Gupta. "Surface potential-based analysis of ferroelectric dual material gate all around (FE CROSSREF  | <1% |

| 24 | dokumen.pub<br>INTERNET                                                                                                                         | <1% |

| 25 | iopscience.iop.org INTERNET                                                                                                                     | <1% |

| 26 | www.studentpipeline.org INTERNET                                                                                                                | <1% |

#### Excluded search repositories:

None

### **Excluded from Similarity Report:**

- Bibliography

- Small Matches (less than 9 words).

#### Excluded sources:

None

### LIST OF PUBLICATION OF CANDIDATE'S WORK

### Analog Analysis of Novel Ferroelectric-Dual Material Oxide Stack-Double Gate FET

Isha Dahiya<sup>1</sup>, Rishu Chaujar<sup>2</sup>

(e-mail: <sup>1</sup>isha24dahiya@gmail.com; <sup>2</sup>chaujar.rishu@dtu.ac.in)

1,2

Department of Applied Physics, Delhi Technological University, Main Bawana Road, Delhi, 110042, India