# SINGLE CAPACITOR SIMULATION OF FLOATING INDUCTORS USING VOLTAGE DIFFERENCING INVERTING BUFFERED AMPLIFIER

A DISSERTATION REPORT

SUBMITTED IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE AWARD OF THE DEGREE OF

# MASTER OF TECHNOLOGY IN VLSI AND EMBEDDED SYSTEMS

Submitted by:

ABHISHEK SHARMA

2K17/VLS/01

Under the supervision of

PROF. D. R. BHASKAR

## DEPARTMENT OF ELECTRONICS AND COMMUNICATION

DELHI TECHNOLOGICAL UNIVERSITY

(Formerly Delhi College of Engineering) Bawana Road, Delhi-110042

JULY, 2019

### Single Capacitor Simulation of Floating Inductors Using Voltage Differencing Inverting Buffered Amplifier

A MAJOR PROJECT REPORT

SUBMITTED IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE AWARD OF THE DEGREE OF

# MASTERS OF TECHNOLOGY IN VLSI AND EMBEDDED SYSTEMS

Submitted by:

#### **ABHISHEK SHARMA**

2K17/VLS/01

Under the supervision of

PROF. D. R. BHASKAR

## DEPARTMENT OF ELECTRONICS AND COMMUNICATION

DELHI TECHNOLOGICAL UNIVERSITY

(Formerly Delhi College of Engineering) Bawana Road, Delhi-110042

JULY, 2019

**ECE DEPARTMENT**

DELHI TECHNOLOGICAL UNIVERSITY

(Formerly Delhi College of Engineering)

Bawana Road, Delhi-110042

**CANDIDATE'S DECLARATION**

I, ABHISHEK SHARMA, 2K17/VLS/01 student of M.Tech (VLSI), hereby declare that

the Dissertation report titled "Single Capacitor Simulation of Floating Inductors Using

Voltage Differencing Inverting Buffered Amplifier" which is submitted by me to the

Department of Electronics and Communication, Delhi Technological University, Delhi in

partial fulfillment of the requirement for the award of the degree of Master of Technology,

is original and not copied from any source without proper citation. This work has not

previously formed the basis for the award of any Degree, Diploma Associateship, Fellowship

or other similar title or recognition.

Place: Delhi

Date:

ABHISHEK SHARMA

[i]

#### **ECE DEPARTMENT**

#### **DELHI TECHNOLOGICAL UNIVERSITY**

(Formerly Delhi College of Engineering) Bawana Road, Delhi-110042

#### **CERTIFICATE**

Inductors Using Voltage Differencing Inverting Buffered Amplifier" which is submitted by ABHISHEK SHARMA, 2K17/VLS/01 [ECE Department], Delhi Technological University, Delhi in partial fulfillment of the requirement for the award of the degree of Master of Technology, is a record of the project work carried out by the student under my supervision. To the best of my knowledge this work has not been submitted in part or full for any Degree or Diploma to this University or elsewhere.

Place: Delhi **D.R.BHASKAR**

Date: SUPERVISOR

**PROFESSOR**

Department of Electronics and Communication

(Formerly Delhi College of Engineering)

Bawana Road, Delhi-110042

#### **ABSTRACT**

Two new simple structures for the simulation of floating lossy inductance have been proposed which realize series and parallel RL impedances employing two voltage differencing inverting buffered amplifiers (VDIBAs) as active components. The presented circuit topologies use canonical number of passive components (one resistor and one capacitor). The simulated inductor can be tuned electronically by means of transconductance of VDIBA in case of floating parallel RL structures while the inductance can be controlled through a resistance in case of series RL. The performance of the proposed configuration has been verified through SPICE simulation using TSMC 0.25um CMOS Technology.

#### **ACKNOWLEDGEMENT**

A successful project can never be prepared by the efforts of the person to whom the project is assigned, but it also demands the help and guardianship of people who helped in completion of the project.

I would like to thank all those people who have helped me in this research and inspired me during my study.

With profound sense of gratitude, I thank Prof. D. R. Bhaskar, my Research Supervisor, for his encouragement, support, patience and his guidance in this research work.

Furthermore I would also like to thank Prof. Rajeshwari Pandey, who gave me the permission to use all required equipment and the necessary format to complete the report.

I take immense delight in extending my acknowledgement to my family and friends who have helped me throughout this research work.

ABHISHEK SHARMA

### **CONTENTS**

| Cano   | idate's De      | ciaration                                             | 1    |  |  |

|--------|-----------------|-------------------------------------------------------|------|--|--|

| Certi  | ficate          |                                                       | ii   |  |  |

| Ackn   | Acknowledgement |                                                       |      |  |  |

| Abstı  | ract            |                                                       | iv   |  |  |

| Cont   | ents            |                                                       | v    |  |  |

| List   | List of Figures |                                                       |      |  |  |

| List o | f Tables        |                                                       | viii |  |  |

| List   | of Symbols      | , abbreviations                                       | xi   |  |  |

| CHA    | APTER 1         | INTRODUCTION                                          | 1    |  |  |

| CHA    | APTER 2         | LITERATURE SURVEY                                     | 4    |  |  |

| 2.1    | Overvi          | ew on Inductor Simulators                             | 4    |  |  |

| 2.2    | Overvi          | ew of VDIBA                                           | 11   |  |  |

| 2.3    | VDIBA           | A CMOS Implementation                                 | 13   |  |  |

| CHA    | APTER 3         | PROPOSED LOSSY INDUCTOR                               | 14   |  |  |

|        |                 | CONFIGURATIONS                                        |      |  |  |

| 3.1    | Propose         | ed floating lossy series inductance realization       | 14   |  |  |

| 3.2    | Propose         | ed floating lossy parallel inductance realization     | 18   |  |  |

| 3.3    | VDIBA           | Non Ideal PerformanceAnalysis                         | 22   |  |  |

|        | 3.3.1           | VDIBA parasitic effects on floating series inductor   | 23   |  |  |

|        | 3.3.2           | VDIBA parasitic effects on floating parallel inductor | 25   |  |  |

| CHA    | APTER 4         | SIMULATION RESULTS                                    | 28   |  |  |

| 4.1    | VDIBA           | Block simulation results                              | 29   |  |  |

| 4.2    | Propose         | ed lossy series inductor simulation results           | 31   |  |  |

### **CONTENTS (CONT.)**

| REFERENCES |                                                  |    |

|------------|--------------------------------------------------|----|

| CONCLUSION |                                                  | 43 |

|            | with Previously Published Inductors              |    |

| 4.5        | Comparison of Proposed Floating Inductors        | 41 |

| 4.4        | Workability Example for Proposed Series Inductor | 39 |

| 4.3        | Workability Example for Proposed Series Inductor | 35 |

### LIST OF FIGURES/ TABLES

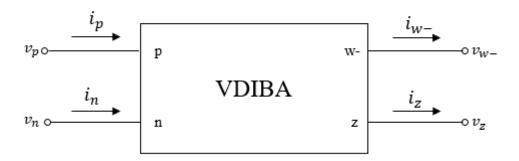

| Fig. 2.1  | Schematic Design of VDIBA                                                             |

|-----------|---------------------------------------------------------------------------------------|

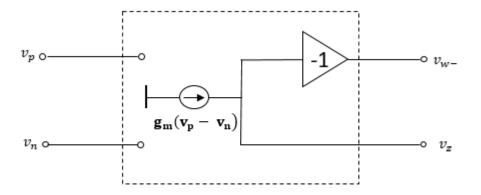

| Fig. 2.2  | Equivalent circuit of VDIBA                                                           |

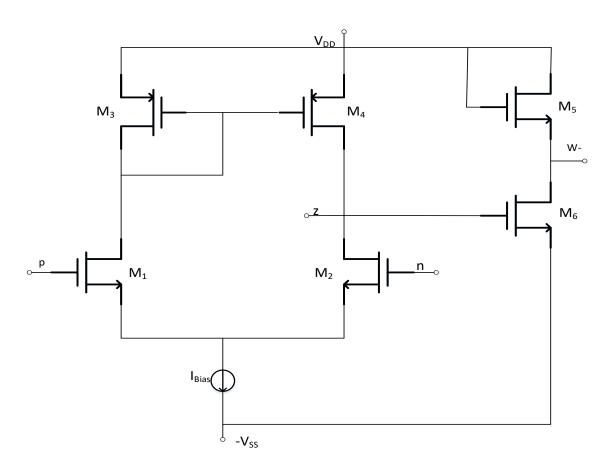

| Fig. 2.3  | CMOS implementation of VDIBA                                                          |

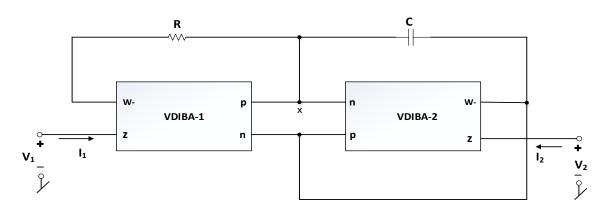

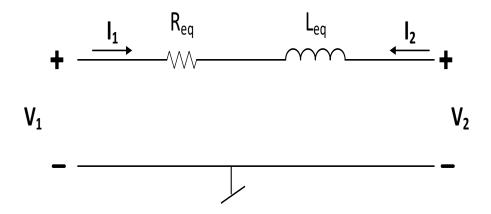

| Fig. 3.1  | Proposed lossy series inductance simulator                                            |

| Fig. 3.2  | Equivalent circuit for proposed floating series inductance                            |

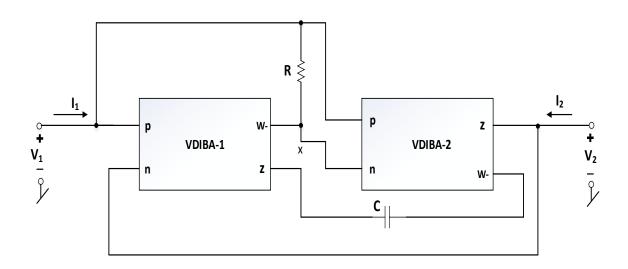

| Fig. 3.3  | Proposed floating parallel inductance simulator                                       |

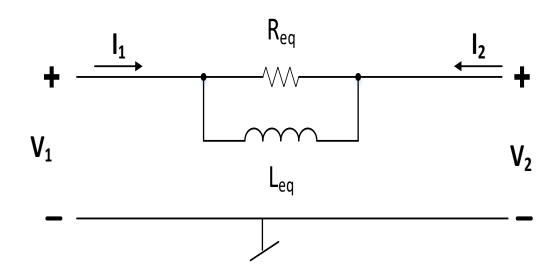

| Fig. 3.4  | Equivalent Circuit of Proposed floating parallel inductance                           |

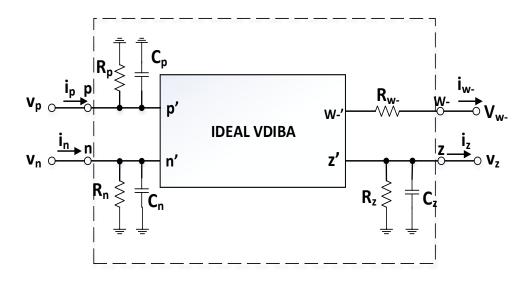

| Fig. 3.5  | VDIBA Non Ideal Model showing its parasitic elements                                  |

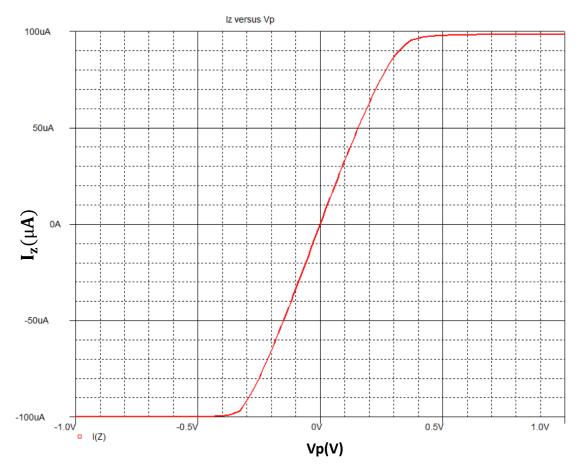

| Fig. 4.1  | $I_Z$ vs $V_p$ curve                                                                  |

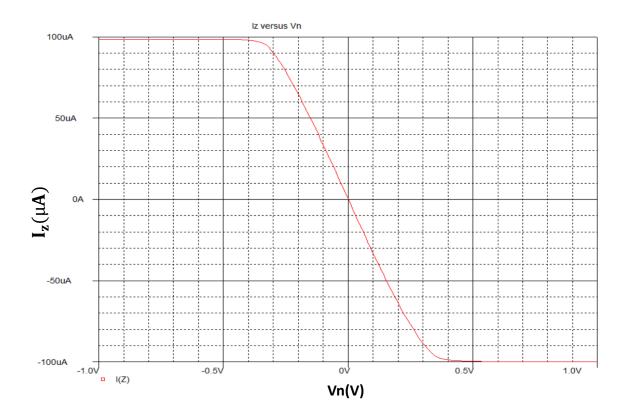

| Fig. 4.2  | $I_Z$ vs $V_n$ curve                                                                  |

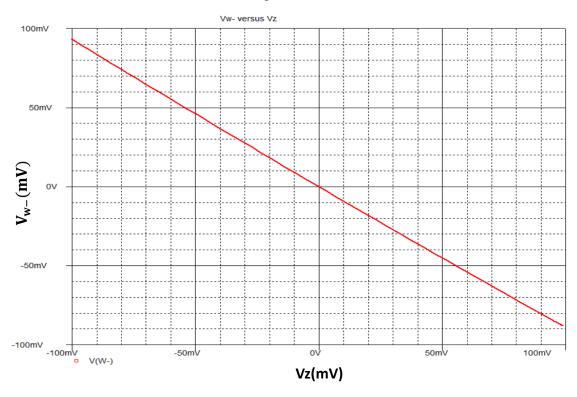

| Fig. 4.3  | $V_{w-} vs V_z$ curve                                                                 |

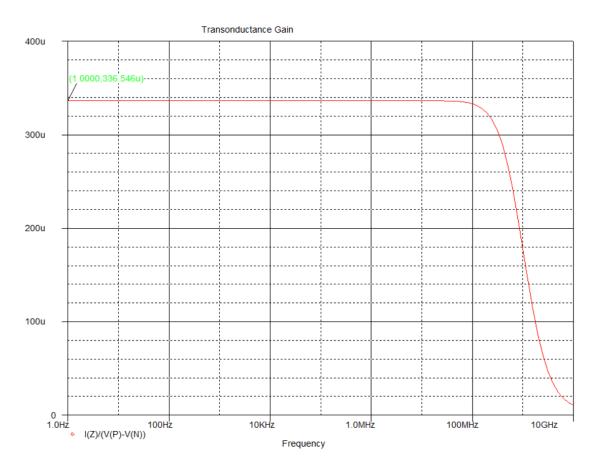

| Fig. 4.4  | Transconductance gain of VDIBA                                                        |

| Fig. 4.5  | Impedance magnitude-frequency response for Ibias1                                     |

| Fig. 4.6  | Impedance magnitude-frequency response for Ibias2                                     |

| Fig. 4.7  | Impedance magnitude-frequency response for Ibias3                                     |

| Fig. 4.8  | RLC low-pass filter realized with the floating inductor                               |

| Fig. 4.9  | Frequency response of the LPF using proposed floating Inductor for $I_{\text{bias}1}$ |

| Fig. 4.10 | Frequency response of the LPF using proposed floating inductor $I_{bias2}$            |

| Fig. 4.11 | Frequency response of the LPF using proposed floating inductor Ibias3                 |

| Fig. 4.12 | Active Resonant circuit realized with the floating inductor                           |

| Fig. 4.13 | Impedance- Frequency response of the parallel resonance circuit                       |

| Fig. 4.14 | Impedance- Frequency response of the parallel resonance circuit for different         |

|           | Biasing currents.                                                                     |

### **LIST OF TABLES**

Table I Dimensions of VDIBA CMOS Transistors

Table II Proposed Circuit comparison with other Simulators

#### **LIST OF SYMBOLS, ABBREVIATIONS**

CC Current conveyors

CCCDTA Current Controlled Current Differencing Transconductance Amplifer

CDBA Current Differencing Buffered Amplifier

CDTA Current differencing transconductance amplifiers

CFOA Current feedback operational amplifiers

CCTA Current Conveyor Transconductance Amplifier

CDDITA Current Differencing Differential Input Transconductance Amplifier

CMOS Complementary Metal Oxide Semiconductor

DVCCTA Differential Voltage Current Conveyor Transconductance Amplifier

DV-OPAMP Differential Voltage Operational Amplifier

DVCCII Differential Voltage Current Conveyor Second Generation

DDCC Differential Difference Current Conveyor

DVCC Differential Voltage Current Conveyor

FDNR Frequency Dependent Negative Resistor

LPF Low Pass Filter

MOSFET Metal Oxide Semiconductor Field Effect Transistor

OP-AMP Operational amplifiers

OTA Operational Transconductance Amplifier

OMA Operational Mirrored Amplifier

VDTA Voltage Difference Transconductance Amplifier

VDBA Voltage Differencing Buffered Amplifier

VDIBA Voltage differencing inverting buffered amplifier

#### **CHAPTER 1**

#### **INTRODUCTION**

The demand for various specifications such as small supply voltages, low dynamic power consumption, extreme speed, accuracy, compact size etc. is crucial in electronic circuits for progress of electronic technologies. Simultaneous fulfillment of all the above requirements is problematic without any tradeoffs. Thus, in order to fulfill all the demands, electronic circuits have grown and has provided ease to the circuit manufacturers in past few decades.

Inductor, one of the most widely used passive devices is one of them, which keeps on evolving depending upon the requirements of the circuit manufacturers. The inductor's applications can be found in various fields such as communications, electronics and measurements. Spiral inductor can be fabricated in integrated circuits. In spite of that, passive inductors fabricated on silicon wafer have certain limitations such as occupying excess area of chip and non-variable inductor values. Even though spiral inductors can be actualized in integrated circuits, they still have few limitations like having excess size and weight, formation of unwanted harmonics, pickings and radiating the electromagnetic waves, etc. Thus, passive inductors are being replaced by active inductance simulators where active elements are used along with passive components such as R, C to realize inductors.

Thus, in recent times, simulation of inductors using active devices (grounded and floating) has been a prominent exploration area because of their utilization in linear (active filters and oscillators) and non-linear (chaotic oscillators) circuit designs as well as their advantages over passive inductors.

Chapter 2 basically deals with the literature review highlighting the active inductance simulations employing various design techniques published in last three decades [5-51].

Floating inductance simulation configurations using various active elements like operational amplifiers (Op-amp) [52], current conveyors (CC) [53, 53], current differencing transconductance amplifiers (CDTA) [53] and current feedback amplifiers (CFA) [61] have been presented in the literature but unfortunately these reported configurations suffers from one of the corresponding downsides:

- Intemperate use of the active components (more than two) [52, 53,54,61]

- Intemperate use of the passive components (more than two) [52, 53]

- Lack of electronic controllability [58].

In order to realize the Inductor in an integrated circuit, the attention here is focused Voltage Differencing Inverting Buffered Amplifier (VDIBA), whose detailed analysis has been covered in Chapter 2 and 3.

Voltage differencing inverting buffered amplifier (VDIBA), recently introduced, is valuable active block being used across many analog signal processing and signal generation applications [60]. VDIBA is developed from the previously generated active element current differencing buffered amplifier (CDBA) [62, 63], where corresponding current difference at the input terminals of CDBA is now replaced with the voltage difference. Thus, in various voltage mode applications, circuits using VDIBA as active element have the advantage of not requiring any external passive resistors for voltage to current conversion unlike traditional CDBA circuit [64].

Also, it has the following feature that through DC bias current, VDIBA's transconductance value can be tuned electronically. When contrasted with various transconductance based active elements, like differential voltage current conveyor transconductance amplifier (DVCCTA), current conveyor transconductance amplifier

(CCTA) etc., VDIBA offers low impedance at its output terminals which makes it handy to be used in voltage-mode applications, as the loading effect is fully removed [60].

Thus, the main purpose of this dissertation is to present two simple lossy floating inductance simulator circuits with specified advantageous features:

- Low active and passive elements requirement (two VDIBA's, one capacitor and resistor).

- Electronic Tunability.

- No passive element matching constraint.

#### **CHAPTER 2**

#### **LITERATURE SURVEY**

During mid-1940, every year there was a new electronic device in the market which tried to dominate the market share of the earlier discovered products. At that time, the devices were being made with the knowledge of market value of that product which is been happening till now but now the manufacturer also take care of the other important/necessary factors like the ease of usage, environmental factors, size, weight etc.

One of the most important inventions which brought the boost in the electronics field was the invention of OPAMP in 1941 which was vacuum tube based. During early 40's to early 60's many new modifications came on the vacuum tube op-amp either it was on the type of the manufacturing technique or on some better properties than the earlier one. But the remarkable invention which caught the attention of every electronic circuit's designer was the monolithic op-amp which was small and easy to use with the remarkable property of decreased price. In the early 60's inductor size and cost was one of the most important problems. Thus, in order to overcome these problems many research papers were presented.

#### 2.1 Overview on Inductor Simulators

In the mid 60's, an attempt was made to make an inductor with a single differential input op-amp (DV-op-amp) with few passive components (Resistance and Capacitance) [5]. In this paper, distinct amplifiers were being used for carrying out capacitance transformation into equivalent coil being termed as positive-immittance inversion and cancelling out the equivalent coil losses also known as negative-immittance

conversion. In this paper a single differential input op-amp was being used to manufacture an inductor.

In the same year another paper was published which also used the (DV opamp) but its performance was better that the earlier one in terms of Quality factor which appeared to be limited primarily by the losses in the capacitors used [6]. Then in early 70's an attempt was made to fabricate a grounded inductor using unity gain op-amp along with few passive components [7]. In the year 1970, first attempt was made to manufacture an inductor using Gyrator which resulted in some new circuits for inductor fabrication [8]. In the next year op-amp based negative impedance converter was used to fabricate the inductor [9]. In the mid 70's, a lossy inductance was fabricated employing two amplifiers with passive resistances[10], the circuits described in this paper were much more sensitive than the earlier circuits which were presented. In the same year, lossy floating active RC realization of an inductor was published. Two operational amplifiers were used each in the unity gain configuration along with two passive capacitors and three resistors. [11], the fundamental advantages of the corresponding inductor design was unity gain, less component counts, easy value modifications, low sensitivities and stable configuration.

In the early 80's, resistance-controlled inductor circuits were fabricated. In this, a single grounded capacitor based lossless floating inductance circuit was realized employing three operational amplifiers. Operational amplifiers were used as unity gain summers along with three external resistors [12]. The inductor circuits obtained using RC circuits had remarkable sensitivity properties which lead to the realization of new op-amp based second order driving point impedances along with the smallest possible count of R, C passive elements [13]. During early 90's op-amp based grounded inductor was made which is very easy to understand and is based on general techniques presented in the corresponding paper [14].

During mid-95, a new floating impedance configuration based on operational mirrored amplifier (OMA) was published which required only three OMAs while keeping all previously discussed advantageous features [15]. In the year 2005, a

current conveyor based inductor circuits were also presented while maintaining all previously presented advantageous features [16]. In the year 2008, using modified current-feedback operational amplifiers (MCFOAs), a new grounded and floating inductance simulation circuit was presented which required minimum number of passive components [17].

During early 60's when the first monolithic design of op-amp was presented at the same time operational transconductance amplifiers (OTA) were also fabricated with control input as a current and with differential inputs like operational amplifiers without containing not a single passive resistor unlike in op-amps. The working of an OTA is primarily based on the working of current mirrors. Since the OTA's are originated from OPAMP hence the OTA based inductor model are not that mush old.

In the mid 2005 a paper was presented which employs two OTRA based grounded parallel immittance (combination of inductance and admittance) simulator topology which requires fewer passive components counts than others presented earlier in literature. The other key reason to use OTRA was the grounding of input terminals because of which most of the parasitic capacitances and resistances effects disappear [18]. During the same time another paper was published in which more passive equivalent circuit was developed which also included finite bandwidth effect and was comparable to active OTA based floating inductor [19].

In the same year, using Operational Transconductance Amplifiers (OTAs) as active elements, single grounded capacitor based floating inductance simulators (positive and negative) were introduced with advantageous feature of controlling the inductance values using the DC bias current. Moreover, inductor was simulated using 2 OTAs, no external resistor and no requirement of component matching conditions [20]. Then during mid-2007 a research paper was presented which primarily focused on the floating inductor simulation based on high performance structured OTA, requiring in total of 4 active OTA elements and this design being superior to previous 3-OTA based design [21].

After this, a paper proposed a novel graph based structured method for the realizing the active inductor simulation circuits. This technique consisted of first developing an inductor less flowgraph for the structure, whose transfer function corresponds to the inductor's impedance or an admittance, and developing a RC element proportionate circuit along with OTA controlled sources [22]. In the paper [20] four OTA based floating inductor was presented which was being reduced to one inductor based floating inductor having all the desirable properties of the earlier OTA based inductors [23].

Though, the use of OPAMP and OTA based inductor circuits have decreased the size of inductor circuits extensively, but in few cases, it is been required to use the inductor in the integrated circuits where the OPAMP and OTA based inductor circuit started showing constraints on minimizing the IC's size. Thus in order to overcome this issue complementary symmetry metal oxide semiconductor (CMOS) based inductor circuit started getting the popularity. In digital circuits, in any digital circuits, the word "complementary-symmetry" refers to use of n type and p type - complementary and symmetrical MOSFET transistors.

During mid 90's, a CMOS GIC based RF active inductor was described. The advantage of this CMOS based inductor to its counterparts was the reduction in the inductor losses by applying gain enhancement techniques based on cascoding. Moreover, the presented inductors had lower losses, high self-resonance frequency and wider inductive region [24]. After few years a new fully differential CMOS based floating inductor was realized. The main significance of shifting to active inductors design are decrease in chip area consumption by inductors and decrease in fabrication processing cost which would have occurred in fabrication of passive inductors, and extra feature of tunability where inductance values can be tuned [25].

In the year 2000 another paper was presented which tried to overcome some of the problems faced by earlier CMOS based designs. In that research, a new CMOS transistor based active inductor circuit relying on circuit configuration of VHF (Very High Frequency) was presented which allowed the circuit to have low power supply

voltages (< 2V) at very high frequency operation. For reducing inductor losses and achieving high Quality factor along with wide operating bandwidth, Gain enhancement techniques were applied [26]. After few years, surface micromachining technology designed and fabricated a highly suspended CMOS compatible spiral inductors on standard silicon substrate (1-30 $\Omega$ -cm in resistivity. This CMOS compatible spiral inductor was capable of achieving Q factor of 70 at 6GHz frequency which is the highest Q factor ever reported on standard silicon substrate at this frequency [27]. In the same year, Current Controlled Current Differencing Transconductance Amplifier (CCCDTA) based grounded as well as floating inductance was simulated requiring only one active block.

The main advantage of this simulated inductance was the electronic controllability of inductance by tuning the dc current of corresponding active element. Floating and grounded Inductance simulator circuit comprised combination of 1 active CCCDTA block each, two to one voltage buffers and one grounded capacitor each respectively, as well as provided advantage for having no passive element matching conditions [28]. In 2010 CMOS technology based digitally controlled lossless floating inductor was fabricated using current conveyors along with array of resistor for providing digital tuning of inductance values. The Inductance value can be adjusted from 0.42763mH to 5.67mH [29].

In the same year, through the tapped-inductor feedback technique, a new Q-enhanced inductor was presented which helped in reducing resistive losses by minimizing the consumed power and also provided a large inductance value inductor in contrast with traditional transformer feedback architectures [30]. In the mid 2011 another paper was presented which proposed frequency dependent floating inductor (FI) simulation circuit using 2 CBTAs and 3 grounded passive components. Based on the component selection, this ci2rcuit can realize resistor, a floating FDNR, an inductor or a capacitor. Also, circuit provides a feature of no passive element matching requirements and provides better sensitivity performance in respect to tracking errors [31].

Recently, in early 2012 a grounded capacitor based floating inductance circuit employing 2 differential voltage second-generation current conveyors (DVCCIIs) operating at very low voltage levels ( $\pm 0.75$  V) was designed. The circuit did not need any component matching conditions [32].

During same time, current mode analog circuits getting popularity which led to invention of Current Conveyors. Observations are also made on current conveyor based inductors in the literature. In the early 70's improvised version of second current conveyor was presented which is used to form a function generator, gyrator, NIC, DVCCS/DVCVS etc. [33]. Then during early 80's a grounded inductance realization using the DVCCS/DVCVS as the active element was presented in which a single grounded capacitor was used to control the inductor magnitude [34]. Then during same time another paper was published for realizing inductance employing second generation CC-II current conveyor as the active element along with three passive components. The inductor realized was seen desirable for moderate applications [35] while in the other paper published, it was demonstrated that current conveyors based inductors can be simulated with minimum count of passive components, only 1 capacitor and 2-3 passive resistors [36]. During the same time a new lossy frequency independent floating inductance was realized employing one second generation CC-II current conveyor along with a one capacitor, and 2 resistors without need of any equality constraint [37]. In the same year it was shown that using CC-II active block and a single grounded capacitor, a grounded inductor can be realized.

The main feature of this was the automatic adjustment of Q factor and its immunity to changes in CC-II parameters which also made it appropriate for high quality applications [38]. After sometime, floating series and parallel RL impedance were demonstrated with CC-II as active element without any component matching requirements. The circuit also facilitated single resistor based automatic control of inductance value and low passive element count (R, C) [39]. During the same year, a new CC-II based lossless synthetic floating inductance circuit was proposed whose value was controllable through a single grounded resistor [40]. Next year three new active simulation circuits were published which realized floating lossless inductance and RL series/parallel impedances respectively using three and two CC-II as active blocks.

The published circuits had salient features such as no matching conditions in components, minimum possible count of passive elements (R, C) and resistance-controlled inductance values [41]. Then during early 80's a grounded inductor using single CC-II was proposed. The realization method is quite versatile and can produce a grounded impedance that may be bilinear RL, ideally inductive or inductive with a positive or negative resistive part either in series or in parallel [42]. During the end of the same year a paper was presented in which an ideal floating inductance was simulated. The main advantage of this work was that the floating inductance was tunable through a single resistor and it has been shown that it is possible to simulate these realizations with unmatched passive components [43]. During early 80's, grounded capacitor based floating lossless inductance simulation was published using a CCII as active element. [44]. Then during early 90's a lossless floating immittance using CCIIs was proposed.

The main advantage in that paper was that based on Nullator. Nullator technique various simulation circuits could be derived comprehensively [45]. During the mid-90's, various new second order current mode circuits were derived using current conveyors as basic elements. Then using these new circuits' inductors outputs were compared which were more reliable and close to the ideal characteristics of grounded inductor [46]. Thus an era had begun where changes in the CC-II were started observing which paved way for the third generation current conveyors (CC-III). During 2000 an actively simulated grounded lossy inductors using CC-III was proposed. Then during the mid2005, a new single capacitor based floating lossless inductor employing CCCII was presented. The circuit has electronic tunability as the inductor value could be adjusted through the biasing currents of the CCCIIs [47]. During 2006, two new CCCII based floating inductors were realized depending on passive components choices [48], with no constraint on component matching as its primary advantage.

During the mid of 2007, a new hybrid inductor was realized which employed hybrid consolidation of operational amplifiers and current conveyors. The circuit offered inductors with high Quality factor in contrast to traditional current conveyor circuits [49]. The other qualities of the hybrid device was that it can be utilized in many ways: (i) as a monodirectional floating inductor, (ii) as a grounded inductor, (iii) as a bidirectional

inductor. Bidirectional Inductor has utility that purely the count of active components is increased in contrast to monodirectional inductor circuits without expanding passive components count. Then in the year 2008 a paper was presented in which the inductor in been made using CC-II with improved performance even at low frequency [50]. In same year, a synthetic grounded lossless inductor using an active differential voltage current conveyor transconductance amplifier (DVCCTA) device with passive RC was developed. The advantage of this circuit is its insensitivity towards port mismatch errors over its counterparts and also no component matching constraint [51].

#### 2.2 Overview of VDIBA

Several new active elements such as CDDITA, VDBA, VDTA etc. were introduced in [59] for the first time. The voltage differencing inverting buffered amplifier (VDIBA), updated from VDBA (presented in [60]), has been recently introduced as an active device for analog signal processing applications.

Fig. 2-1 Schematic Design of VDIBA

Voltage differencing inverting buffered amplifier (VDIBA) is a 4 terminal active block along with electronic tunability. The schematic symbolic representation and equivalent circuit of VDIBA are presented below in Fig. 2.1 and Fig. 2.2 distinctively [60]. From equivalent circuit model it can be inferred that VDIBA exhibits high-impedance at input terminals (in this dissertation labeled as p and n), high-impedance at z terminal, and low-impedance at w- terminal.

Fig. 2-2 Equivalent circuit of VDIBA

The input stage of VDIBA consists of an operational transconductance amplifier (OTA), which transforms the differential voltage at its input terminals to the output current that flows out from its z terminal. VDIBA's output is implemented by a unity gain inverted buffer. As both stages (OTA and unity gain inverted buffer) can be actualized by commercially available ICs (Integrated Circuits), VDIBA is suitable for electronically controllable circuit requisitions.

The terminal relationships between port currents and voltages of the VDIBA can be specified by the subsequent hybrid matrix:

$$\begin{bmatrix} i_p \\ i_n \\ i_z \\ v_{,,,,-} \end{bmatrix} = \begin{bmatrix} 0 & 0 & 0 & 0 \\ 0 & 0 & 0 & 0 \\ g_m & -g_m & 0 & 0 \\ 0 & 0 & -\beta & 0 \end{bmatrix} \begin{bmatrix} v_p \\ v_n \\ v_z \\ v_{w-} \end{bmatrix}$$

(2.1)

Where  $g_m$  represents transconductance and  $\beta$  means non-ideal voltage gain of VDIBA. For an ideal VDIBA, the value of  $\beta$  is unity.

From Equation (2.1), it can be inferred that the differential voltage at input terminals i.e.  $(v_p - v_n)$  of VDIBA is transformed into the output current flowing out from the z terminal and the voltage at z terminal is conveyed to w-port (inverted).

Generally, the transconductance is electrically adjustable by tuning the bias current in VDBIA [60].

#### 2.3 VDIBA CMOS Implementation

A simple VDIBA CMOS implementation is presented below in Fig. 3.3 [63]

Fig. 2.3 CMOS implementation of VDIBA [60]

VDIBA consists of M1-M4 transistors as active loaded differential pair combined with unity gain inverting voltage buffer at the output stage (with M5 and M6 as matched transistors). Output stage can also be called a unity-gain common-source amplifier with diode-connected load (M5). VDD and VSS are the supply voltages provided to the circuit.

#### **CHAPTER 3**

# THE PROPOSED LOSSY INDUCTOR CONFIGURATIONS

As stated in Chapter 1, Active simulation of Inductors offers various advantages over their passive counterpart. Here, single capacitor based inductor simulation using recently introduced active element VDIBA is being proposed which realizes lossy series and parallel inductances.

#### 3.1 Proposed Floating Lossy Series Inductance Realization

The proposed tunable floating lossy series inductor employing voltage differencing inverted buffered amplifiers, along with one capacitor and resistor, is shown in Fig. 3.1.

Fig. 3.1 Proposed lossy series inductance simulator

The proposed floating series inductor is realized with two VDIBAs, one resistor R and a capacitor C. Assuming Ideal VDIBA, from the VDIBA behavior description in Fig 2.1 and doing circuit analysis of Figure 3.1, with  $g_{m1} = g_{m2} = g_m$ , the equivalent input impedance can be derived as:

At node x,

$$(V_{w2} - V_x)sC = \frac{V_x - V_{w1}}{R}$$

(3.1)

From above Equation (3.1), we get

$$V_{x} = \frac{V_{w1-} + V_{w2-} sRC}{1 + sRC}$$

$$V_{w1-} = -V_{z1}, V_{w2-} = -V_{z2}, V_{z1} = V_1, V_{z2} = V_2$$

$$V_x = \frac{-V_1 - V_2 \text{ sRC}}{1 + \text{sRC}}$$

(3.2)

From Matrix (2.1), we know,

$$\begin{split} i_{z1} &= g_m (V_{p1} - V_{n1}) \\ V_{p1} &= V_x \\ V_{n1} &= -V_2 \\ i_{z1} &= -i_1 \\ \\ -i_1 &= g_m (V_x + V_2) \end{split} \tag{3.3}$$

Putting values of  $V_x$  from Equation (3.2) in Equation (3.3), we get Equation (3.4)

$$-i_{1} = g_{m} \frac{-V_{1} + V_{2}}{1 + sRC}$$

or

$$i_{1} = g_{m} \frac{V_{1} - V_{2}}{1 + sRC}$$

(3.4)

From Matrix 2.1:

$$\begin{split} i_{z2} &= g_m (V_{p2} - V_{n2}) \\ V_{p2} &= -V_2 \\ V_n &= V_x \\ i_{z2} &= -i_2 \\ -i_2 &= g_m (-V_2 - V_x) \end{split} \tag{3.5}$$

Putting values of  $V_x$  from Equation 3.2 in Equation (3.5), we get Equation (3.6)

$$-i_{2} = g_{m} \frac{-V_{2} + V_{1}}{1 + sRC}$$

or

$$i_{2} = g_{m} \frac{V_{2} - V_{1}}{1 + sRC}$$

(3.6)

From Equation (3.4) and (3.6),

$$i_1 = g_m \frac{V_1 - V_2}{1 + sRC}$$

$$i_2 = g_m \frac{V_2 - V_1}{1 + sRC}$$

From above 2 Equations, we can say:

$$\begin{bmatrix} \mathbf{i}_1 \\ \mathbf{i}_2 \end{bmatrix} = \begin{bmatrix} \frac{\mathbf{g}_m}{1 + \mathbf{s}RC} & -\frac{\mathbf{g}_m}{1 + \mathbf{s}RC} \\ -\frac{\mathbf{g}_m}{1 + \mathbf{s}RC} & \frac{\mathbf{g}_m}{1 + \mathbf{s}RC} \end{bmatrix} \begin{bmatrix} \mathbf{V}_1 \\ \mathbf{V}_2 \end{bmatrix}$$

(3.7)

From standard two port network theorems, we have

$$\begin{bmatrix} i_1 \\ i_2 \end{bmatrix} = [Y] \begin{bmatrix} V_1 \\ V_2 \end{bmatrix}$$

$$[Y] = \frac{1}{Z_{eq}} \begin{bmatrix} 1 & -1 \\ -1 & 1 \end{bmatrix}$$

(3.8)

Thus, from above three equations, we can say that:

$$Y_{eq1} = g_m \left(\frac{1}{1 + sRC}\right)$$

or

$$Z_{eq1} = \frac{1}{g_m} + \frac{sRC}{g_m}$$

(3.9)

$$R_{eq} = \frac{1}{g_m} \& L_{eq} = \left(\frac{C \cdot R}{g_m}\right)$$

(3.10)

From Equation (3.10), the proposed circuit in Fig. 3.1 realizes single capacitor based floating series R-L impedance, and equivalent RL values are described as  $R_{eq} = \frac{1}{g_m}$  and  $L_{eq} = \left(\frac{CR}{g_m}\right)$ . From above analysis, the  $R_{eq}$  value can be tuned electronically via  $g_m$ , and inductance  $L_{eq}$  value can be tuned independently through R and/or C.

Fig. 3.2 Equivalent circuit for proposed floating series inductance

For above floating inductor circuit, the quality factor (Q) is defined as in Equation (3.11):

$$Q = w. R. C \tag{3.11}$$

Fig. 3.2 represents the equivalent circuit for floating series inductance between two ports with equivalent resistance  $R_{eq} = \frac{1}{g_m}$  and equivalent inductance as  $L_{eq} = \left(\frac{c R}{g_m}\right)$ .

# 3.2 Proposed Floating Lossy Parallel Inductance Configuration

The proposed tunable floating parallel inductance realization employing voltage differencing inverted buffered amplifier as active element, along with resistor and capacitor, is shown in Fig. 3.3

Fig. 3.3 Proposed floating parallel inductance simulator

Here, single capacitor based floating parallel inductor is realized with two VDIBAs along with one passive resistor R. From the VDIBA behavior in Matrix (2.1) circuit analysis is done below:

From Matrix (2.1), we know

$$i_{z1} = g_{m1}(V_{p1} - V_{n1})$$

$$V_{p1} = V_{1}$$

$$V_{n1} = V_{2}$$

$$i_{z1} = (V_{z1} - V_{w2})sC$$

$$V_{w2} = -V_{2}$$

At terminal Z1 of VDIBA-1,

$$g_{m1}(V_1 - V_2) = (V_{z1} - V_{w2})sC$$

$$g_{m1}(V_1 - V_2) = (V_{z1} - V_{w2})sC$$

On solving the above stated Equations, we get

$$V_{z1} = \frac{g_{m1}V_1 - V_2 (g_{m1} + sC)}{sC}$$

$$V_x = V_{w1} = -V_{z1}$$

$$i_1 = \frac{V_1 - V_x}{R}$$

$$i_1 = \frac{V_1 + V_{z1}}{R}$$

Putting Value of Vz1 from equation (3.12), we get  $i_1$  as

$$i_{1} = \frac{1}{R} \left[ V_{1} + \frac{g_{m1}V_{1-}V_{2}\left[g_{m1} + sC\right]}{sC} \right]$$

$$i_1 = \frac{1}{R} \left( \frac{(g_{m1} + sC)}{sC} \right) [V_{1-} V_2]$$

(3.13)

From Matrix (2.1), we get

$$\begin{split} i_{z2} &= g_{m2}(V_{p2} - V_{n2}) \\ V_{p2} &= V_1 \\ V_{n2} &= V_x \\ i_{z2-} &= -i_2 \\ -i_2 &= g_{m2}(V_1 - V_x) \\ V_x &= V_{w1} = -V_{z1} \\ -i_2 &= g_{m2}(V_1 + V_{z1}) \end{split}$$

Putting value of  $V_{z1}$  from Equation (3.12), we get

$$-i_{2} = g_{m2}[V_{1} + \frac{g_{m1}V_{1-}V_{2}[g_{m1} + sC]}{sC}]$$

$$i_{2} = g_{m2}\left(\frac{(g_{m1} + sC)}{sC}\right)[V_{2-}V_{1}]$$

$$i_{2} = \left(g_{m2} + \frac{g_{m1}g_{m2}}{sC}\right)[V_{2-}V_{1}]$$

(3.14)

From Equations (3.13) and (3.14), For  $\mathbf{R} = \frac{1}{g_{m2}}$  we get,

$$\begin{bmatrix}

i_1 \\

i_2

\end{bmatrix} = \begin{bmatrix}

(g_{m2} + \frac{g_{m1}g_{m2}}{sC}) & -(g_{m2} + \frac{g_{m1}g_{m2}}{sC}) \\

-(g_{m2} + \frac{g_{m1}g_{m2}}{sC}) & (g_{m2} + \frac{g_{m1}g_{m2}}{sC})

\end{bmatrix} \begin{bmatrix}

V_1 \\

V_2

\end{bmatrix}$$

(3.15)

From standard two port network theorem, we have Y matrix defined as:

$$\begin{bmatrix} i_1 \\ i_2 \end{bmatrix} = \begin{bmatrix} Y \end{bmatrix} \begin{bmatrix} V_1 \\ V_2 \end{bmatrix}$$

$$[Y] = \frac{1}{Z_{eq}} \begin{bmatrix} 1 & -1 \\ -1 & 1 \end{bmatrix}$$

Thus, on comparing above three equations, we get

$$Y_{eq} = \left(g_{m2} + \frac{g_{m2} g_{m1}}{sRC}\right)$$

(3.16)

$$R_{eq1} = \frac{1}{g_{m2}} \& L_{eq1} = \frac{C}{g_{m1}g_{m2}}$$

(3.17)

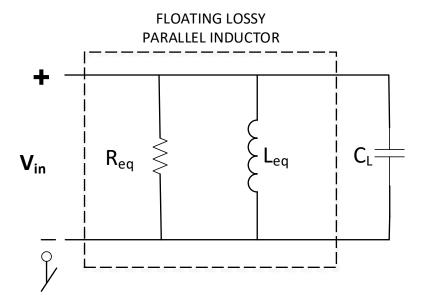

Thus, from Equation (3.17), it can be inferred that the circuit in Fig. 3.3 realizes single capacitor based floating parallel RL impedance, and equivalent R, L values being described as  $\mathbf{R_{eq}} = \frac{1}{\mathbf{g_{m2}}}$  and  $\mathbf{L_{eq}} = \frac{\mathbf{C}}{\mathbf{g_{m1}g_{m2}}}$ . From this it is seen that  $R_{eq}$  value can be tuned through R and/or  $g_{m2}$  and the  $L_{eq}$  is electronically tunable through  $g_{m1}$ .

Fig. 3.4 Equivalent Circuit of Proposed floating parallel inductance

For above circuit, the quality factor (Q) is described as:

$$Q = \frac{\omega.\,C}{g_{m1}} \tag{3.18}$$

Fig. 3.4 represents the equivalent circuit of lossy floating parallel inductance between two ports with equivalent resistance  $R_{eq} = \frac{1}{g_{m2}}$  and equivalent inductance as  $L_{eq} = \frac{C}{g_{m1}g_{m2}}$ . And  $\omega$  is the angular frequency of operation.

#### 3.3 VDIBA Non-Ideal Performance Analysis

VDIBA non ideal model with its parasitic elements is depicted in Fig. 3.5. Practical VDIBA has parasitic resistances and capacitances at terminals p, n, and z to the ground (**Rp**//**Cp**, **Rn**// **Cn**, **and Rz**//**Cz**), and a serial parasitic resistance **R**<sub>w</sub> at the terminal w.

Fig. 3.5 VDIBA Non-Ideal Model showing its parasitic elements

Considering the parasitic resistance  $R_z$  and capacitance  $C_z$  of terminal z, the terminal voltages and current relationship is given by:

$$\begin{bmatrix} i_{p} \\ i_{n} \\ i_{z} \\ v_{w-} \end{bmatrix} = \begin{bmatrix} 0 & 0 & 0 & 0 \\ 0 & 0 & 0 & 0 \\ g_{m} & -g_{m} & sC_{z} + \frac{1}{R_{z}} & 0 \\ 0 & 0 & -\beta & 0 \end{bmatrix} \begin{bmatrix} v_{p} \\ v_{n} \\ v_{z} \\ v_{w-} \end{bmatrix}$$

(3.19)

Where  $\beta = (1-e_v)$ ,  $|e_v| << 1$ , represents voltage tracking error from z terminal to terminal w-,  $g_m$  represents transconductance and  $C_z$  and  $R_z$  are the parasitic elements of terminal z.

#### 3.3.1 VDIBA Parasitic Elements Effect on Floating Series Inductor

Considering parasitic effects at Z terminal, Non-Ideal analysis is being done for determining floating lossy series inductance for Fig. 3.1.

At node x,

$$(V_{w2} - V_x)sC = \frac{V_x - V_{w1}}{R}$$

(3.20)

From above Equation (3.20), we get

$$V_{x} = \frac{V_{w1-} + V_{w2-} sRC}{1 + sRC}$$

$$V_{w1-} = -\beta_1 V_{z1}, V_{w2-} = -\beta_2 V_{z2}, V_{z1} = V_1, V_{z2} = V_2$$

$$V_{x} = \frac{-\beta_{1}V_{1} - \beta_{2}V_{2} \text{ sRC}}{1 + \text{sRC}}$$

(3.21)

Assuming,

$$g_{m1} = g_{m2} = g_m$$

$$i_{z1} = g_m (V_{p1} - V_{n1}) + V_{z1} (sC_{z1} + \frac{1}{R_{z1}})$$

$$V_{p1} = V_x$$

[23]

$$V_{n1} = -\beta_2 V_2$$

$$i_{z1} = -i_1$$

$$-i_1 = g_m(V_x + \beta_2 V_2) + V_{z1} \left(sC_{z1} + \frac{1}{R_{z1}}\right)$$

Putting value of  $V_x$  from Equation (3.21) in above Equation, we get Equation (3.22)

$$-i_1 = g_m \frac{-\beta_1 V_1 + \beta_2 V_2}{1 + sRC} + V_{z1} (sC_{z1} + \frac{1}{R_{z1}})$$

$$\begin{aligned} V_{1} \left( \frac{\beta_{1} - (1 + sRC)(sC_{z1} + \frac{1}{R_{z1}})}{g_{m}} \right) - \frac{\beta_{2}V_{2}}{g_{m}} \\ i_{1} = g_{m} \frac{1 + sRC}{} \end{aligned} \tag{3.22}$$

Similarly, from Equation (3.19) we get,s

$$\begin{split} i_{z2} &= g_m \big( V_{p2} - V_{n2} \, \big) + \, V_{z2} (s C_{z2} + \frac{1}{R_{z2}}) \\ V_{p2} &= -\beta_2 V_2 \\ V_n &= V_x \\ i_{z2} &= -i_2 \\ -i_2 &= g_m (-\beta_2 V_2 - V_x) + \, V_2 \left( s. \, C_{z2} + \frac{1}{R_{z2}} \right) \end{split}$$

Putting values of  $V_x$  from equation (3.21) in above equation, we get:

$$-i_2 = g_m \frac{-\beta_2 V_2 + \beta_1 V_1}{1 + sRC} + V_2 \left( sC_{z2} + \frac{1}{R_{z2}} \right)$$

$$v_{2}\left(\frac{\beta_{2}-(1+sRC)(sC_{z2}+\frac{1}{R_{z2}})}{g_{m}}\right)-\frac{\beta_{1}V_{1}}{g_{m}}$$

$$i_{2}=g_{m}\frac{1+sRC} \tag{3.23}$$

From Equation (3.22) and (3.23), we get,

$$\begin{bmatrix} i_1 \\ i_2 \end{bmatrix} = \begin{bmatrix} (g_m \beta_1 + (1 + sRC)(sC_{z1} + \frac{1}{R_{z1}})) & -(g_{m2}\beta_2) \\ -(g_{m2}\beta_2) & (g_m \beta_2 + (1 + sRC)(sC_{z2} + \frac{1}{R_{z2}})) \end{bmatrix} \begin{bmatrix} V_1 \\ V_2 \end{bmatrix}$$

Assuming  $\beta_1$ ,  $\beta_2=1$ ,  $C_{z2}=C_{z1}=C_z$  and  $R_{z2}=R_{z1}=R_z$ , we get

$$\begin{bmatrix} i_1 \\ i_2 \end{bmatrix} = \begin{bmatrix} (g_m + (1 + sRC)(sC_z + \frac{1}{R_z})) & -(g_m) \\ -(g_m) & (g_m + (1 + sRC)(sC_z + \frac{1}{R_z})) \end{bmatrix} \begin{bmatrix} V_1 \\ V_2 \end{bmatrix}$$

Thus from above equation, we can infer that equivalent impedance is affected by parasitic elements.

#### 3.3.2 VDIBA Parasitic Elements Effect on Floating Parallel Inductor

Considering parasitic effects, Non-Ideal analysis is being done for determining floating lossy parallel inductance for Fig. 3.3. As we have already seen the non-ideal circuit equations with the help of Equation (3.19).

$$i_{z1} = g_{m1}(V_{p1} - V_{n1}) + V_{z1}(sC_{z1} + \frac{1}{R_{z1}})$$

$$V_{p1} = V_{1}$$

$$V_{n1} = V_{2}$$

$$i_{z1} = (V_{z1} - V_{w2})sC$$

$$V_{w2} = -\beta_{2}V_{2}$$

[25]

$$g_{m1}(V_1 - V_2) + V_{z1}(sC_{z1} + \frac{1}{R_{z1}}) = (V_{z1} - V_{w2})sC$$

$$g_{m1}(V_1 - V_2) + V_{z1}\left(sC_{z1} + \frac{1}{R_{z1}}\right) = (V_{z1} + \beta_2 V_2)sC$$

On solving the above Equation, we get  $V_{z1}$  as shown in Equation (3.24)

$$V_{z1} = \frac{g_{m1}V_1 - V_2 (g_{m1} + sC\beta_2)}{(sC - sC_{z1}) - \frac{1}{R_{z1}}}$$

(3.24)

$$\begin{aligned} V_{x} &= V_{w1} = -\beta_{1}V_{z1} \\ V_{w1} &= -\beta_{1}V_{z1} \\ i_{1} &= \frac{V_{1} - V_{x}}{R} \\ i_{1} &= \frac{V_{1} + \beta_{1}V_{z1}}{R} \end{aligned} \tag{3.25}$$

$$i_{1} = \frac{g_{m1}}{R\left((sC - sC_{z1}) - \frac{1}{R_{z1}}\right)} \left[ \left(\frac{V_{1}\left((sC - sC_{z1}) - \frac{1}{R_{z1}}\right)}{g_{m1}} + \beta_{1}g_{m1}\right) - V_{2}\left[g_{m1} \ \beta_{2}sC\right] \right]$$

(3.26)

From Equation (3.19), we have

$$\begin{split} i_{z2} &= g_{m2} \big( V_{p2} - V_{n2} \, \big) + \, V_{z2} (s C_{z2} + \frac{1}{R_{z2}}) \\ V_{p2} &= V_1 \\ V_{n2} &= V_x \\ V_x &= V_{w1} = -V_{z1} \\ -i_2 &= g_{m2} (V_1 + \beta_1 V_{z1}) + V_{z2} \Big( s C_{z2} + \frac{1}{R_{z2}} \Big) \end{split}$$

On putting  $V_{z1}$  value from Equation (3.24) in above Equation, we get Equation (3.27)

$$-i_{2} = g_{m2} \left[ V_{1} + \frac{g_{m1}V_{1-}V_{2} [g_{m1} + sC\beta_{1}]}{(sC - sC_{z2}) + \frac{1}{R_{z2}}} \right] + V_{2} \left( sC_{z2} + \frac{1}{R_{z2}} \right)$$

(3.27)

$$i_{2} = -g_{m2} \left[ \frac{V_{1} \left[ \left( (sC - sC_{z2}) + \frac{1}{R_{z2}} \right) \right] + \beta_{1}g_{m1}V_{1} - V_{2} \left[ g_{m1} + sC\beta_{1} \right]}{(sC - sC_{z2}) + \frac{1}{R_{z2}}} \right] + V_{2}(sC_{z2} + \frac{1}{R_{z2}})$$

$$\begin{split} i_2 &= \frac{g_{m2}}{(sC - C_{z2}) + \frac{1}{R_{z2}}} \Bigg[ -V_1 \Bigg[ \Bigg[ \bigg( (sC - sC_{z2}) + \frac{1}{R_{z2}} \bigg) \Bigg] + \beta_1 g_{m1} \Bigg] + D \Bigg] \\ &\quad \text{where D} = &V_2 \Bigg[ \left[ g_{m1} + sC\beta_1 \right] + (sC_{z2} + \frac{1}{R_{z2}}) \Bigg( (sC - sC_{z2}) + \frac{1}{R_{z2}} \Bigg) \Bigg] \end{split}$$

Thus from above equation (3.28) and Equation (3.26), we can infer that Equivalent impedance is affected by parasitic elements of VDIBA.

### **CHAPTER 4**

### **SIMULATION RESULTS**

VDIBA CMOS circuit is simulated using TSMC 0.25-µm real transistor model and the corresponding dimensions of VDIBA transistors are mentioned in below Table [64].

| Transistors | $\frac{W}{L}(\mu m)$ |

|-------------|----------------------|

| M1-M2       | $\frac{2.5}{0.25}$   |

| M3-M4       | $\frac{2.5}{0.25}$   |

| M5-M6       | $\frac{75}{0.25}$    |

Table I: Dimensions of VDIBA CMOS transistors

Supply voltage of  $V_{dd} = -V_{ss} = 0.75$  V, along with DC biasing current of  $I_{bias} = 100$ mA are used which corresponds to  $g_m = 336 \frac{uA}{V}$ . The  $g_m$  value is controllable through external biasing DC current  $I_{bias}$  based on the following expression:

$$\mathbf{g_m} = \sqrt{\mu \, C_{ox} \frac{\mathbf{W}}{\mathbf{L}} \mathbf{I_{bias}}} \tag{4.1}$$

Where  $\mu$  represents carrier mobility,  $C_{ox}$  represents the gate capacitance per unit area, L and W are the effective channel length and width of transistors and  $I_{bias}$  is the DC biasing current.

#### 4.1 VDIBA Block Simulation Results

VDIBA DC transfer characteristics [60] are shown in Fig. 4.1- Fig. 4.3

Fig. 4.1 I<sub>Z</sub> vs V<sub>p</sub> curve

Fig. 4.2  $I_Z$  vs  $V_n$  curve

Fig. 4.3  $V_{w-}$  vs  $V_z$  curve

#### VDIBA AC transfer characteristics shown in Fig. 4.4

Fig. 4.4 Transconductance Gain of VDIBA ( $g_m = 339 \frac{uA}{V}$ )

## 4.2 Proposed Lossy Series Inductor Simulation Results

For simulation of floating lossy series inductor of Fig. 3.1, the component values were selected as C = 150 pF and  $R = 3k\Omega$ .

1. The biasing current of the CMOS VDIBA is set to  $I_{bias}=100\mu A$  to obtain the value of  $g_m=336\mu A/V(approx)$  (from equation).

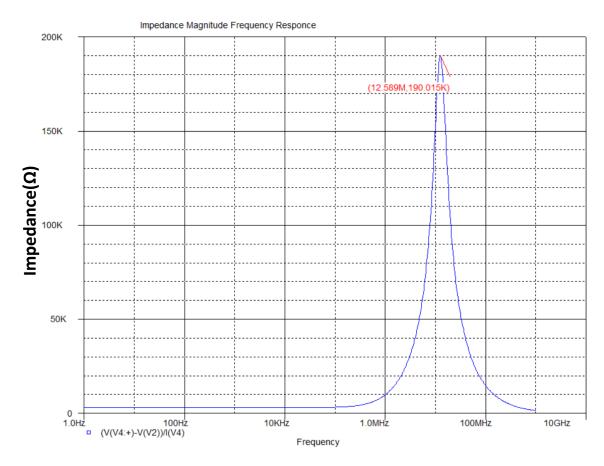

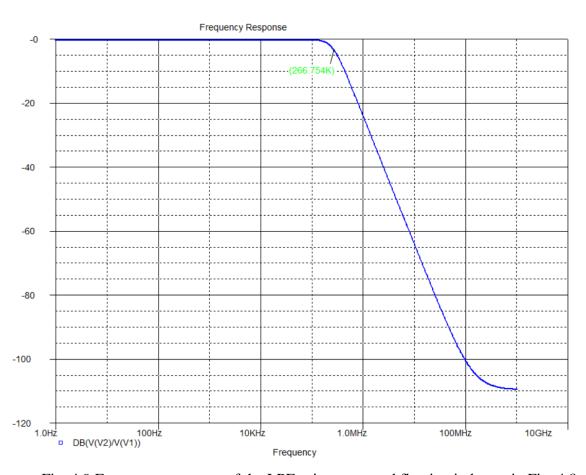

Fig. 4.5 Impedance magnitude–frequency response of Fig. 3.1 for  $I_{\text{bias}} = 100 \mu A$

In above simulation,

- $Z_{eq} = 4.9k$  is obtained through simulation at frequency of 266.65kHz

- On carrying out theoretical calculations,  $Z_{eq} = 4.5k$  is obtained at 266.65kHz frequency.

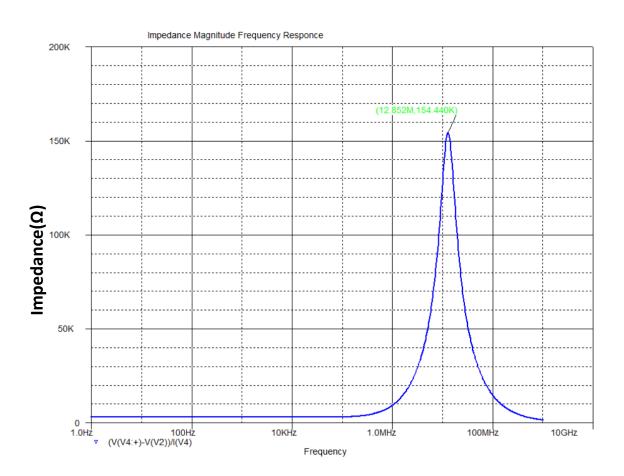

2. The biasing current of the CMOS VDIBA is set to  $I_{bias}=120\mu A$  to obtain the value of  $g_m=354.387\mu A/V$ .

Fig. 4.6 Impedance magnitude–frequency responses of Fig. 3.1 for  $I_{\text{bias}} = 120 \mu A$

In above simulation,

- $Z_{eq} = 5.3k$  is obtained through simulation at frequency of 504.11kHz

- On carrying out theoretical calculations,  $Z_{eq} = 4.9k$  is obtained at 504.11kHz frequency.

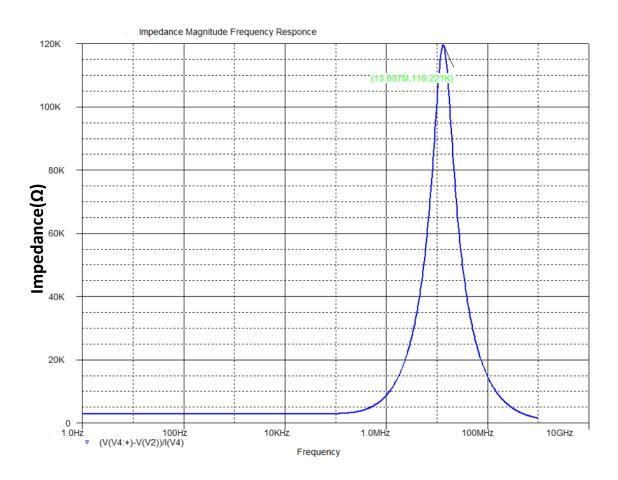

3. The biasing current of the CMOS VDIBA is set to  $I_{bias}=120\mu A$  to obtain the values of  $g_m=375.335\mu A/V$ .

Fig. 4.7 Impedance magnitude–frequency responses of Fig. 3.1 for  $I_{bias}=150\mu A$

From above cases, it is seen that simulated and theoretical results are in close agreement between 1 kHz and 1 MHz frequency range.

#### 4.3 Workability Example for proposed series Inductor

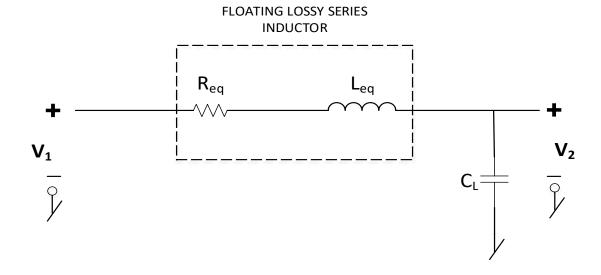

To check the workability of proposed floating series inductor of Fig. 3.1, it is applied in active RLC second order low pass filter as depicted in Fig 4.8. The corresponding transfer function of the designed filter is given as in Equation (4.2) below:

$$V_2 = \frac{\left(\frac{1}{L_{eq}C_L}\right)V_1}{s^2 + s\left(\frac{R_{eq}}{L_{eq}}\right) + \frac{1}{L_{eq}C_L}} \tag{4.2}$$

Whose cut off frequency is described as:

$$\omega_o = \sqrt{\frac{1}{L_{eq}C_L}} \tag{4.3}$$

and quality factor is denoted as:

$$Q = \frac{1}{R_{eq}} \sqrt{\frac{L_{eq}}{C_L}} \tag{4.4}$$

Fig. 4.8 RLC low-pass filter realized with the floating inductor in Fig. 3.1

The component values used for realizing filter are:  $C=150pF,\,R=3k\Omega$  and  $C_L\!\!\equiv\!265pF.$

• For  $I_{bias} = 100 \mu A$

Fig. 4.9 Frequency response of the LPF using proposed floating inductor in Fig. 4.8

Practical Cut off frequency = 266.65 kHz (from simulation)

Theoretical Cut off frequency = 267.2 kHz (from equation (4.3))

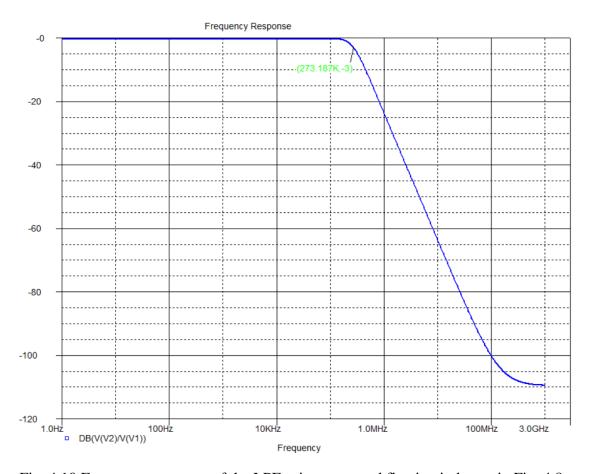

• For  $I_{bias} = 120 \mu A$

Fig. 4.10 Frequency response of the LPF using proposed floating inductor in Fig. 4.8

Practical Cut off frequency of filter = 273.18 kHz (from simulation)

Theoretical Cut off frequency of filter = 274.5 kHz (from Equation (4.3))

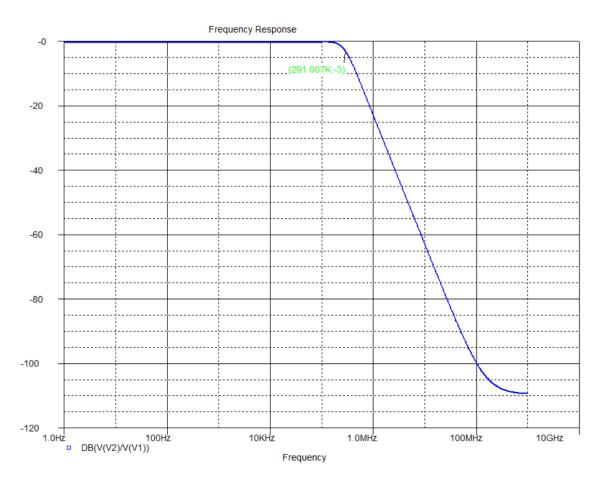

• For  $I_{bias} = 150 \mu A$

Fig. 4.11 Frequency response of the LPF using proposed floating inductor in Fig. 4.8

Practical Cut off frequency = 291 kHz

Theoretical Cut off frequency = 284 kHz

From above different analysis , we can see see the tunability of cut off frequency with  $g_m$ . Thus above analysis verifies the workability of the proposed floating inductor within a relative error range of +- 5%.

#### 4.4 Workability Example for Proposed Parallel Inductor

To confirm the workability, the proposed lossy floating parallel inductor of Fig. 3.3 is used to implement the active resonant circuit depicted in Fig. 4.12 whose angular frequency and the quality factor are given by:

$$\omega_o = \sqrt{\frac{1}{L_{eq}C_L}} \text{ and } Q = \frac{1}{R_{eq}} \sqrt{\frac{L_{eq}}{C_L}}$$

(4.5)

Fig. 4.12 Active Resonant circuit realized with the floating inductor of Fig. 3.3

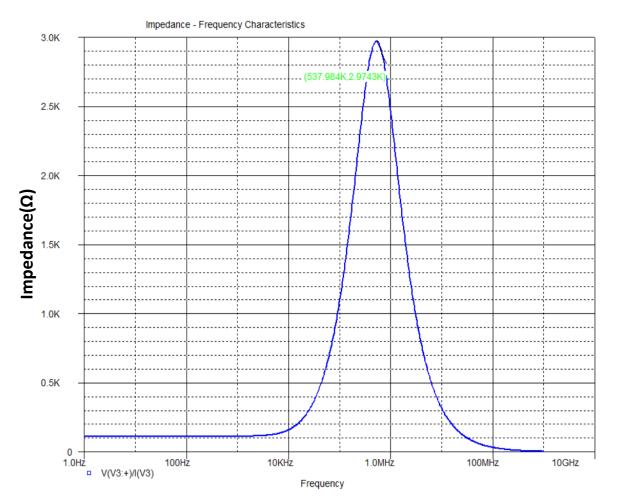

A) For

$$I_{bias1} = 120$$

mA and  $I_{bias2} = 100$ mA and  $C_L = 50$ pF

Practical Cut off frequency,  $f_o = 537.984kHz$  (from simulation)

Theoretical Cut off frequency,  $f_t = 550.646$ kHz (from Equation (4.5))

Fig. 4.13 Impedance- Frequency response of the parallel resonance circuit for VDIBA Biasing Currents.

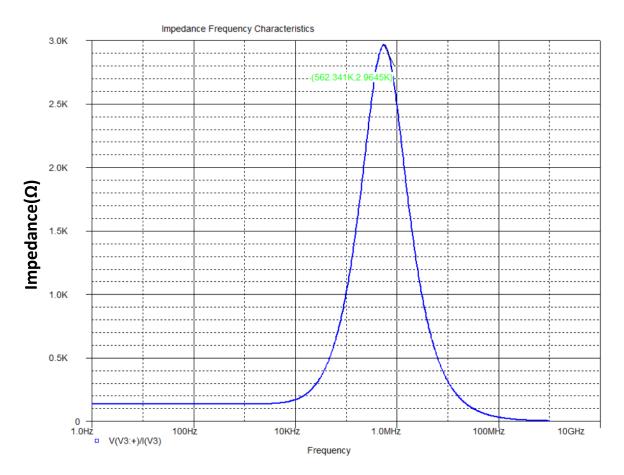

B) For

$$I_{bias1} = 150$$

mA and  $I_{bias2} = 100$ mA and  $C_L = 50$ pF

Practical Cut off frequency,  $f_p = 562.341kHz$  (from simulation)

Theoretical Cut off frequency,  $f_t = 566.27 \mathrm{kHz}$  (from equation 4.5)

Fig. 4.13 Impedance Frequency response of the parallel resonance circuit for VDIBA Biasing Currents.

Thus, from above analysis, Electronic tuning of cut off frequency through Bias current confirms the workability of the proposed floating inductor parallel circuit.

# 4.5 Comparison of Proposed Floating Inductors with Previously Published Inductors:

Comparison of various performance parameters of proposed inductance simulator with the previous known simulators in the literature is shown in Table II.

| INDUCTOR | REFERENC  | ACTIVE   | PASSIVE  | INDUCTOR           | ELECTRO |

|----------|-----------|----------|----------|--------------------|---------|

| TERMINAL | E         | BLOCK    | ELEMEN   | CONFIGURATIO       | NIC     |

|          |           | COUNT    | T COUNT  | N                  | TUNING  |

| Floating | [65]      | OTA=1    | R=2, C=1 | Series RL          | No      |

|          |           | OTA=1,   |          | PARALLEL - RL      |         |

|          |           | OA>=2    |          |                    |         |

| Floating | [66]      | CFOA=2   | R=3, C=1 | Lossless Parallel- | No      |

|          |           |          |          | RL                 |         |

| Floating | [1]       | CFOA=2   | R=2, C=1 | Series RL,         | No      |

|          |           |          |          | Parallel-RL        |         |

| Floating | [41]      | CCII+=2, | R=2, C=1 | Series RL,         | No      |

|          |           | CCII-=1  |          | Parallel-RL        |         |

| Floating | [67]      | DDCC =1  | R=2, C=1 | Series-RL          | No      |

| Grounded | [68]      | VDBA=1,  | C=1      | Series RL,         | Yes     |

|          |           | MOS=1    |          | Parallel RL        |         |

| Floating | [69]      | DVCC=2   | R=2, C=1 | Lossless           | No      |

| Floating | [70]      | VDBA=2   | C=1      | Lossless           | Yes     |

| Floating | [71]      | CCII+=2, | R=2, C=1 | Lossless           | no      |

|          |           | CFOA=1   |          |                    |         |

| Floating | Proposed  | VDIBA=2  | R=1, C=1 | Series-RL,         | Yes     |

|          | Inductors |          |          | ParallelRL         |         |

Table II: Proposed Circuit comparison with other Simulators

From the table it can be seen that inductors configurations in [65], [41] and [72] employ more number of active devices and simulators in [66], [69], [71] employ more number of passive components that the proposed simulator along with no tuning feasibility.

#### **CONCLUSION**

Among various modern active building blocks, VDIBA is emerging as quite flexible and versatile building block for analog circuit design. Alternative simple single capacitor based lossy floating inductance circuits (series and parallel) are presented employing two VDIBAs along with one passive resistor and capacitor each.

Inductance value in both floating inductors is electronically controllable in parallel RL circuit whereas it is controllable through resistor in series RL circuit. The synthetic lossy inductor and its application have been evaluated by employing PSPICE simulation for the TSMC 0.25-um CMOS technology. One NMOS transistor (in triode region) can be used which can act as Voltage controlled linear resistor (VCR) by which inductance value can also be tuned electronically.

#### **REFERENCES**

- [1] D. R. Bhaskar and R. Senani, "Synthetic Floating Inductors realized with only two Current Feedback op-amps," American Journal of Electrical and Electronic Engineering, vol. 3, no. 4, pp. 88-92, 2015.

- [2] R. Senani, "Novel active-RC circuit for floating inductor simulation," IEEE Electronics Letters, 15(21), pp. 679-680, Oct. 1979.

- [3] R. Senani, "New tunable synthetic floating inductors," IEEE Electronics Letters, 16(10), pp. 382-383,1980.

- [4] R. Senani, "Floating ideal FDNR using only two current conveyors", IEEE Electronics Letters, 20(5), pp. 205-206, 1984.

- [5] A. W. Keen and (Miss) J. L. Peters, "Inductance simulation with a single differential input operational amplifier," Electronics letters, vol. 3, no. 4, March 1967.

- [6] R.H.S. Riordan, "Simulated inductors using differential amplifiers," Electronics letters, vol. 3, no. 2, December 1967.

- [7] D. F. B. Suhash and C. D. Roy, "Inductor simulation using a single unity gain amplifier," IEEE journal of solid-state circuits, June 1969.

- [8] K. R. Rao and S. Venkateshwara, "Synthesis of inductors and gyrators with voltage-controlled voltage sources," Electronics letters, vol. 6, no. 2, 22nd January 1970.

- [9] A. Antoniou, "Floating negative-impedance converters," IEEE transactions on circuit theory, March 1972.

- [10] D. R. Wise, "Active simulation of floating lossy inductances," Proc. IEE, vol. 121, no.2, February 1974.

- [11] S. C. D. Roy, "A circuit for floating inductance simulation," Proceedings of the IEEE, April 1974.

- [12] R. Senani, "Realization of single-resistance controlled lossless floating inductance," Electronics letters, vol.14, no. 25, 7th December 1978.

- [13] P. Horn and G. S. Moschytz, "Active RC single-Opamp design of driving point inductance," IEEE transactions on circuits and systems, vol. cas-26, no. 1, January 1979.

- [14] V. Singh, "New floating-point impedance simulation using operational amplifiers," IEEE proceedings, vol. 135, no. 3, June 1988.

- [15] R. Senani and J. Malhotra, "Minimal realizations of a class of operational mirrored-amplifier-based floating impedances," Electronics letters, vol. 30, no. 14, 7th July 1994.

- [16] Abdullah, "Inductor simulation with operational devices," G.U. J. Sci., 18(1):143151 (2005)/ Abdullah FERİKOĞLU, Taner TOPAL, 2005.

- [17] E. Yuce and S. Minaei, "A modified CFOA and its applications to simulated inductors, Capacitance multipliers, and Analog filters," IEEE transactions on circuits and systems-I: Regular papers, vol. 55, no. 1, February 2008.

- [18] U. Cam, F. Kacar, O. Cicekoglu, H. Kuntman and A. Kuntman, "Novel two OTRA-based grounded immittance simulator topologies," Analog integrated circuits and signal processing, 39, pp. 169–175, 2004.

- [19] R. Banchuin, B. Chipipop and B. Sirinaovakul, "The complete passive equivalent circuit of the practical OTA-based floating inductor," Department of Microelectronics & Computer science, Technical University of Lodz, 2006.

- [20] W. Jaikla and M. Siripruchyanant, "Floating Positive and Negative Inductance simulators based on OTAS," ISCIT, 2006.

- [21] R. Banchuin, B. Chipipop and B. Sirinaovakul, "Novel practically applicable passive equivalent circuit model of the alternatively structured higher performance practical OTA-based floating Inductor," Proceedings of 2007 International symposium on intelligent signal processing and communication systems, Xiamen, China, December 2007.

- [22] M. Pierzchala and M. Fakhfakh, "Generation of active inductor circuits," IEEE, 2011.

- [23] M. Kumngern, "New positive/negative floating inductance simulation using OTA AND CCCII", IEEE symposium on wireless technology and applications, September 2011.

- [24] A. Thanachayanont and A. Payne, "VHF CMOS Integrated active inductor". Electronics letters, vol. 32, no. 11, May 1996.

- [25] A. Thanachayanont and A. Payne, "CMOS floating active inductor and its applications to band pass filter and oscillator designs," IEE proc.-circuits devices systems, vol. 147, no. 1, February 2000.

- [26] A. Thanachayanont, "A 1.5 V high-Q CMOS active inductor for few wireless applications," IEEE, 2000.

- [27] J. B. Yoon, Y. S. Choi, B. I. Kim, E. Yunseong and E. Yoon, "CMOS-compatible surface Micromachined suspended-spiral inductors for multi-Ghz silicon RF ICs," IEEE electron device letters, vol.23, no.10, October 2002.

- [29] W. Jaikla and M Siripruchyanan, "Current controlled CDTA (CCCDTA) based-novel floating and grounded inductance simulators," ISCIT, 2006.

- [30] L. A. Said, A. H. Madian, M. H. Isamil and A. M. Soliman, "CMOS digitally programmable lossless floating inductor," IEEE International Conference of Electron Devices and Solid-State Circuits (EDSSC), 2010.

- [31] S. Wang and R. X. Wang, "Q-enhanced CMOS inductor using tapped-inductor feedback," Electronics letters, vol. 47, no. 16, August 2011.

- [32] U. E. Ayten, M. Sagbas, N. Herencsar and J. Koton, "Novel floating FDNR, inductor and capacitor simulator using CDTA," IEEE, 2011.

- [33] P. S. Manhas and K. Pal, "A low voltage active circuit for realizing floating inductance, capacitance, frequency dependent negative resistances and admittance converter," Arab J Sci Eng, 36:1313–1319, October, 2011

- [34] A. Sedra and K. C. Smith, "A second-generation current conveyor and its applications," IEEE transaction on circuit theory, February 1970.

- [35] A. M. Soliman, "A grounded inductance simulation using the DVCCS/DVCVS," Proceedings of the IEEE, vol. 66, no. 9, 1978.

- [36] R. Nandi, "Active inductances using current conveyors and their application in a simple bandpass filter realization," Electronics letters vol.14, no. 12, September 1978.

- [37] R. Senani, "Active simulation of inductors using current conveyor," Electronics letters, vol. 14, no. 15, 1978.

- [38] V. Singh, "A new active-RC circuit realization of floating inductance". Proceedings of the IEEE, vol. 67, no. 12, December 1979.

- [39] R.Senani, "Novel active RC realizations of tunable floating inductors," Electronics letters, vol. 16, no. 4, February 1980.

- [40] R.Senani, "Novel lossless synthetic floating inductor employing a grounded capacitor," Electronics letters, vol. 18, no. 10, March 1980.

- [41] R. Senani, "New tunable synthetic floating inductors," Electronics letters, vol. 16, no. 10, 24th March 1981.

- [42] A. N. Paul and D. Patranabis, "Active simulation of grounded inductors using a single current conveyor," IEEE transactions on circuits and systems, vol. CA. 28, no. 2, 1981.

- [43] K. Pal, "New inductance and capacitor floatation schemes using current conveyors," Electronics letters, vol. 17, no. 21, 1981.

- [44] V. Singh, "Active RC single-resistance controlled lossless floating inductance simulation using single grounded capacitor," Electronics letters, vol.17, no. 24, November 1981.

- [45] M. Higashimura and Y. Fukui, "Novel method for realizing lossless floating immittance using current conveyors," Electronics letters, vol. 23, no. 10, May 1987.

- [46] I. Haritantis and M. C. Layos, "Second order current mode circuits based on the general current conveyor," ICECS, 1996.

- [47] S. Minaei, E. Yuce and O. Cicekoglu, "Lossless active floating inductance simulator," Electronics letters, vol. 39, no. 35, 2005.

- [48] E. Yuce, "On the realization of the floating simulators using only grounded passive components," Analog integrated circuits signal process 49, pp. 161–166, September 2006.

- [49] B. Maundy, S. Gift and P. Aronhime, "A novel hybrid active inductor," IEEE transactions on circuits and systems, vol. 54, no. 8, August 2007.

- [50] E. Yuce, "Grounded inductor simulators with improved low frequency performances," IEEE transactions on instrumentation and measurement, vol. 57, No. 5, May 2008.

- [51] R. Nandi, M. Kar, S. Das, "Synthetic inductor-based resonators using DVCCTA," IEEE, 2011.

- [52] R. Senani and J. Malhotra, "Minimal realizations of a class of operational mirrored amplifier based floating impedance," Electronics Letters, vol. 30, no. 14,1994.

- [53] W. Kiranon and P. Pawarangkoon, "Floating inductance simulation based on current conveyors," Electronics Letters, vol. 33, pp. 1748-1749, 1997.

- [54] W. Tangsrirat and W. Surakampontorn, "Electronically tunable floating inductance simulation based on current controlled current differencing buffered amplifiers," Thammasat International Journal of Science and Technology, vol. II, no. 1, pp. 60-65,2006.

- [55] U. E. Ayten, M. Sagbas, N. Herencsar and J. Koton, "Novel general element simulators using CBTA," Radio engineering, vol.21, no.1, pp.11-19, April 2012.

- [56] U. Keskin and H. Erhan, "CDBA-based synthetic floating inductance circuits with electronic tuning properties," ETRI Journal, vol. 27, no. 2, pp. 239-242,2005.

- [57] D. Prasad, D. R. Bhaskar and A. K. Singh, "New grounded and floating simulated inductance circuits using current differencing transconductance amplifiers," Radio engineering, vol. 19, no. I, pp. 194-198, 2010.

- [58] E. Yuce, "On the realization of the floating simulators using only grounded passive components," Analog Integrated Circuits and Signal Processing, vol. 49, pp. 161-166,2006.

- [59] D. Biolek, R. Senani, V. Biolkova and Z. Kolka, "Active Elements for analog signal processing: Classification, review, and new proposals," Radio engineering, vol. 17, iss. 4, pp. 15-32., 2008.

- [60] N. Herencsar, S. Minaei, J. Koton, E. Yuce, and K. Vrba, "New resistor less and electronically tunable realization of dual-output VM all-pass filter using VDIBA," Analog Integrated Circuits and Signal Processing, vol. 74, no. 1, pp. 141-154, 2013.

- [61] C. M. Chang and C. S. Hwang, 'Comment on Voltage mode notch, low pass and band pass filter using current feedback amplifier," IEE Electron. Lett, 31(4), 246, Feb. 1995.

- [62] C. Acar and S. Ozoguz, "A new versatile building block: current differencing buffered amplifier suitable for analog signal processing filters," Microelectron. J., vol. 30, no. 2, pp. 157–60, Feb. 1999.

- [63] W. Tangsrirat , K. Klahan, T. Dumawipata and W. Surakampontorn, "Low-voltage NMOS-based current differencing buffered amplifier and its application to current-mode ladder filter design," International Journal of Electronics, 93(11), pp. 777-791, 2007.

- [64] A. Sheikh, B. A. Ganai, N. Shah and F. Khanday, "Current Differencing Buffered Amplifier Based Voltage Mode Multifunction Biquad," International Journal of Advanced Scientific Research and Technology, vol. 2, pp. 349-354, June 2012.

- [65] R. Senani, "New Single capacitor simulation of floating inductors," Electro Compton. Sci. Technol., vol. 10, pp. 7-12, March 1982.

- [66] R. Senani and D. R. Bhaskar, "New lossy/loss-less synthetic floating inductance configuration realized with only two CFOA's," Analog Integr. Circ. Sig. Process., vol 73, pp. 981-7, June 2012.

- [67] E. Yuce, "New Low component count floating inductor simulators consisting of a single DDCC," Analog Integr. Circ. Sig. Process., vol. 58, pp. 61-66, Jan. 2009.

- [68] W. Tangsrirat, "Synthetic grounded lossy inductance simulators using single VDBA," IETE J. Res., Vol. 63, no.1, pp. 134-41, Jan- Feb 2017.

- [69] H. Sedef and M. Koksal, "A new floating FDNR circuit using differential voltage current conveyors," Int. J. Electron. Commum.(AEU), vol.54, no. 5, pp. 297-301, May 2000.

- [70] E. Yuce, "A novel floating simulation topology composed of only grounded passive components," Int. J. Electron., Vol. 97, no. 3, pp. 249-62, March 2010.

- [71] E. Yuce and S. Minaei, "Novel Floating simulated inductors with wider operating frequency ranges," Micro-electronics Journal, vol. 40, no.6, pp. 928-38, Jun. 2009.