# ANALYTICAL MODELING AND TCAD SIMULATION OF IN<sub>2</sub>O<sub>5</sub>SN TRANSPARENT GATE ELECTRODE RECESSED CHANNEL MOSFET FOR HIGH PERFORMANCE APPLICATIONS

Thesis Submitted by

### **AJAY KUMAR**

In Fulfillment of the Requirements for the Degree of

#### **DOCTOR OF PHILOSOPHY**

Under the Supervision of

PROF. M. M. TRIPATHI &

DR. RISHU CHAUJAR

ELECTRICAL ENGINEERING DEPARTMENT

DELHI TECHNOLOGICAL UNIVERSITY

MARCH 2019

# Dedicated to.... My Family

#### **Delhi Technological University**

(Govt. of National Capital Territory of Delhi) Bawana Road, Delhi-110042

### **CERTIFICATE**

This is to certify that the thesis titled "Analytical Modeling and TCAD Simulation of In<sub>2</sub>O<sub>5</sub>Sn Transparent Gate Electrode Recessed Channel MOSFET for High Performance Applications" is being submitted by Mr. AJAY KUMAR with registration number 2K16/PHD/EE/05 to the Delhi Technological University for the award of the degree of Doctor of Philosophy in Electrical Engineering Department. The work embodied in this thesis is a record of bonafide research work carried out by him in the Microelectronics Research Lab, Applied Physics Department, Delhi Technological University (Formerly Delhi College of Engineering), New Delhi under the guidance of Prof. M. M. Tripathi and Dr. Rishu Chaujar. It is further certified that this work is original and has not been submitted in part or fully to any other University or Institute for the award of any degree or diploma.

Ajay Kumar

Roll No.2K16/PHD/EE/05

This is to certify that the above statement made by the candidate is correct to the best of our knowledge.

Prof. Madhusudan Singh

Head & DRC Chairman

Electrical Engineering Department

Delhi Technological University

Delhi, India

Prof. M. M. Tripathi

Supervisor (Professor)

Electrical Engineering Department

Delhi Technological University

Delhi, India

Dr. Rishu Chaujar Supervisor (Associate Professor) Department of Applied Physics Delhi Technological University Delhi, India During three years of my research work, several people support with their valuable suggestions and make my research a wonderful journey. I would like to take this opportunity to acknowledge them.

First and foremost, I would like to express my sincere gratitude to my supervisor, mentor **Dr. Rishu Chaujar** and **Prof. M.M. Tripathi** for their constant encouragement, support, and guidance at every stage of my research time. They provided me every opportunity to present my work at important conferences and in industry. I especially thank for prompt reading and careful review of my thesis.

I am thankful to **Prof. Yogesh Singh**, Vice Chancellor, Delhi Technological University, **Prof. Madhusudan Singh**, HOD, Electrical Engineering Department, DTU and **Prof. S. C. Sharma**, Applied Physics Department, DTU for their generous support and providing ample infrastructure to carry out my research work. I further thanks to SRC and DRC members **Prof. Madhusudan Singh** (**Chairman DRC**), **Prof. Harsupreet Kaur** (**External Expert**), for taking their decisive time serving in my committee and giving me treasured recommendations on my thesis.

I wish to express my deepest gratitude to my beloved wife Dr. Neha Gupta for her important, perceptive comments and suggestions which enhance the quality of my research work. It was her continuous moral support and encouragement without which this thesis would not have been possible. I also express my gratefulness to Dr. Aditya Jain, Dr. Vinay Kumar, Dr. Rakesh Saroha, Dr. Ratneshwar Kumar Ratnesh, Dr. Lucky Krishnia, and Dr. Ashish Gupta for the various discussions we had, both technical and otherwise.

My colleagues, associates, and friends continuously influenced me in a positive way and have an important impact on my thinking. I will always remain

grateful to them for their selfless support. I want to thank Suryakant Shukla, Dr. Prakash Chittora, Dr. Ravi Gupta, Abhishek Bhardwaj, and Hemant Saxena.

To each and every one whom I have met during my time at Microelectronics Research Laboratory: Anuj Chhabra, Samarth Singh, Balark Tiwari, Anuj Sinha, Pawan Singh, Deepak Singh, Bhavya Kumar, and Ardaman Kaur.

I would also like to convey my extreme thanks to all the faculty members and technical staff of Department of Electrical Engineering and Department of Applied Physics for their continuous support.

I would like to thank University Grant Commission (UGC), New Delhi, for providing the financial support to carry out the research work. I would also like to acknowledge the support of Department of Science and Technology (DST) for research work and travel grant.

Last but not least, my father (Ram Sajiwan Verma), my mother (Rani Devi), my brother my ideal (Sanjay Kumar), my sister-in-law (Sheela Verma), my sisters (Seema Verma, Sanno Verma and Sudha Verma), my niece (Vaishnavi Kumar), my mother-in-law (Rajkumari Gupta), my brother-in-law (Nikhil Gupta), my sister-in-law (Diksha Gupta), my nephew (Reyansh Gupta), all my relatives and well-wishers, have always encouraged me and have been by my side in every challenging and tough situation. I am highly grateful towards my parents who have sacrificed boundlessly to make this thesis a success. Also, I would like to thank Dr. Kunwar Singh (Assistant Professor, NSIT, Delhi), Dr. Sachin Umrao, Dr. Shubham Sahay and Dr. Amit Kumar Goyal for their constant support and motivation during my research work.

(Ajay Kumar) New Delhi, March 2019

# Analytical Modeling and TCAD Simulation of In<sub>2</sub>O<sub>5</sub>Sn Transparent Gate Electrode Recessed Channel MOSFET for High Performance Applications

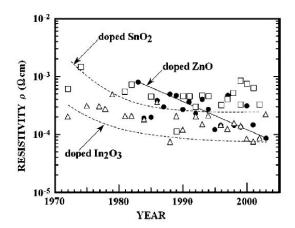

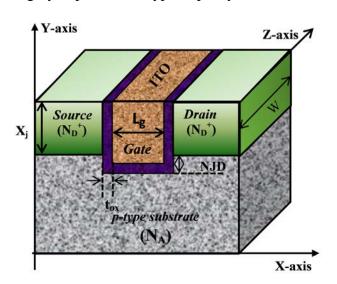

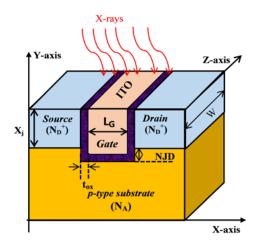

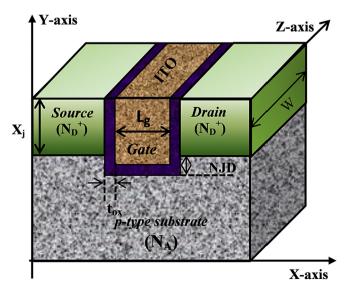

In this era of internet of things (IoT), the scaling of CMOS is playing a vital role. However, scaling of MOSFETs beyond sub-nm regime is extremely challenging for non-planar device architecture owing to rigorous criteria required for the transistor switching. The stringent scaling may lead to static power dissipation due to increase in OFF-state leakage current. Many solutions have been proposed to overcome CMOS scaling bottleneck with different device architectures such as FinFETs, gate all around silicon nanowire (GAA SiNW), recessed channel (RC) MOSFETs and many more. Although many device structures such as GAA SiNW MOSFETs results in suppression of SCEs, it is not easy to fabricate this due to its non-planar architecture. RC MSOFET offers best possible gate control leading to SCEs and fabrication feasibility for IC industries at very low fabrication cost owing to planar architecture. Different gate materials have been used to improve the gate controllability over the channel and among all; indium tin oxide (ITO) is found to be the most suitable gate material. ITO is very feasible for fabrication and has a very low cost. ITO has a very low resistivity ( $10^{-5} \Omega$ -cm) with higher Hall mobility ( $53.5 \text{ cm}^2 \text{ V}^{-1} \text{s}^{-1}$ ). Due to these properties, ITO is frequently used in semiconductor devices and more commonly, for silicon-based MOSFET devices having technology less than 30 nm.

In this thesis, Transparent Gate Recessed Channel (TGRC) MOSFET have been critically scrutinized and compared with the conventional structures using device simulations obtained using ATLAS 3D device simulator. The analysis exemplified that TGRC-MOSFET has overcome the drawbacks faced by the conventional structures and improves the device analog and RF performance owing to trench gate

and ITO metal gate. The improved analog performance and architecture of the device makes it suitable for x-ray dosimeter and bio-sensing applications.

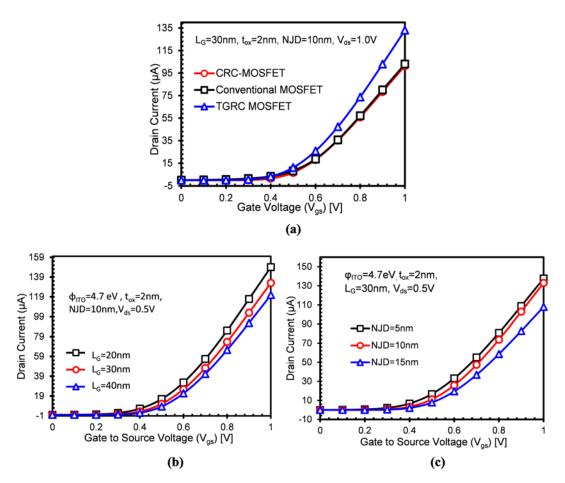

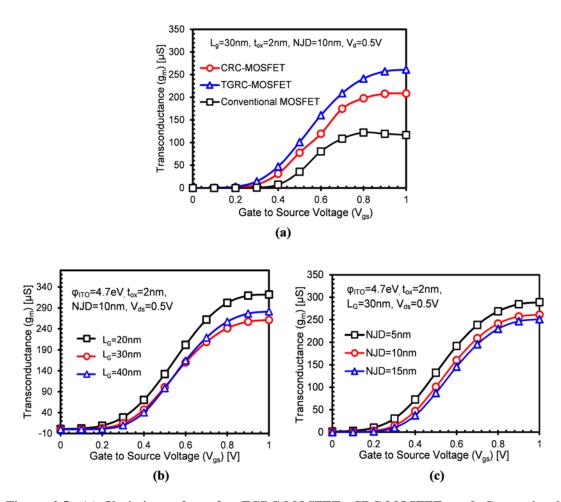

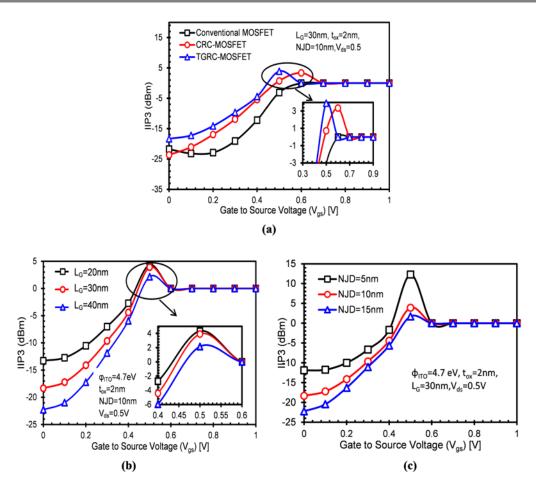

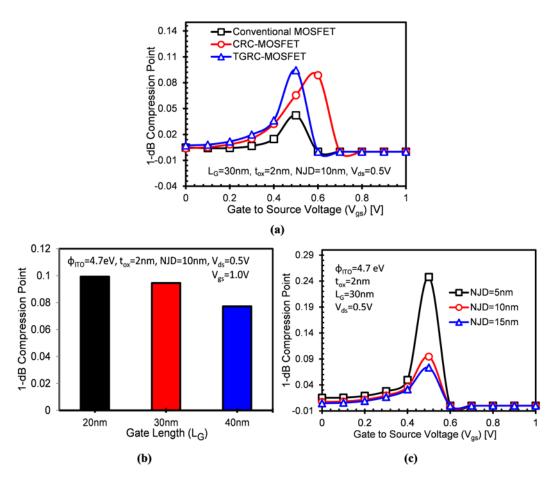

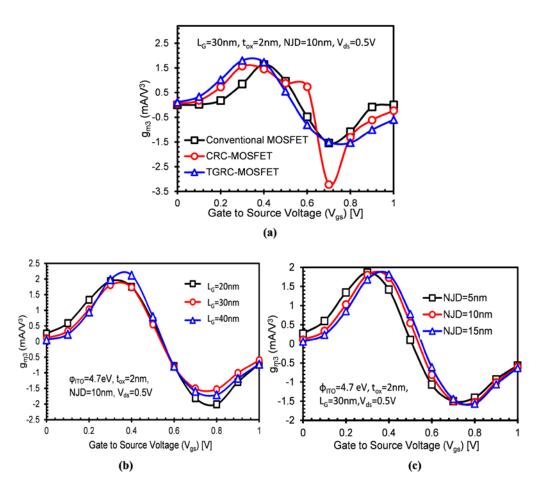

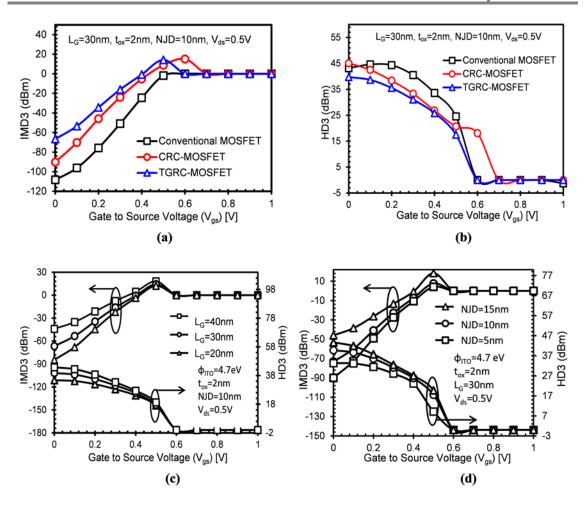

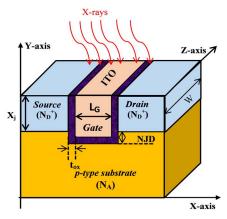

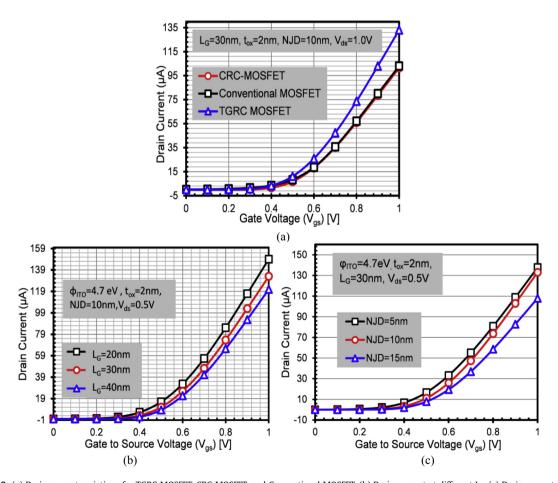

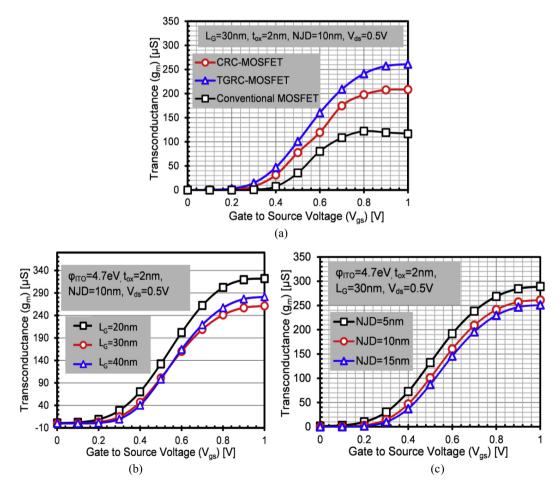

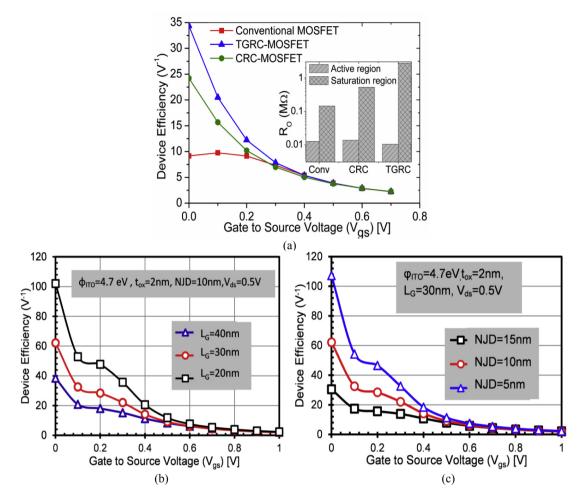

In the beginning, the analog and linearity performance of TGRC-MOSFET has been discussed along with the impact of trench depth [Negative Junction Depth (NJD)] and gate length ( $L_G$ ) with an aim to achieve a reliable and high performance transistor. Proposed device improves the analog performance in terms of transconductance, device efficiency, output resistance, and gain. The improved analog and linearity performance at 5 nm NJD and 20 nm  $L_G$  of TGRC-MOSFET makes it suitable for low power linear RF amplifiers as a nano-scaled device.

Further, the reliability issues of the proposed device have been explored by considering the effect of interface trap charges (both polarity and density) in terms of static, linearity and intermodulation distortion FOMs. It is found that with the amalgamation of ITO on conventional recessed channel (CRC) MOSFET, the proposed device exhibits improved immunity against interface trap charges. In addition, the influence of ambient temperature (150-300K) along with trap charges on TGRC MOSFET has also been explored with an aim to analyse at which temperature the device is more stable in the presence of interface defects (trap charges).

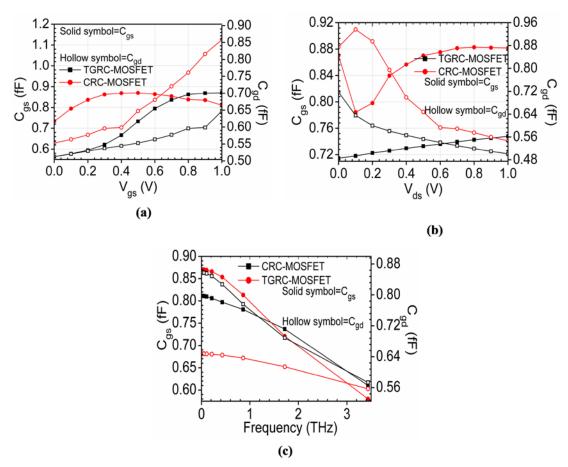

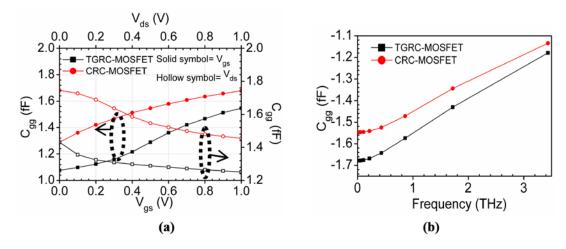

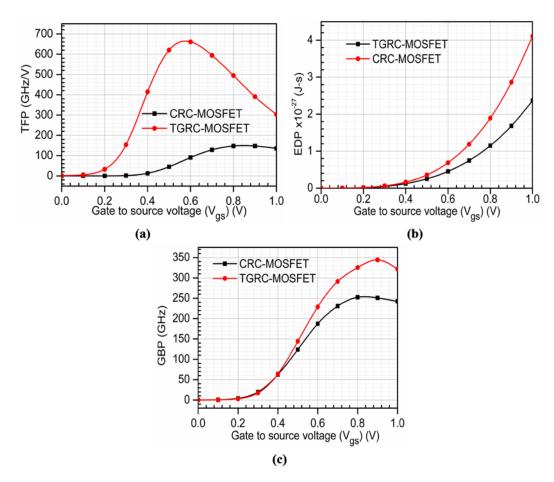

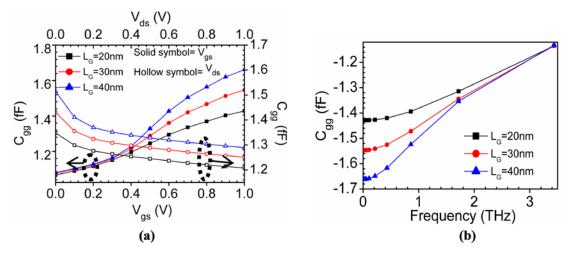

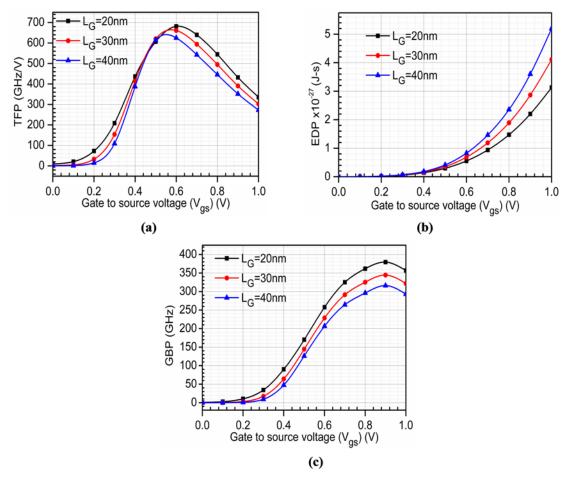

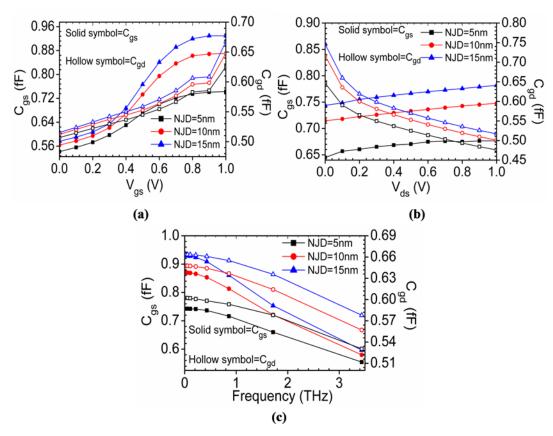

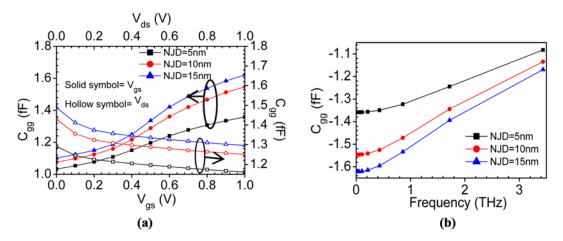

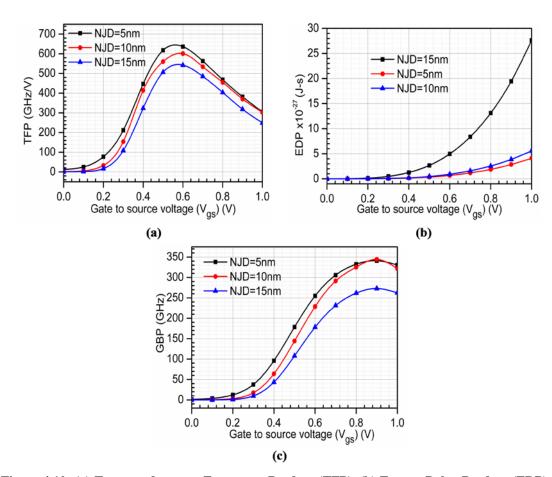

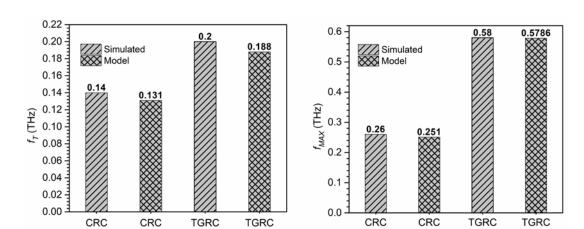

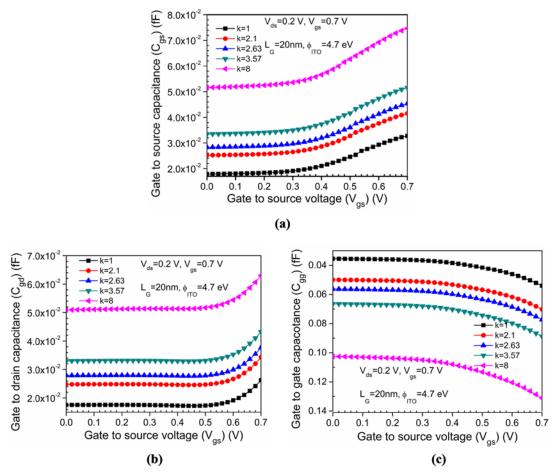

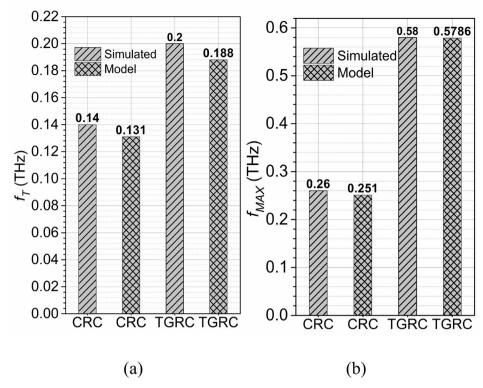

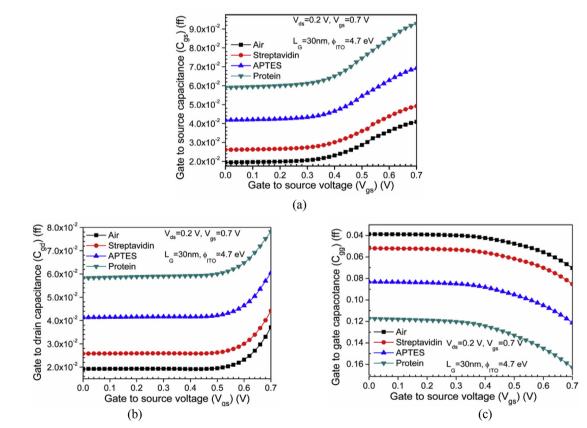

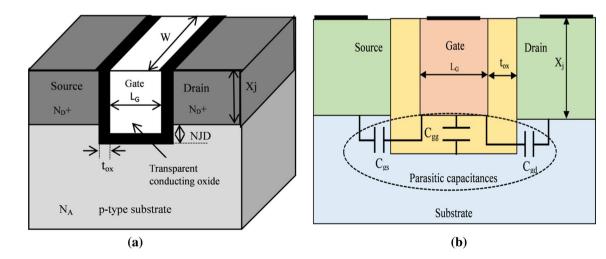

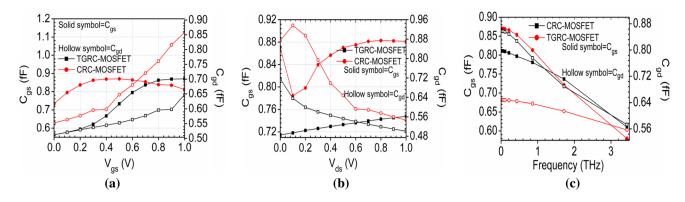

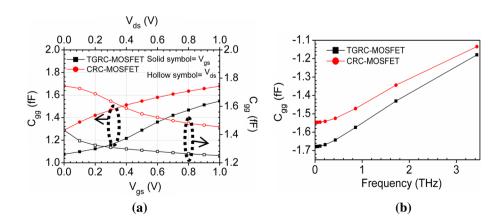

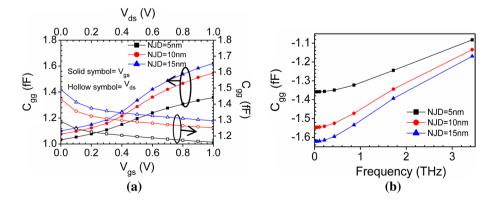

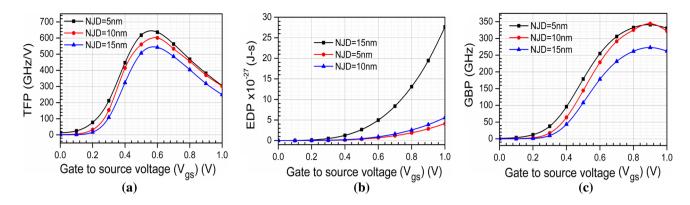

Moreover, capacitance-voltage (C-V) analysis and frequency dependent capacitance have been analysed with an aim to examine the effectiveness of  $In_2O_5Sn$  as a gate material on parasitic capacitance. The capacitance dependent parameters such as Transconductance Frequency Product (TFP), Energy Delay Product (EDP) and Gain Bandwidth Product (GBP) have also been assessed and found that, TFP increases in comparison to metal gate RC MOSFET owing to a noticeable reduction in parasitic capacitance ( $C_{gg}=C_{gs}+C_{gd}$ ), due to which EDP and GBP also improve considerably. In order to provide detailed insight to RF engineers for microwave applications, the small signal RF model has been studied in terms of microwave parameters such as S (scattering) parameters, Z (impedance) parameters, Y (admittance) parameters, and Y (hybrid) parameters with an aim to analyse the behaviour of device at microwave frequency. It has also been observed that the

transit (cut-off) frequency ( $f_T$ ) and maximum oscillator frequency ( $f_{MAX}$ ) enhances significantly owing to the remarkable reduction in intrinsic capacitances.

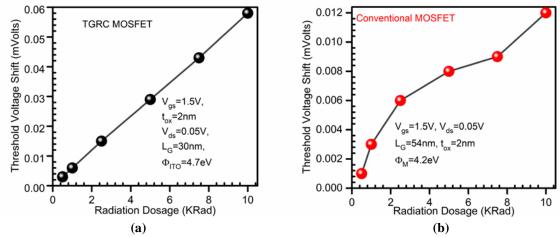

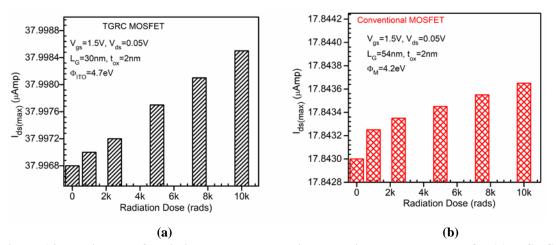

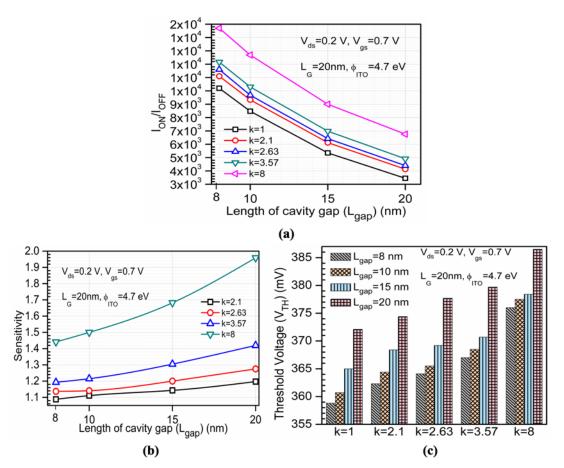

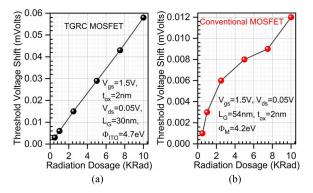

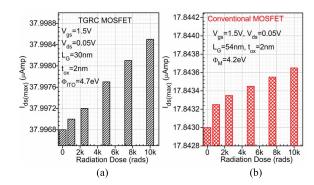

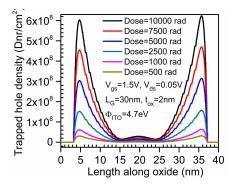

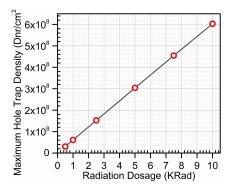

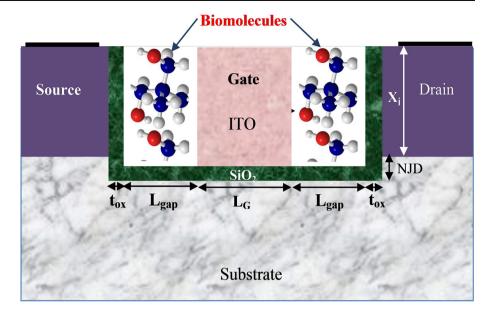

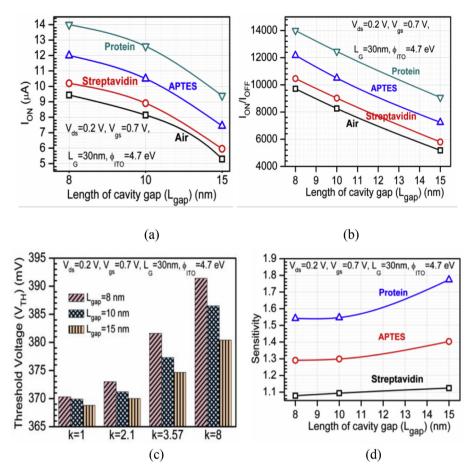

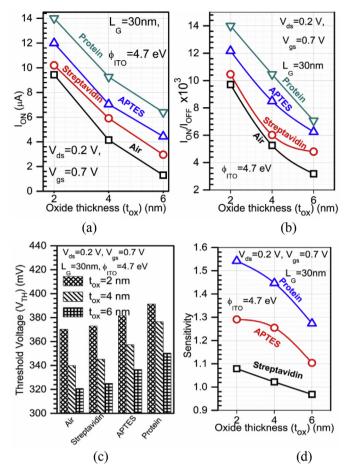

After analysing the enhanced electrical properties of the proposed device, it has been explored for an X-Ray dosimeter as well as a biosensor. In the first application, TGRC-MOSFET has used as an x-ray dosimeter where x-ray radiation in the 0.5k to 10kRad dose range after irradiation has been considered. TCAD simulations for the same have been done to estimate threshold voltage shift in MOSFET with different radiation dosage. Models accounting for electron-hole pair generation and recombination are applied along with trap/de-trap model for insulator as well as interface charging. An improvement in radiation sensitivity has been found on increasing the oxide thickness from 2 nm to 6 nm. Along with signal amplification and processing circuit, this device can find enormous applicability in clinical and space environment. Further, the device applications have been extended and used for bio-sensing application. TGRC-MOSFET comprises a nano-gap cavity for the detection of biomolecules and transparent gate to enhance the overall current efficiency of RC-MOSFET. For the detection of neutral biomolecules, following electrical characteristics were studied: I<sub>ON</sub>/I<sub>OFF</sub>, shift in threshold voltage, change in surface potential and hereafter, calculate the sensitivity of the biosensor. In addition, TGRC noise immunity has been evaluated in the presence of biomolecules.

Thus, the high current switching ratio, lower I<sub>OFF</sub>, lower SS, superior RF performance, temperature robustness, and better reliability in terms of ITCs makes TGRC-MOSFET, a promising candidate for employing in a low power, high switching speed and high performance applications even at wide temperature range.

# LIST OF FIGURES

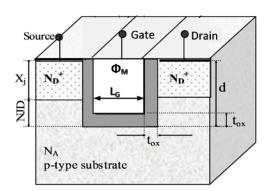

| Figure 1.1: Schematic structure of Conventional MOSFET                                                                                                                                                                                                                       |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 1.2: Drain Induced Barrier Lowering.                                                                                                                                                                                                                                  |

| Figure 1.3: Cross-Sectional View of n-channel MOSFET showing Injection of Hot-Carriers due to shortening of channel length                                                                                                                                                   |

| Figure 1.4: Different schemes to alleviate SCEs in nano-scale MOSFET                                                                                                                                                                                                         |

| Figure 1.5: Silicon-On-Insulator MOSFET                                                                                                                                                                                                                                      |

| Figure 1.6: Double-Gate MOSFET9                                                                                                                                                                                                                                              |

| Figure 1.7: Schematic view of both planar MOSFET and FinFETs                                                                                                                                                                                                                 |

| Figure 1.8: Cross-sectional view of cylindrical gate MOSFET with the coordinate system                                                                                                                                                                                       |

| Figure 1.9: Schematic cross-sectional view of Conventional Recessed Channel MOSFET14                                                                                                                                                                                         |

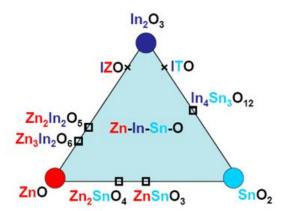

| Figure 1.10: TCO semiconductors for thin film transparent electrodes                                                                                                                                                                                                         |

| Figure 1.11: Reported resistivity of impurity-doped binary compound TCO films                                                                                                                                                                                                |

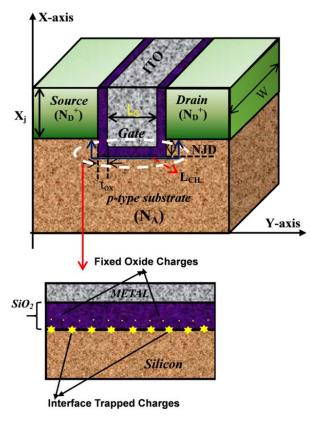

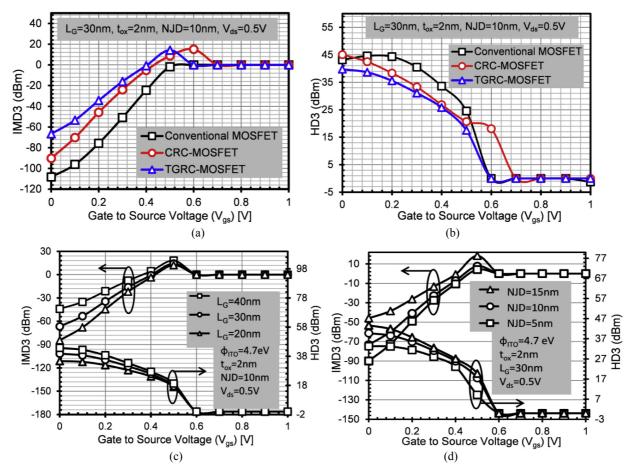

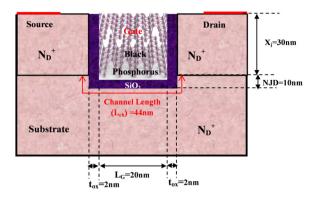

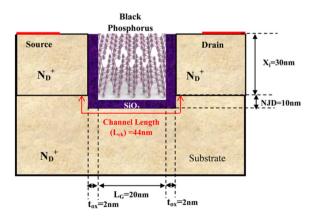

| Figure 2.1: 3-D device structure of TGRC-MOSFET                                                                                                                                                                                                                              |

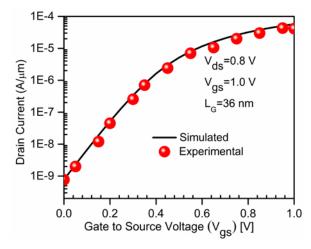

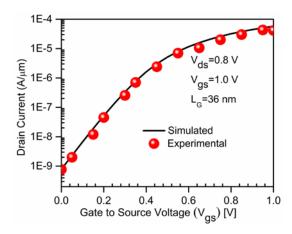

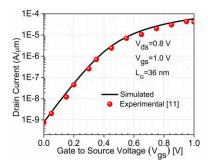

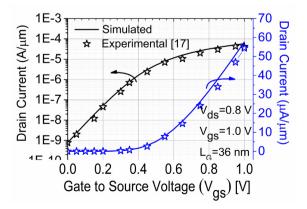

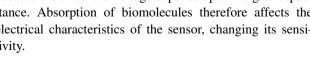

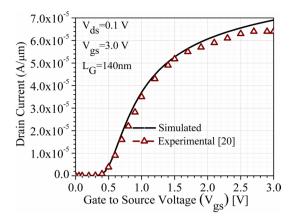

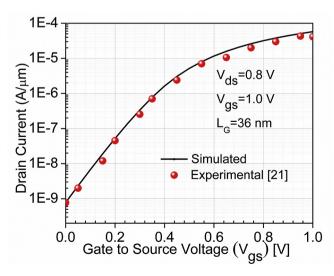

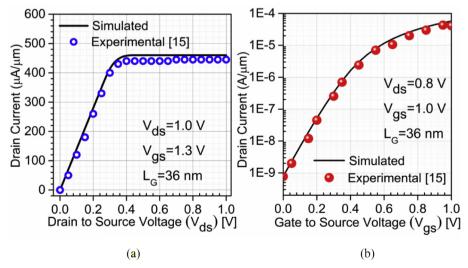

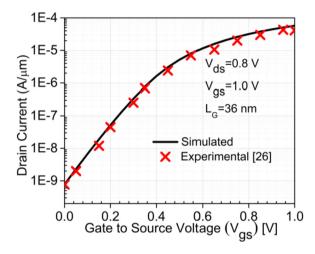

| Figure 2.2: Calibrated transfer characteristics of recessed channel MOSFET (36 nm gate length) with experimental (Appenzeller et al, 2002) and simulation data                                                                                                               |

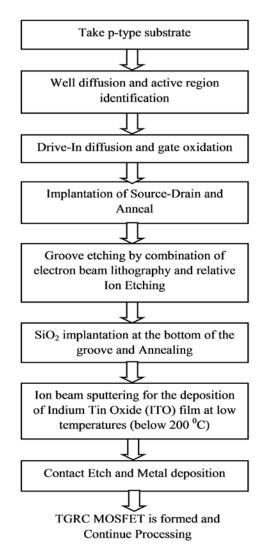

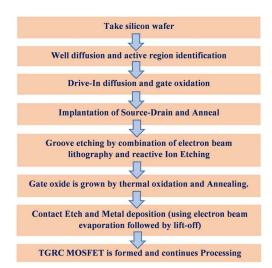

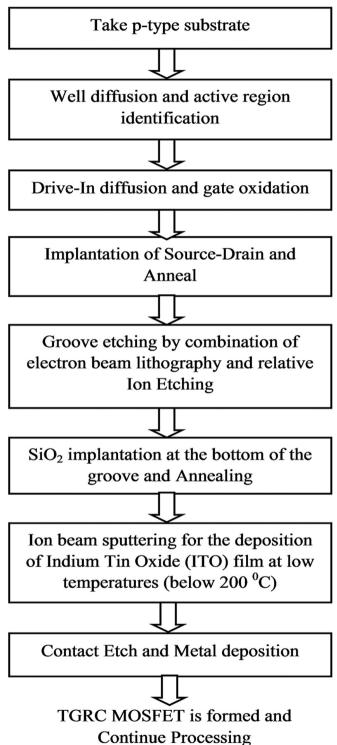

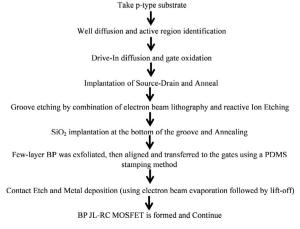

| Figure 2.3: Process flow of TGRC MOSFET                                                                                                                                                                                                                                      |

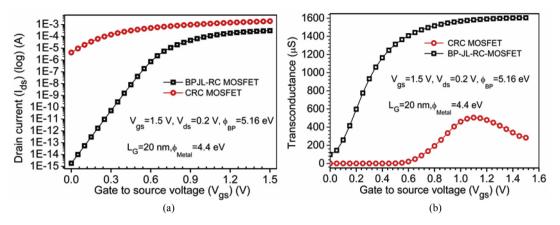

| Figure 2.4: (a) Drain current variations for TGRC-MOSFET, CRC-MOSFET, and Conventional MOSFET. (b) Drain current at different $L_{\rm G}$ . (c) Drain current variations at different NJDs as a function of applied $V_{\rm gs}$                                             |

| Figure 2.5: (a) Variations of $g_m$ for TGRC-MOSFET, CRC-MOSFET, and Conventional MOSFET, (b) Variation of $g_m$ at different $L_G$ , (c) Variation of $g_m$ at various NJDs as a function of applied $V_{gs}$ 39                                                            |

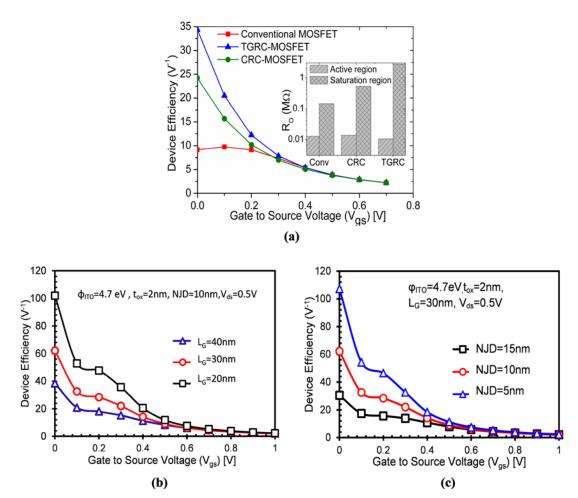

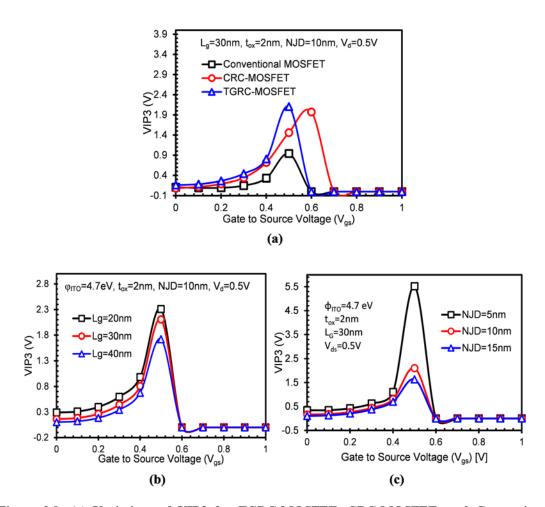

| Figure 2.6: (a) Variations of Device Efficiency for TGRC-MOSFET, CRC-MOSFET, and Conventional MOSFET. Inset: Output resistance. (b) Variation of Device Efficiency at different $L_G$ , (c) Variation of Device Efficiency at various NJDs as a function of applied $V_{gs}$ |

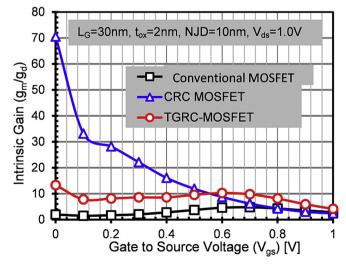

| Figure 2.7: Variations of Intrinsic Gain as a function of applied $V_{gs}$ for TGRC-MOSFET, CRC-MOSFET, and Conventional MOSFET. 41                                                                                                                                          |

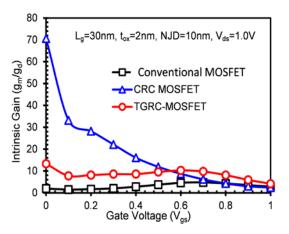

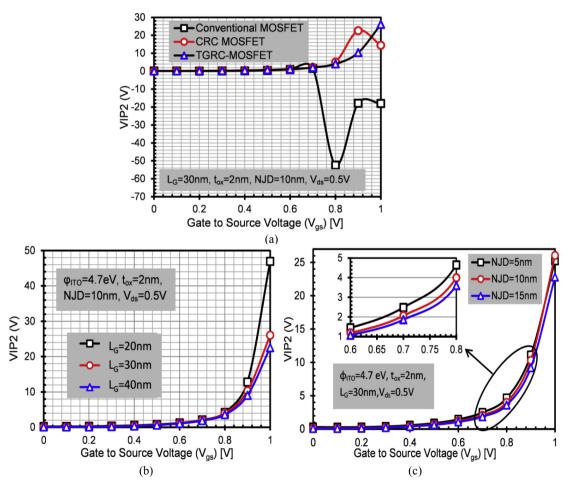

| Figure 2.8: (a) Variations of VIP2 for TGRC-MOSFET, CRC-MOSFET, and Conventional MOSFET. (b) Variation of VIP2 at different $L_G$ . (c) Variation of VIP2 at different NJDs as a function of applied $V_{-}$ .                                                               |

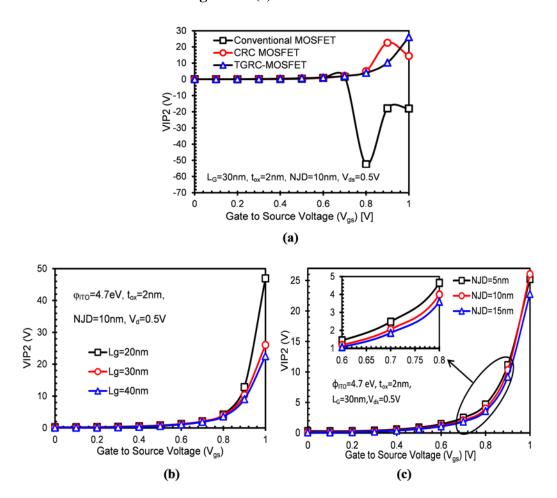

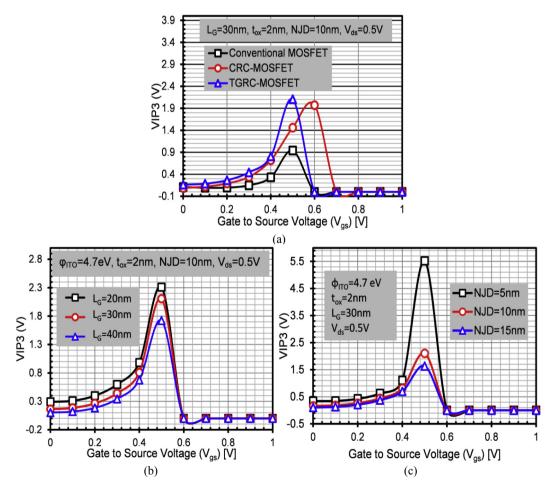

| Figure 2.9: (a) Variations of VIP3 for TGRC-MOSFET, CRC-MOSFET, and Conventional MOSFET                                                                                  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| (b) Variation of VIP3 at different $L_G$ . (c) Variation of VIP3 at various NJDs as a function of applied                                                                |

| $V_{gs}$ 44                                                                                                                                                              |

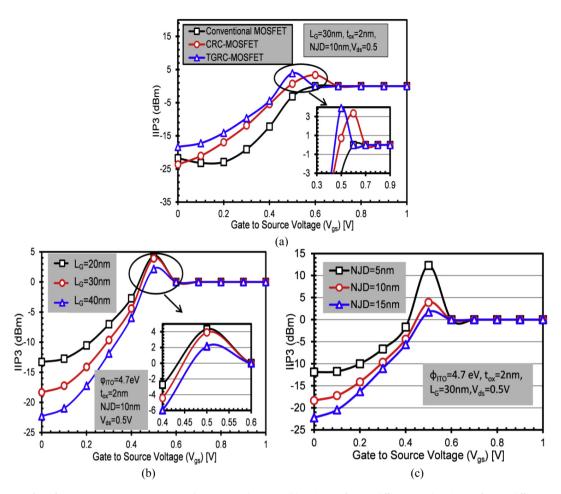

| Figure 2.10: (a) Variations of IIP3 for TGRC-MOSFET, CRC-MOSFET, and Conventional MOSFET                                                                                 |

| (b) Variation of IIP3 at different $L_G$ . (c) Variation of IIP3 at different NJDs as a function of applied $V_g$                                                        |

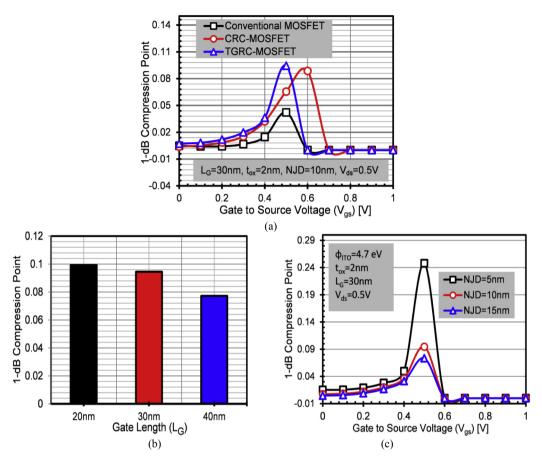

| Figure 2.11: (a) Variations of 1-dB Compression point for TGRC-MOSFET, CRC-MOSFET, and                                                                                   |

| Conventional MOSFET. (b) Variation of 1-dB Compression point at different $L_{G}$ . (c) Variation of 1-dB                                                                |

| Compression at different NJDs as a function of applied $V_{\text{gs}}$ .                                                                                                 |

| Figure 2.12: (a) Variations of $g_{m3}$ for TGRC-MOSFET, CRC-MOSFET, and Conventional MOSFET                                                                             |

| (b) Variation of $g_{m3}$ at different $L_G$ . (c) Variation of $g_{m3}$ at various NJDs as a function of applied $V_{gs}$ . 48                                          |

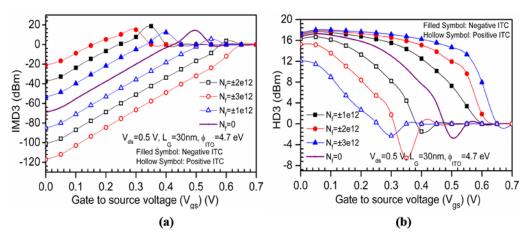

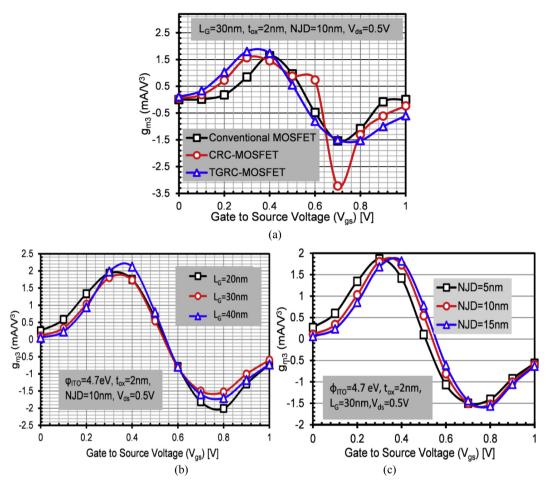

| Figure 2.13: (a) Variations of IMD3 for TGRC-MOSFET, CRC-MOSFET and Conventional                                                                                         |

| MOSFET. (b) Variation of HD3 for TGRC-MOSFET, CRC-MOSFET, and Conventional MOSFET                                                                                        |

| (c) Variations of IMD3 and HD3 at different $L_G$ . (d) Variation of IMD3 and HD3 at various NJDs as                                                                     |

| function of applied $V_{\text{gs}}$                                                                                                                                      |

| Figure 3.1: Device design of TGRC-MOSFET (3D device) with interface traps charges5                                                                                       |

| Figure 3.2: Calibrated transfer characteristics of recessed channel MOSFET (36 nm gate length) with                                                                      |

| experimental (Appenzeller et al, 2002) and simulation data                                                                                                               |

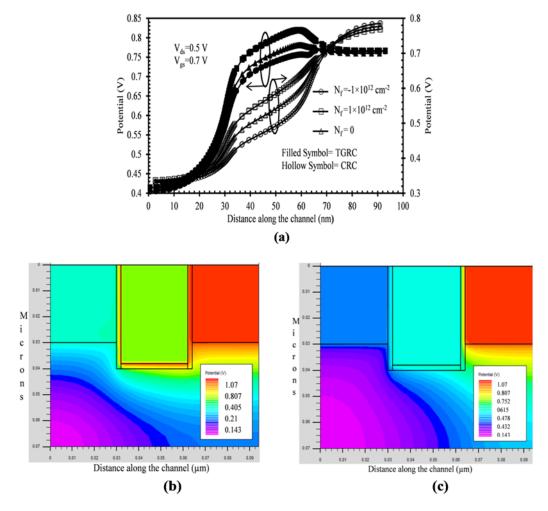

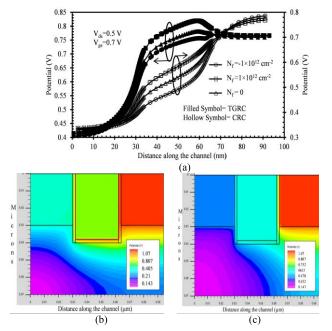

| Figure 3.3: (a) Potential, with respect to the distance along the channel for CRC and TGRC MOSFETs                                                                       |

| (b) Contour plot CRC-MOSFET with impact of positive interface trap charge (c) Contour plot TGRC                                                                          |

| MOSFET with impact of positive interface trap charge.                                                                                                                    |

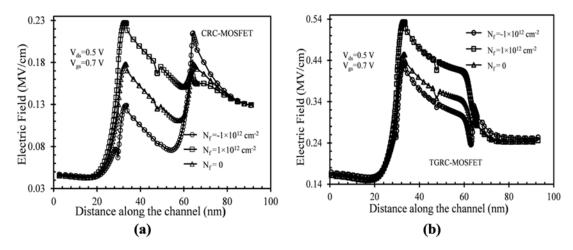

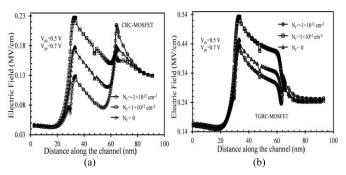

| Figure 3.4: (a) Electric field distribution along the channel for CRC-MOSFET and (b) for TGRC                                                                            |

| MOSFET60                                                                                                                                                                 |

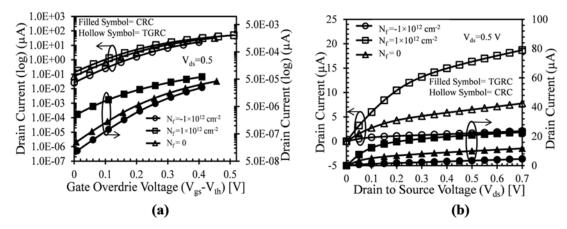

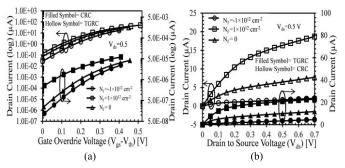

| Figure 3.5: (a) Transfer characteristics w.r.t. $V_{gs}$ , (b) Output characteristics w.r.t. $V_{ds}$ ; for CRC                                                          |

| MOSFET and TGRC-MOSFET                                                                                                                                                   |

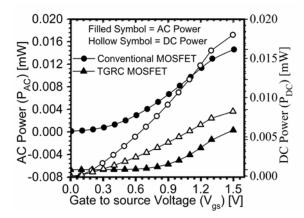

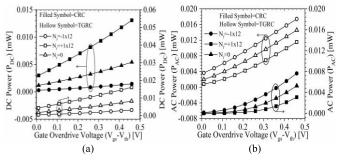

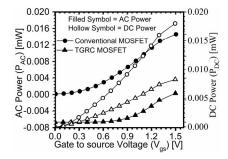

| Figure 3.6: (a) DC power ( $P_{DC}$ ) and (b) AC power ( $P_{AC}$ ) w.r.t. $V_{gs}$ ; for CRC-MOSFET and TGRC                                                            |

| MOSFET                                                                                                                                                                   |

|                                                                                                                                                                          |

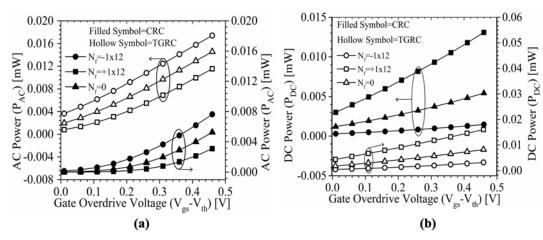

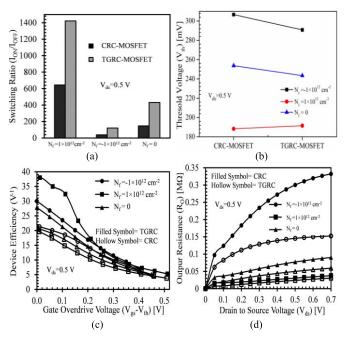

| Figure 3.7: Effect of interface trap charges on (a) switching ratio (b) threshold voltage (c) devic efficiency and (d) output resistance, for CRC-MOSFET and TGRC-MOSFET |

|                                                                                                                                                                          |

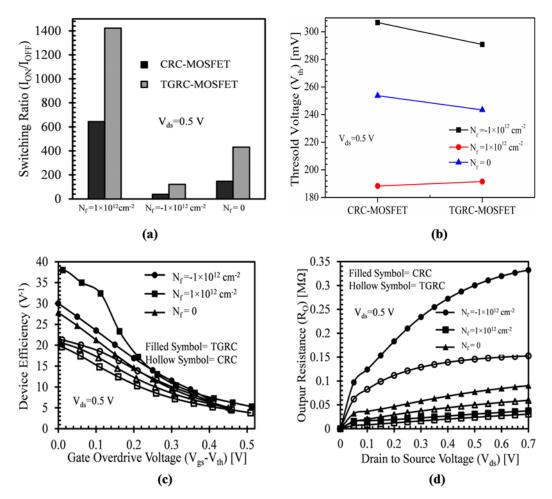

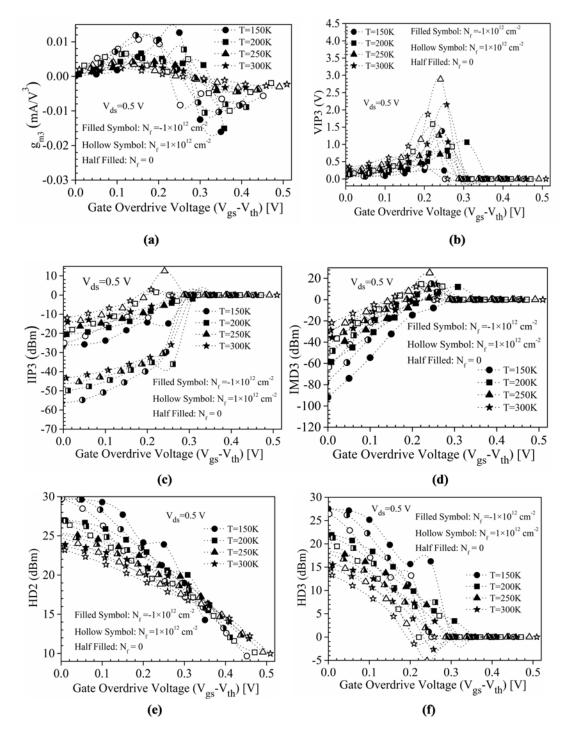

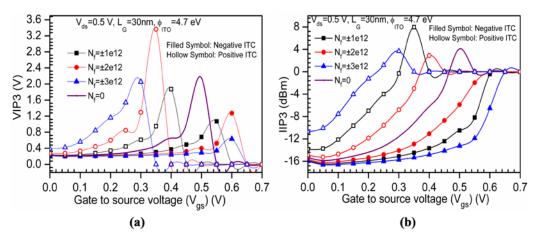

| Figure 3.8: Effect of interface trap charges on (a) $g_{m3}$ , (b) VIP3, (c) IIP3, (d) IMD3, (e) HD2 and (f                                                              |

| HD3 for CRC-MOSFET and TGRC-MOSFET60                                                                                                                                     |

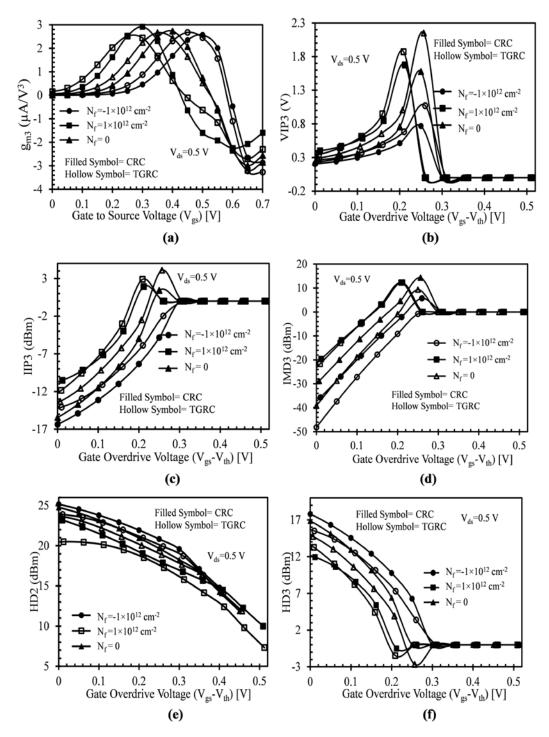

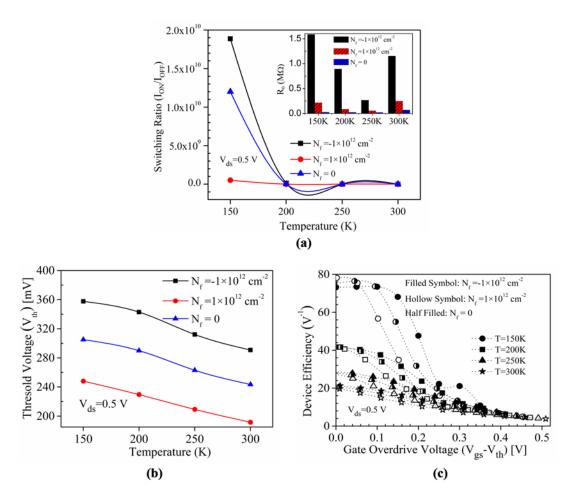

| Figure 3.9: Effect of temperature on (a): switching ratio, Inset: output resistance, (b): threshold voltage                                                              |

| and (c): device efficiency, in TGRC-MOSFET with interface trap charge density69                                                                                          |

| Figure 3.10: Effect of temperature with interface trap charges on (a): $g_{m3}$ , (b): VIP3, (c): IIP3, (d): IMD3, (e): HD2 and (f): HD3 in TGRC-MOSFET70                                                             |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

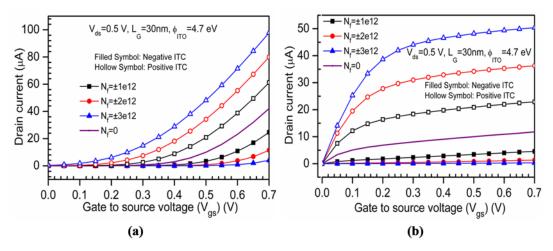

| Figure 3.11: (a) Transfer characteristics w.r.t. source voltage $(V_{gs})$ , (b) Output characteristics w.r.t. source voltage $(V_{ds})$ for TGRC-MOSFET                                                              |

| Figure 3.12: Impact of interface trap charges for TGRC-MOSFET on (a) transconductance $(g_{m1})$ and (b) $g_{m3}$                                                                                                     |

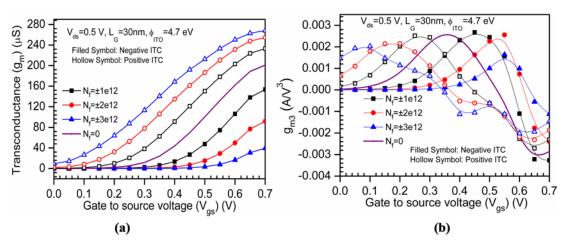

| Figure 3.13: Impact of interface trap charges for TGRC-MOSFET on (a) VIP3 and (b) IIP373                                                                                                                              |

| Figure 3.14: Impact of interface trap charges for TGRC-MOSFET on (a) IMD3, and (b) HD373                                                                                                                              |

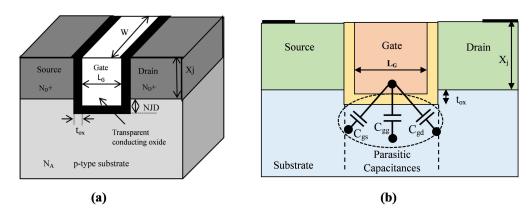

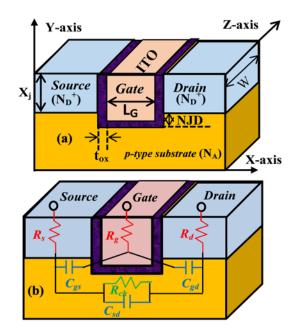

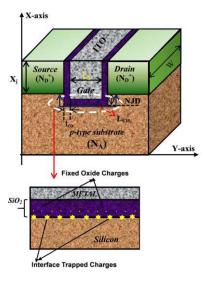

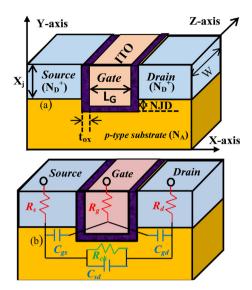

| Figure 4.1: The schematic simulated structure of TGRC-MOSFET. (b). Cross view of TGRC-MOSFET with parasitic capacitances                                                                                              |

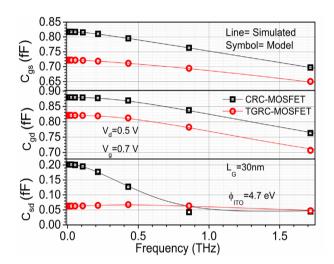

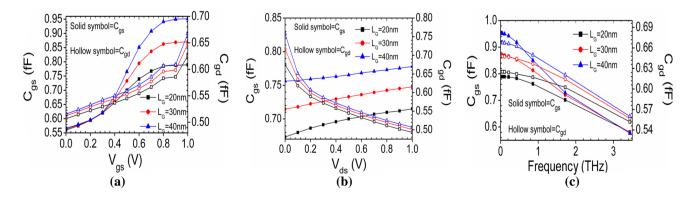

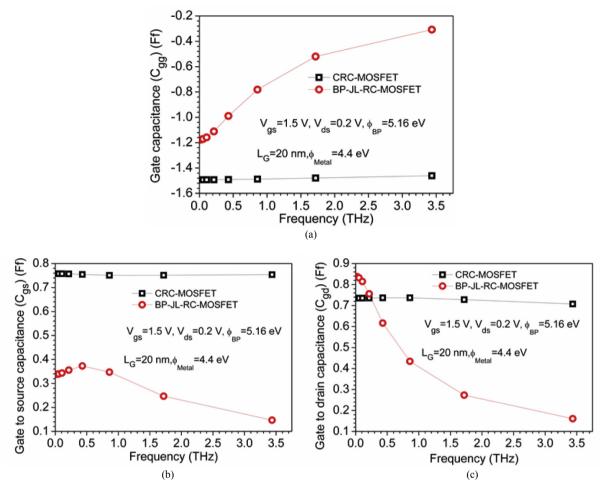

| Figure 4.2: $C_{gs}$ and $C_{gd}$ as a function of (a) $V_{gs}$ =1.0V at $V_{ds}$ =0.5V (b) $V_{ds}$ =1.0V at $V_{gs}$ =0.5V (c) frequency at $V_{gs}$ =1.0V, $V_{ds}$ =0.5V; of CRC and TGRC MOSFETs                 |

| Figure 4.3: Gate Capacitance as a function of (a) $V_{gs}$ =1.0V ( $V_{ds}$ =0.5V) and $V_{ds}$ =1.0V ( $V_{gs}$ =0.5V) (b) frequency at $V_{gs}$ =1.0V, $V_{ds}$ =0.5V; of CRC and TGRC MOSFETs                      |

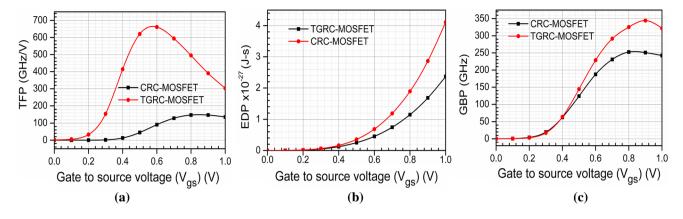

| Figure 4.4: (a) TFP, (b) EDP, (c) GBP; at $V_{gs}$ =1.0V, $V_{ds}$ =0.5V as a function of gate to source voltage for CRC and TGRC MOSFETs85                                                                           |

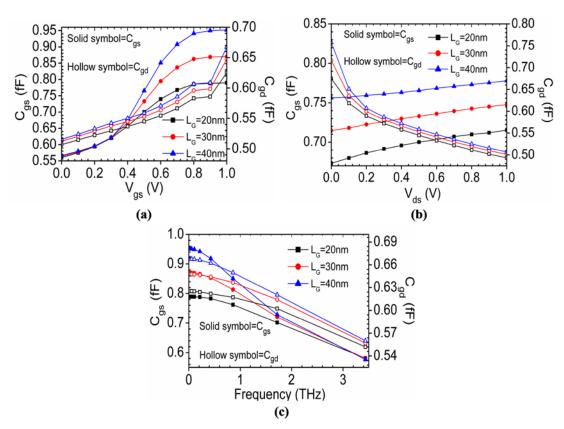

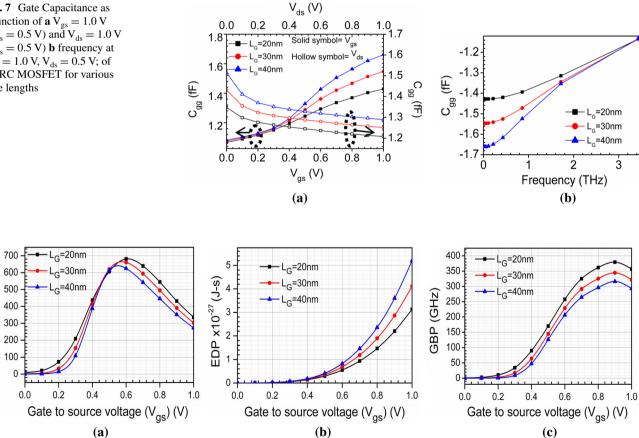

| Figure 4.5: $C_{gs}$ and $C_{gd}$ as a function of (a) $V_{gs}$ =1.0V at $V_{ds}$ =0.5V (b) $V_{ds}$ =1.0V at $V_{gs}$ =0.5V (c) frequency at $V_{gs}$ =1.0V, $V_{ds}$ =0.5V; of TGRC-MOSFET for various gate lengths |

| Figure 4.6: Gate Capacitance as a function of (a) $V_{gs}$ =1.0V ( $V_{ds}$ =0.5V) and $V_{ds}$ =1.0V ( $V_{gs}$ =0.5V) (b) frequency at $V_{gs}$ =1.0V, $V_{ds}$ =0.5V; of TGRC-MOSFET for various gate lengths      |

| Figure 4.7: (a) TFP, (b) EDP, (c) GBP; as a function of $V_{gs}$ =1.0V ( $V_{ds}$ =0.5V) of TGRC-MOSFET for various gate lengths.                                                                                     |

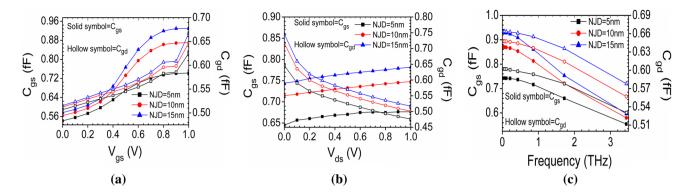

| Figure 4.8: $C_{gs}$ and $C_{gd}$ as a function of (a) $V_{gs}$ =1.0V at $V_{ds}$ =0.5V (b) $V_{ds}$ =1.0V at $V_{gs}$ =0.5V (c) frequency at $V_{gs}$ =1.0V, $V_{ds}$ =0.5V; of TGRC-MOSFET at various NJDs90        |

| Figure 4.9: Gate Capacitance as a function of (a) $V_{gs}$ =1.0V ( $V_{ds}$ =0.5V) and $V_{ds}$ =1.0V ( $V_{gs}$ =0.5V) (b) frequency at $V_{gs}$ =1.0V, $V_{ds}$ =0.5V; of TGRC-MOSFET for various NJDs90            |

| Figure 4.10: (a) Transconductance Frequency Product (TFP), (b) Energy Delay Product (EDP) , (c) Gain Bandwidth Product (GBP); as a function of $V_{gs}$ =1.0V ( $V_{ds}$ =0.5V) of TGRC-MOSFET for various NJDs       |

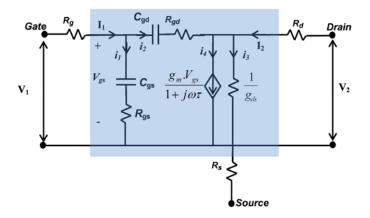

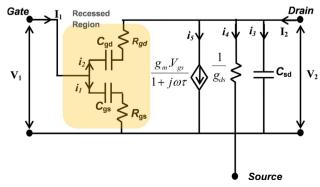

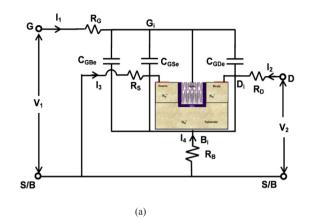

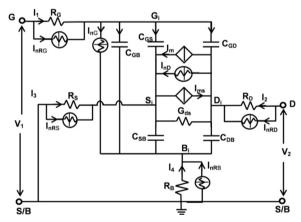

| Figure 5.1: (a) Schematic structure and (b) conceptual depiction of the small signal equivalent of TGRC-MOSFET                                                                                                        |

| Figure 5.2: Non-quasi-static (NQS) model of the RF MOSFET (RC-MOSFET)                                                                                                                                                 |

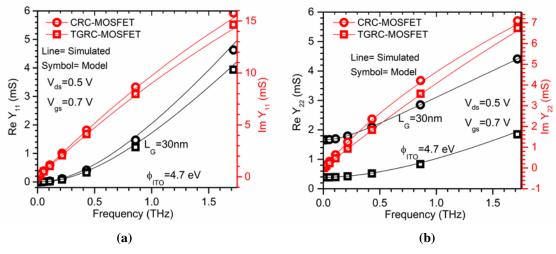

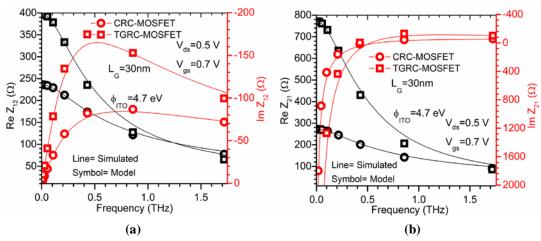

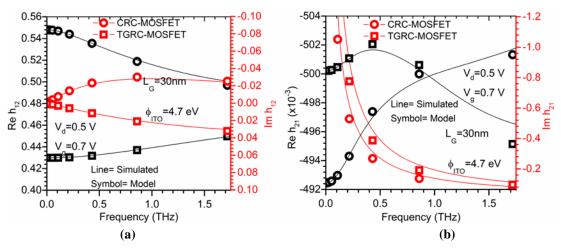

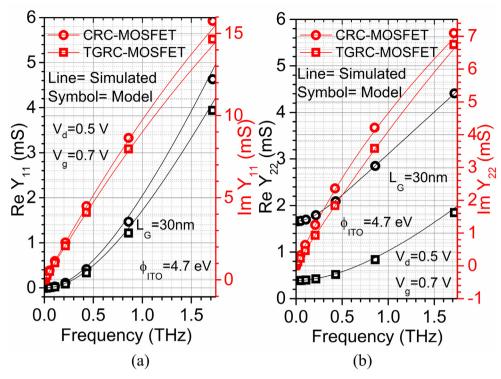

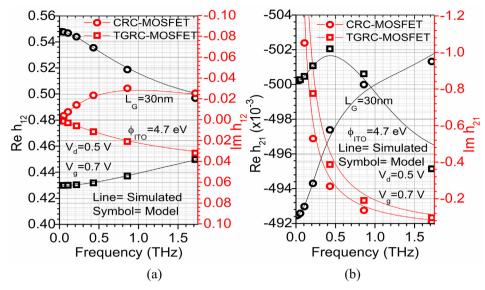

| Figure 5.3: (a) Y-parameters ( $Y_{11}$ ) and (b) Y-parameters ( $Y_{22}$ ), w.r.t. frequency at $V_{gs}$ =0.7 V and $V_{ds}$ =0.5 V for CRC and TGRC-MOSFET                                                                                                                                                                                                                                                                                                                           |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

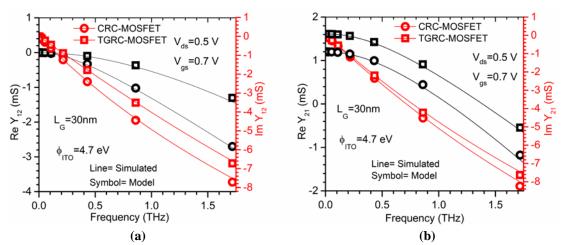

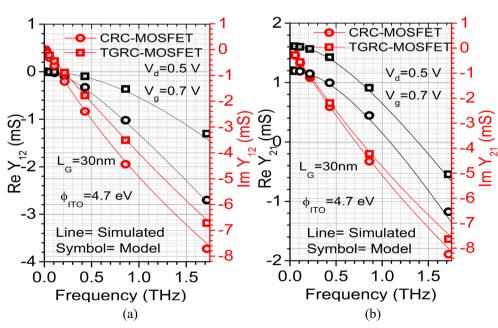

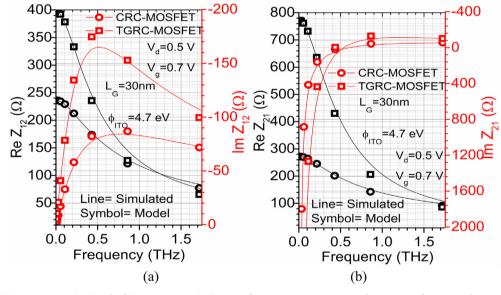

| Figure 5.4: (a) Y-parameters ( $Y_{12}$ ) and (b) Y-parameters ( $Y_{21}$ ), w.r.t. frequency at $V_{gs}$ =0.7 V and $V_{ds}$ =0.5 V for CRC-MOSFET and TGRC-MOSFET                                                                                                                                                                                                                                                                                                                    |

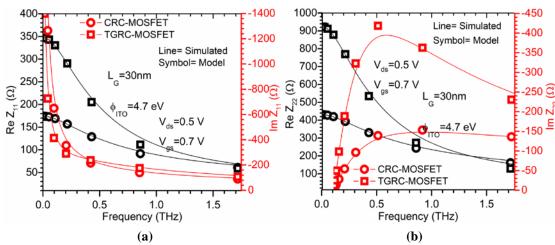

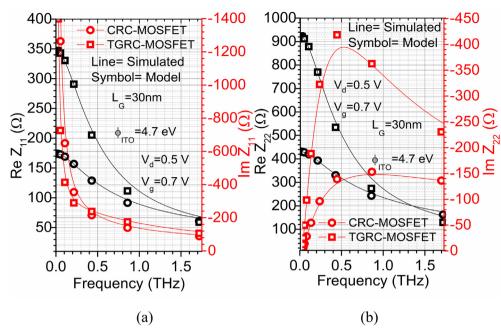

| Figure 5.5: (a) Z-parameters ( $Z_{11}$ ) and (b) Z-parameters ( $Z_{22}$ ), w.r.t. frequency at $V_{gs}$ =0.7 V and $V_{ds}$ =0.5 V for CRC and TGRC MOSFETs                                                                                                                                                                                                                                                                                                                          |

| Figure 5.6: (a) Z-parameters ( $Z_{12}$ ) and 7(b) Z-parameters ( $Z_{21}$ ), w.r.t. frequency at $V_{gs}$ =0.7 V and $V_{ds}$ =0.5 V for CRC and TGRC MOSFETs                                                                                                                                                                                                                                                                                                                         |

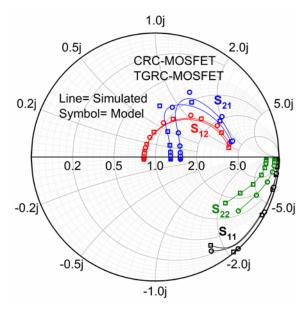

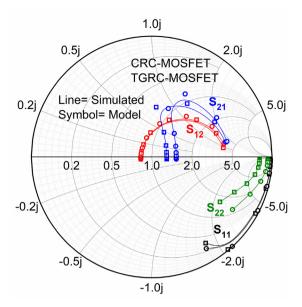

| Figure 5.7: Modeled and simulated S-parameters up to 1.7 THz frequency using extracted model parameters and small signal model for CRC and TGRC MOSFETs at $V_{gs}$ =0.7 V and $V_{ds}$ =0.5 V108                                                                                                                                                                                                                                                                                      |

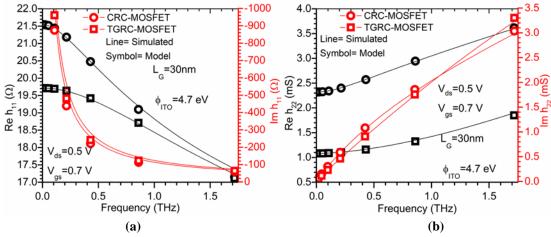

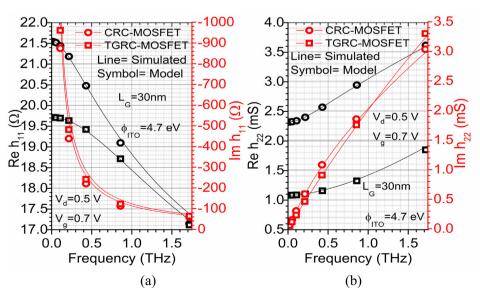

| Figure 5.8: (a) h-parameter ( $h_{11}$ ) and (b) h-parameter ( $h_{22}$ ), w.r.t. frequency at $V_{gs}$ =0.7 V and $V_{ds}$ =0.5 V for CRC and TGRC MOSFETs.                                                                                                                                                                                                                                                                                                                           |

| Figure 5.9: (a) h-parameter ( $h_{12}$ ) and (b) h-parameter ( $h_{21}$ ), w.r.t. frequency at $V_{gs}$ =0.7 V and $V_{ds}$ =0.5 V for CRC and TGRC MOSFETs.                                                                                                                                                                                                                                                                                                                           |

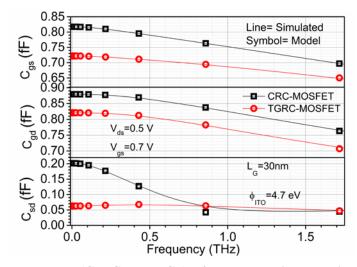

| Figure 5.10: RF component ( $C_{gs}$ , $C_{gd}$ and $C_{sd}$ ) of the small signal equivalent circuit w.r.t. frequency at $V_{gs}$ =0.7 V and $V_{ds}$ =0.5 V for CRC and TGRC MOSFETs112                                                                                                                                                                                                                                                                                              |

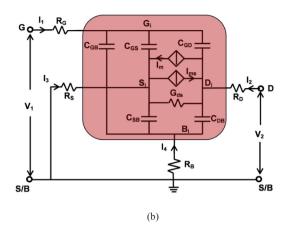

| Figure 5.11: (a) Transit frequency. (b) Maximum oscillator frequency at $V_{gs}$ =0.7 V and $V_{ds}$ =0.5 V for CRC-MOSFET and TGRC-MOSFET                                                                                                                                                                                                                                                                                                                                             |

| Figure 6.1: Simulated device structure of TGRC-MOSFET                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Figure 6.2: AC power $(P_{AC})$ and DC power $(P_{DC})$ w.r.t. $V_{gs}$ ; for TGRC MOSFET and conventional MOSFET.                                                                                                                                                                                                                                                                                                                                                                     |

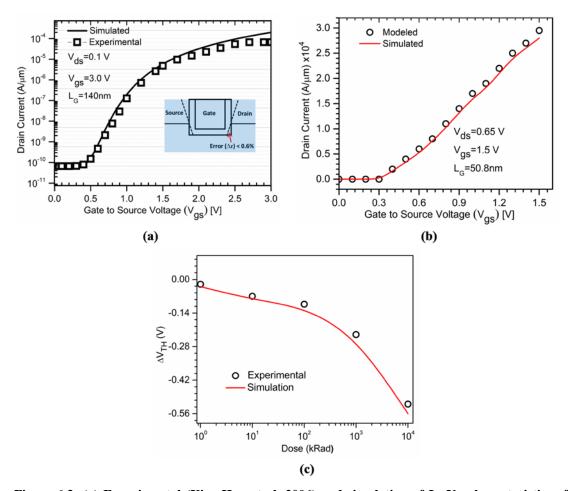

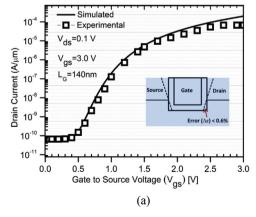

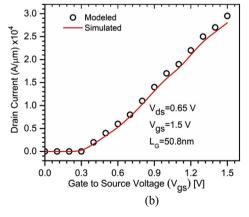

| Figure 6.3: (a) Experimental (Xiao-Hua et al, 2006) and simulation of $I_{ds}$ - $V_{gs}$ characteristics of 140 nm gate length grooved gate (recessed channel) MOSFET. (b) Modelled (Sreelal et al, 2002) and simulation of $I_{ds}$ - $V_{gs}$ characteristics of 50.8 nm gate length recessed channel MOSFET. (c) Calibration of experimental (Berland et al, 1991) and simulation results with shift in threshold voltage ( $\Delta V_{TH}$ ) under irradiation up to $10^4$ kRad. |

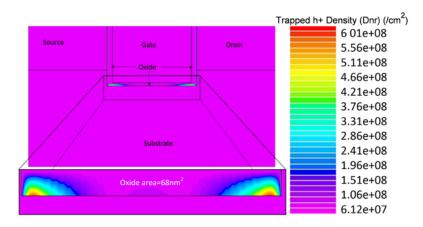

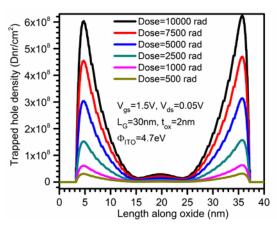

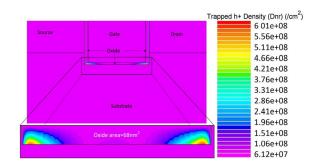

| Figure 6.4: Trapped hole density profile along the oxide substrate interface, having oxide thickness 2nm, and oxide area 68 nm <sup>2</sup>                                                                                                                                                                                                                                                                                                                                            |

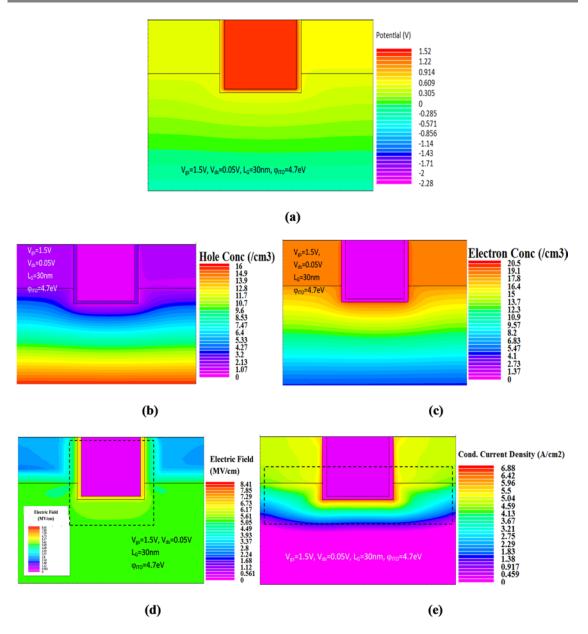

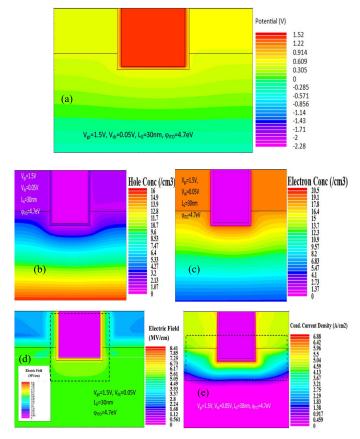

| Figure 6.5: Contour plots of (a) Surface potential; (b) Hole concentration; (c) Electron concentration; (d) Electric field and (e) Conduction current density on TGRC-MOSFET ( $t_{ox}$ =2nm) with 1000 RadX-ray dose                                                                                                                                                                                                                                                                  |

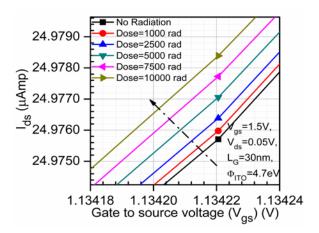

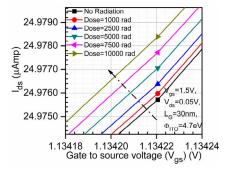

| Figure 6.6: The impact of X-ray radiation damage on the current-voltage characteristics of TGRC MOSFET at $t_{ox}$ =2nm                                                                                                                                                                                                                                                                                                                                                                |

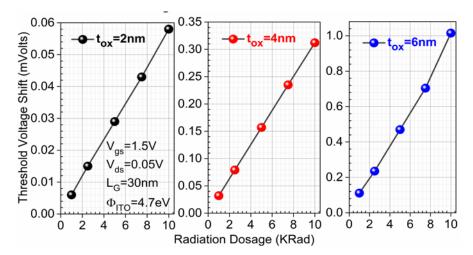

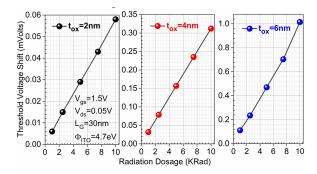

| Figure 6.7: Threshold Voltage Shift due to radiation on (a): TGRC MOSFET and, (b): Conventional MOSFET                                                                                                                                                                                           |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

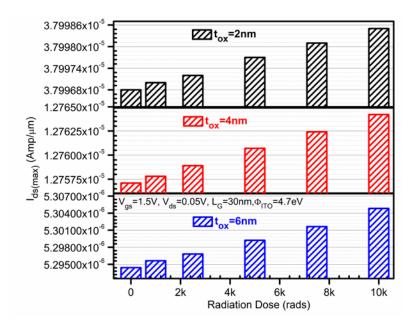

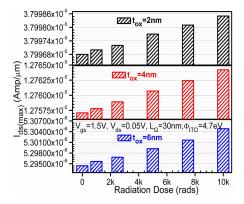

| Figure 6.8: The impact of radiation dose on the maximum drain to source current for (a): TGRC MOSFET and, (b): Conventional MOSFET                                                                                                                                                               |

| Figure 6.9: Trapped hole density profile along the oxide substrate interface                                                                                                                                                                                                                     |

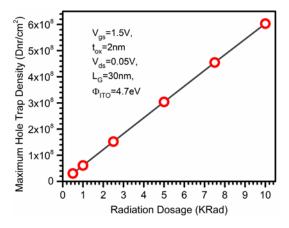

| Figure 6.10: The impact of varying radiation dosage on maximum hole trap density                                                                                                                                                                                                                 |

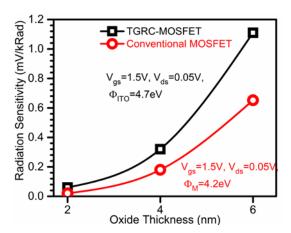

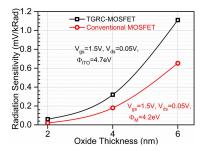

| Figure 6.11: Dependency of Radiation Sensitivity on Oxide Thickness in TGRC MOSFET and, Conventional MOSFET                                                                                                                                                                                      |

| Figure 6.12: Variation of ON current with radiation dosage for different oxide thickness                                                                                                                                                                                                         |

| Figure 6.13: Threshold voltage shift with variation in radiation dosage for various oxide thicknesses.                                                                                                                                                                                           |

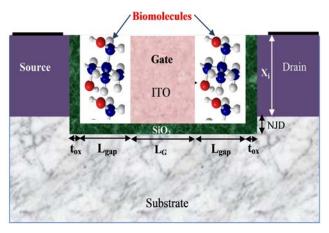

| Figure 6.14: Schematic structure of TGRC-MOSFET as a biosensor                                                                                                                                                                                                                                   |

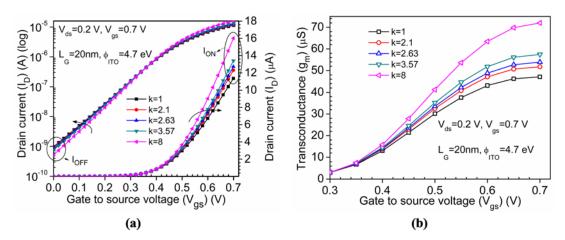

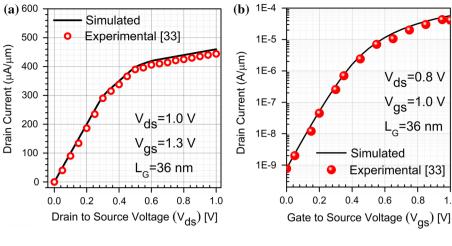

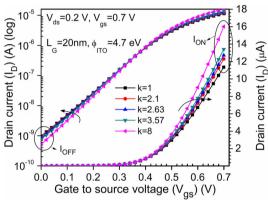

| Figure 6.15: (a) Transfer characteristics and (b) Transconductance (g <sub>m</sub> ); of Nano-gap embedded TGRC-MOSFET in the presence of biomolecules                                                                                                                                           |

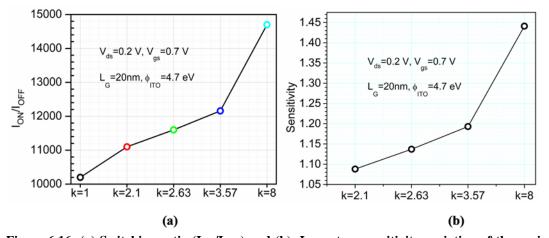

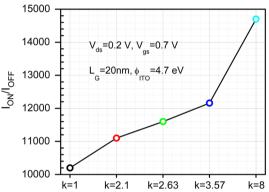

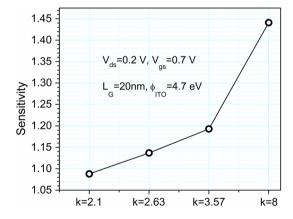

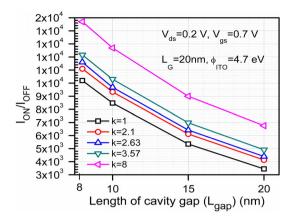

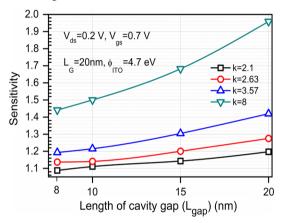

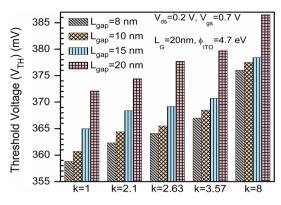

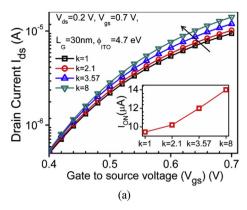

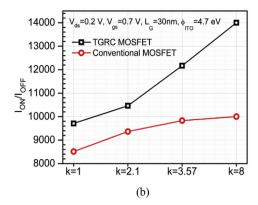

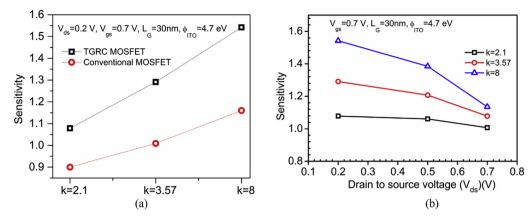

| Figure 6.16: (a) Switching ratio ( $I_{ON}/I_{OFF}$ ) and (b) Impact on sensitivity variation of the various biomolecules at 0.2V drain voltages for TGRC-MOSFET                                                                                                                                 |

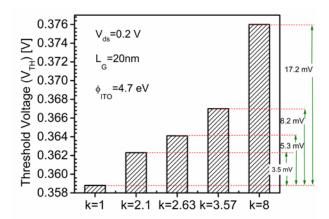

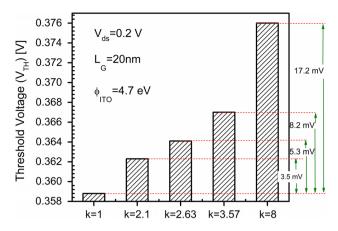

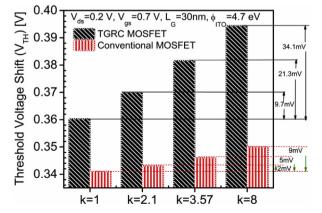

| Figure 6.17: Threshold voltage shifts for different biomolecules in TGRC-MOSFET                                                                                                                                                                                                                  |

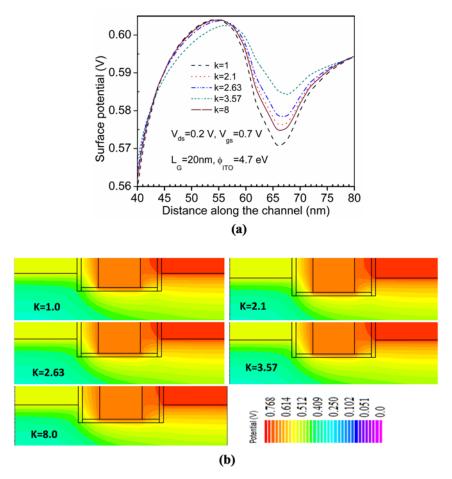

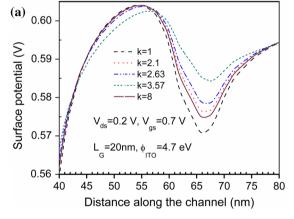

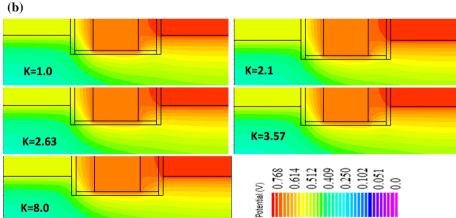

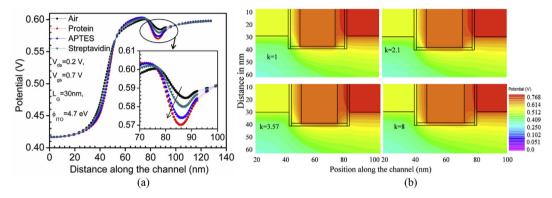

| Figure 6.18: (a) Effect on surface potential in the presence of biomolecules along the channel from source to drain in TGRC-MOSFET. (b) Contour plot of surface potential in the presence of biomolecules (for k=1, 2.1, 2.63, 3.57 and 8) along the channel from source to drain in TGRC-MOSFET |

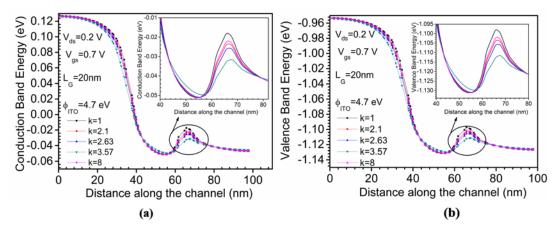

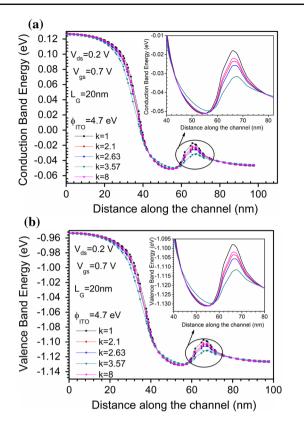

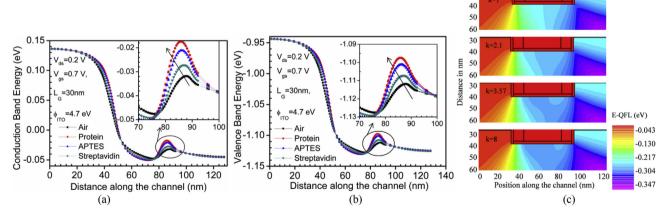

| Figure 6.19: Effect on energy bands: (a) Conduction band and (b) Valence band along the channel in the presence of biomolecules in TGRC-MOSFET                                                                                                                                                   |

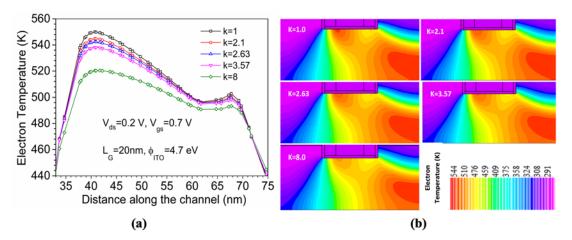

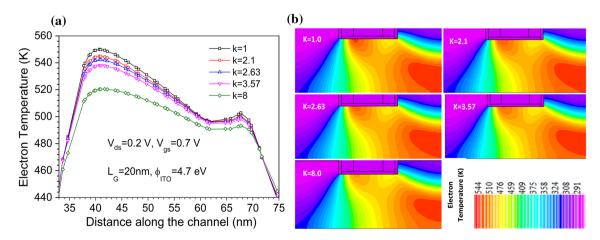

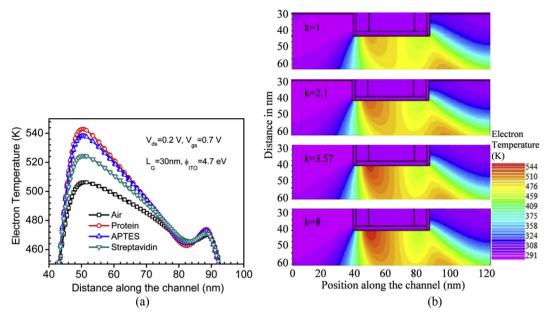

| Figure 6.20: (a) Effect on electron temperature along the channel from source to drain and (b) contour plot of electron temperature, in the presence of biomolecules in TGRC-MOSFET142                                                                                                           |

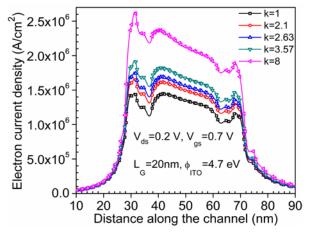

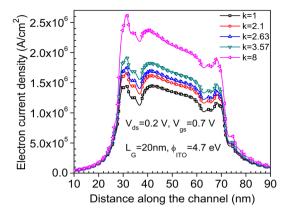

| Figure 6.21: Electron current density along the channel from source to drain in the presence of biomolecules in TGRC-MOSFET                                                                                                                                                                      |

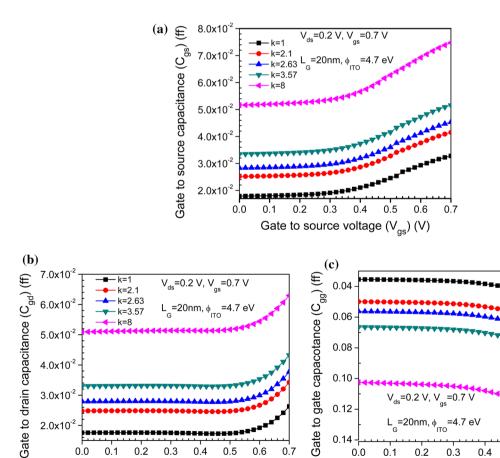

| Figure 6.22: (a) Effect on parasitic capacitances (a) $C_{gs}$ (b) $C_{gd}$ (c) $C_{gg}$ ; in the presence of biomolecules in TGRC-MOSFET                                                                                                                                                        |

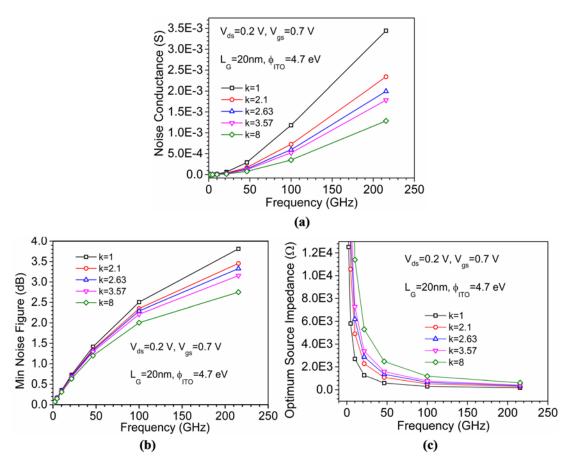

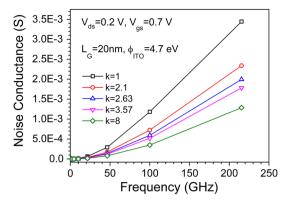

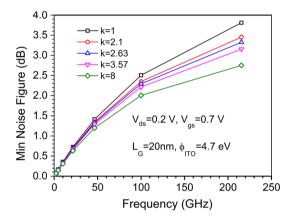

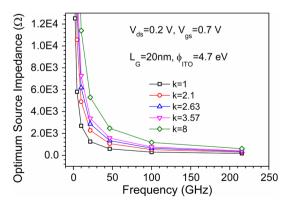

| Figure 6.23: (a) Noise conductance, (b) Minimum noise figure, and (c) Optimum source impedance; in the presence of biomolecules in TGRC-MOSFET at GHz frequency range                                                                                                                            |

Figure 6.24: (a) The impact of length of cavity gap variation on switching ratio, (b) The impact of length of cavity gap variation on Sensitivity, and (c) The impact of length of cavity gap variation on Threshold voltage; for different biomolecules in TGRC-MOSFET.......146

# LIST OF TABLES

| Table 1.1: TCO for thin film transparent electrodes                                 | 17  |

|-------------------------------------------------------------------------------------|-----|

| Table 1.2: Electrical properties if ITO with a resistivity of $10^{-5} \Omega$ -cm. | 19  |

| Table 1.3: Comparison of ITO and ZnO                                                | 19  |

| Table 3.1: P <sub>AC</sub> Variation with L <sub>G</sub>                            | 62  |

| Table 4.1: Default simulated structure parameters of TGRC and CRC MOSFETs           | 82  |

| Table 6.1: Design Parameters of TGRC MOSFET.                                        | 126 |

#### **In International Refereed Journals (9)**

- **1. A. Kumar,** M. M. Tripathi, and R. Chaujar "Reliability of Indium-Tin-Oxide with Interface Trap Charges on TGRC-MOSFET at Low Temperature" **IEEE Transactions on Electron Devices**, Vol.65, Issue 3, pp 860-866. (**IF: 2.605**).

- **2. A. Kumar,** B. Tiwari, S. Singh, M. M. Tripathi, and R. Chaujar "Radiation Analysis of TGRC-MOSFET: An X-Ray Dosimeter for Clinical Applications" **IEEE Transactions on Electron Devices.** Vol.65, pp 5014-5020, 2018. (**IF: 2.605**)

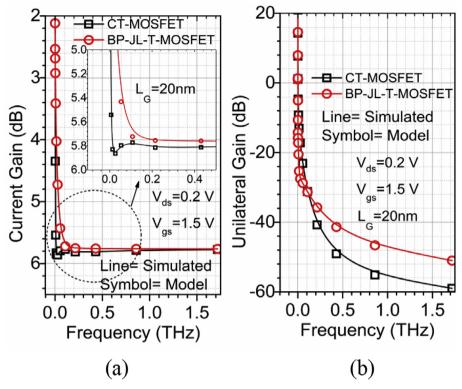

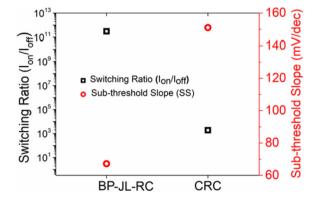

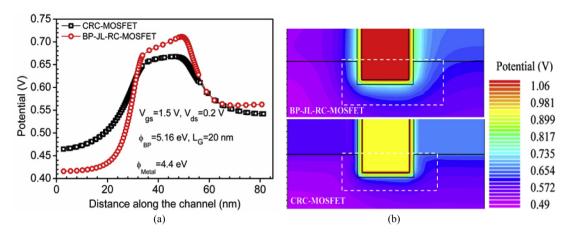

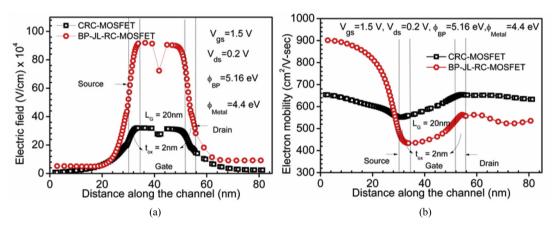

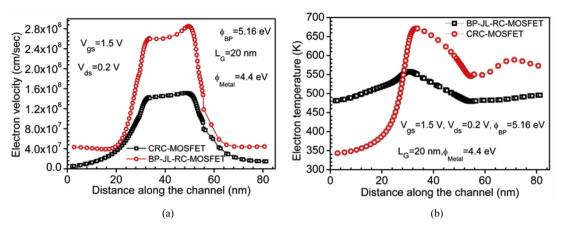

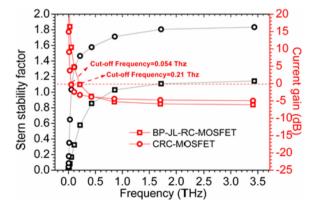

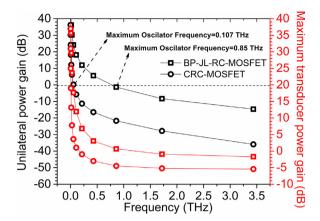

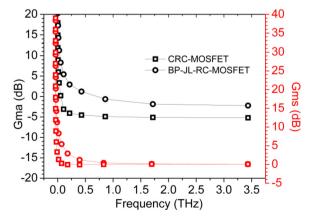

- **3. A. Kumar,** M. M. Tripathi, and R. Chaujar "Comprehensive Analysis of Sub-20nm Black Phosphorus Based Junctionless-Recessed Channel MOSFET for Analog/RF Applications" **Superlattices and Microstructures, Elsevier** Vol. 116, April 2018, Pages 171-180. (**IF: 2.123**)

- 4. A. Kumar, M. M. Tripathi, and R. Chaujar "Investigation of Parasitic Capacitances of In<sub>2</sub>O<sub>5</sub>Sn Gate Electrode Recessed Channel MOSFET for ULSI Switching Applications" Microsystem Technologies, Springer Vol 23, Issue 12, pp 5867–5874, 2017. (IF: 1.581)

- **5. A. Kumar,** M. M. Tripathi, and R. Chaujar "Low Power, Highly Sensitive Nano-gap Embedded Sub-20nm TGRC-MOSFET for the Detection of Neutral Biomolecules" **Journal of computational electronics, Springer.** Vol 1, pp 1807-1815. (**IF: 1.526**)

- 6. A. Kumar, M. M. Tripathi, and R. Chaujar "In<sub>2</sub>O<sub>5</sub>Sn Based Transparent Gate Recessed Channel MOSFET: RF Small-Signal Model for Microwave Applications" AEU International Journal of Electronocs and Communication, Elsevier, Vol 93, <u>Issue 9</u>, pp 233–241. (IF: 2.115).

- **7. A. Kumar** "Effect of Trench Depth and Gate Length Shrinking Assessment on the Analog and Linearity Performance of TGRC-MOSFET" **Superlattices and Microstructures, Elsevier** Volume 109, September 2017, Pages 626-640. (**IF: 2.123**).

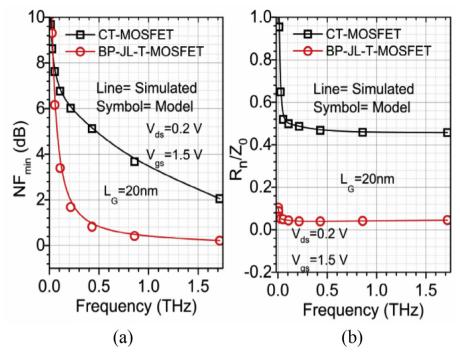

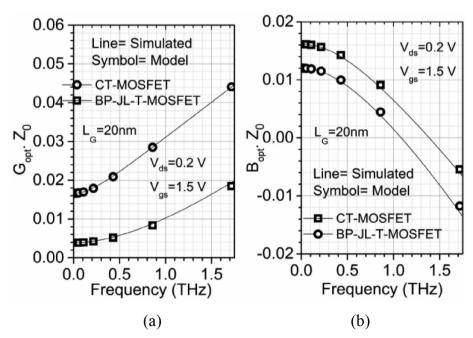

- **8. A. Kumar,** M. M. Tripathi, and R. Chaujar, "RF Noise Modeling of Black Phosphorus Junctionless Trench MOSFET in Strong Inversion Region", **Superlattices and Microstructures**, **Elsevier**. Vol. 125, pp. 72-79, 2019. (**IF: 2.123**).

- **9. A. Kumar,** M. M. Tripathi and R. Chaujar "High Sensitivity Assessment of TGRC MOSFET as a Protein Biomarker for Early Stage Diagnostics" **Vacuum, Elsevier**. Vol. 164, pp. 46-52, 2019. (**IF: 2.067**).

#### **In International Conferences (15)**

- **1. A. Kumar,** M. M. Tripathi, and R. Chaujar "Low Power, Highly Sensitive Nano-gap Embedded TGRC-MOSFET for the Detection of Neutral Biomolecules" 5<sup>th</sup> International Conference on Bio-Sensing Technology Riva Del Garda, Italy (Elsevier), P-115. 7-10 May 2017.

- **2. A. Kumar,** D. Kaur, M. M. Tripathi, and R. Chaujar "Influence of High-k Gate on Transparent Gate Recessed Channel (TGRC) MOSFET: A reliability Study" International Conference on Microelectronics Devices and Systems (ICMDCS), 10<sup>th</sup> to 12<sup>th</sup> August 2017, Vellore, India.

- **3. A. Kumar,** M. M. Tripathi, and R. Chaujar "Effect of Interface Trap charge density on the reliability issues of TGRC-MOSFET: A reliability Study" International Conference on Microelectronics Devices and Systems (ICMDCS), 10<sup>th</sup> to 12<sup>th</sup> August 2017, Vellore, India.

- **4. A. Kumar**, S. Singh, B. Tiwari and R. Chaujar, "Twin Gate Rectangular Recessed Channel (TG-RRC) MOSFET for Digital-Logic Applications". International Conference on Microelectronics Devices and Systems (ICMDCS), 10<sup>th</sup> to 12<sup>th</sup> August 2017, Vellore, India.

- **5. A. Kumar,** M. M. Tripathi, and R. Chaujar "Small-Signal Modeling of In<sub>2</sub>O<sub>5</sub>Sn Based Transparent Gate Recessed Channel MOSFET for Microwave/RF Applications" IEEE APMC 2017 Kuala Lampur, 16-17 Nov, pp. 976-979.

- **6. A. Kumar,** M. M. Tripathi, and R. Chaujar "Sub-20 nm Black Phosphorus Junctionless-Recessed Channel (BP JL-RC) MOSFET: A Low Power Device" 3<sup>rd</sup> Nanotechnology for Instrumentation and Measurement Workshop (NANOfIM), Gautam Buddha University Noida, India, November 16-17, 2017.

- **7. A. Kumar**, S. Singh, B. Tiwari and R. Chaujar, "Junctionless Double Gate Recessed Channel (JL-DGRC) MOSFET for Digital-Logic Applications". 3<sup>rd</sup> Nanotechnology for Instrumentation and Measurement Workshop (NANOfIM), Gautam Buddha University Noida, India, November 16-17, 2017.

- **8. A. Kumar,** M. M. Tripathi, and R. Chaujar, "Investigation of Novel Gate Materials on Recessed Channel (RC) MOSFET for High Performance Applications" pp. 402. ICN3I-2017, 6-8 Dec. IIT Roorkee.

- **9. A. Kumar,** M. M. Tripathi, and R. Chaujar, "Sub-20nm In<sub>2</sub>O<sub>5</sub>Sn Gate Electrode Recessed Channel MOSFET for Bio-sensing Applications" International Symposium on Functional Materials (ISFM), 13-15 April, 2018, Chandigarh, India.

- **10. A. Kumar,** M. M. Tripathi, and R. Chaujar, "High-Temperature Reliability of Black Phosphorus Recessed Channel (BPRC) MOSFET" 7<sup>th</sup> International Conference on Computing, Communication and Sensor Network (CCSN) 2018, 27-28 October, Kolkata India.

- **11. A. Kumar,** M. M. Tripathi, and R. Chaujar, "TCAD Analysis of Sub-20 nm Black Phosphorus Trench (BP-T) MOSFET for High Temperature Applications" 7<sup>th</sup> International Conference on Computing, Communication and Sensor Network (CCSN) 2018, 27-28 October, Kolkata India.

- **12. A. Kumar,** M. M. Tripathi, and R. Chaujar, "Linearity and Distortion Assessment of Black Phosphorus-Based Junctionless RC-MOSFET" 2018 3rd IEEE International Conference on Recent Trends in Electronics, Information & Communication Technology (RTEICT), Sri Venkateshwara College of Engineering, Bengaluru 18-19 May 2018.

- 13. A. Kumar, M. M. Tripathi, and R. Chaujar, "Investigation of Different Gate Materials onto Recessed Channel (RC) MOSFET for Improved Device Performance" 3rd IEEE International Conference on Recent Trends in Electronics, Information & Communication Technology (RTEICT), Sri Venkateshwara College of Engineering, Bengaluru 18-19 May 2018.

- **14. Ajay Kumar**, S. Singh, B. Tiwari, and R. Chaujar, "Temperature Reliability of Junctionless Twin Gate Recessed Channel (JL-TGRC) MOSFET with Different Gate Material for Low Power Digital-Logic Applications. IEEE Region 10 Conference (TENCON), Jeju Island, Korea, 28-31 October 2018.

- **15. A. Kumar,** M. M. Tripathi, and R. Chaujar, "Low-Temperature Reliability of Sub-20nm 4H-SiC Trench MOSFET with Black Phosphorus Gate Material", 5<sup>th</sup> International Conference on Signal Processing and Communication (ICSC), JIIT Noida, India, 7<sup>th</sup> to 9<sup>th</sup> March 2019.

## TABLE OF CONTENTS

| Certific | cate. |                                               | i    |

|----------|-------|-----------------------------------------------|------|

| Acknov   | vledg | yments                                        | iii  |

| Abstra   | ct    |                                               | v    |

| List of  | Figu  | res                                           | ix   |

| List of  | Tabl  | es                                            | xv   |

| List of  | Publ  | ications                                      | xvii |

| Table o  | of Co | ntents                                        | xxi  |

| Acrony   | ms    |                                               | xxv  |

| Снарт    | ER 1  | : Introduction                                | 1    |

| 1.1      | Ov    | verview of Nanoscale MOSFET                   | 2    |

| 1.2      | Sc    | aling of MOSFET                               | 4    |

| 1.3      | Sh    | ort Channel Effects (SCEs)                    | 5    |

| 1        | 3.1   | Threshold Voltage (V <sub>th</sub> ) Roll-off | 5    |

| 1        | 3.2   | Drain Induced Barrier Lowering (DIBL)         | 6    |

| 1.3      | 3.3   | Hot Carrier Effects (HCEs)                    | 6    |

| 1.4      | En    | gineering Schemes to Overcome SCEs            | 7    |

| 1.5      | De    | evice Concepts                                | 8    |

| 1.3      | 5.1   | Silicon on Insulator (SOI)                    | 8    |

| 1.3      | 5.2   | Dual Gate MOSFET                              | 9    |

| 1.3      | 5.3   | Fin FET                                       | 9    |

| 1.5      | 5.4   | Gate-All-Around (GAA) MOSFET                  | 10   |

| 1.6      | Re    | liability Issues of CMOS Devices              | 11   |

| 1.0      | 5.1   | Interface Trap Charges                        | 11   |

| 1.7      | Re    | search Gaps                                   | 13   |

| 1.8      | Po    | ssible Solutions                              | 14   |

| 1.8      | 8.1   | Recessed Channel MOSFET                       | 14   |

| A.       | Me    | erits of RC-MOSFET                            | 16   |

| В.       | De    | emerits of RC-MOSFET                          | 16   |

| 1.8      | 8.2   | Novel Gate Materials                          | 16   |

| A.                  | Transparent Conducting Oxides (TCOs)                                                 | 16      |  |

|---------------------|--------------------------------------------------------------------------------------|---------|--|

| В.                  | <i>Indium Tin Oxide (ITO): In</i> <sub>2</sub> <i>O</i> <sub>5</sub> <i>Sn</i> 1     |         |  |

| 1.9                 | Objectives of Thesis                                                                 |         |  |

| 1.10                | •                                                                                    |         |  |

| 1.11                | Organization of Thesis                                                               | 22      |  |

| 1.12                | References                                                                           | 25      |  |

| Снарті              | ER 2: ANALOG AND LINEARITY PERFORMANCE OF TRANSPARENT (                              | SATE    |  |

| RECESS              | ED CHANNEL (TGRC) MOSFET FOR HIGH PERFORMANCE APPLI                                  | CATIONS |  |

|                     |                                                                                      | 31      |  |

| 2.1                 | Introduction                                                                         | 32      |  |

| 2.2                 | Device Design and its Description                                                    | 33      |  |

| 2.3                 | Simulation Methodology and Calibration                                               | 34      |  |

| 2.4                 | Fabrication Feasibility                                                              | 36      |  |

| 2.5                 | Results and Discussion.                                                              | 37      |  |

| 2.5.                | 1 Analog Performance                                                                 | 37      |  |

| 2.5.                | 2 Intermodulation and Linearity Performance                                          | 42      |  |

| A.                  | Linearity Performance                                                                | 42      |  |

| <i>B</i> . <i>I</i> | ntermodulation Distortion                                                            | 47      |  |

| 2.6                 | Summary                                                                              | 50      |  |

| 2.7                 | References                                                                           | 51      |  |

| Снарті              | ER 3: RELIABILITY ISSUES OF IN <sub>2</sub> O <sub>5</sub> SN GATE ELECTRODE RECESSE | ED      |  |

| CHANN               | EL MOSFET: IMPACT OF INTERFACE TRAP CHARGES AND TEMPE                                | RATURE  |  |

| ••••                |                                                                                      | 55      |  |

| 3.1                 | Introduction                                                                         | 56      |  |

| 3.2                 | Device Design and its Description                                                    | 57      |  |

| 3.3                 | Simulation Methodology and Calibration                                               | 58      |  |

| 3.4                 | Results and Discussion                                                               | 59      |  |

| 3.4.                | 1 Impact of Interface Trap Charges on Analog Performance                             | 59      |  |

| 3.4.2      |         | Impact of Interface Trap Charges on Linearity and Distortion                     |     |

|------------|---------|----------------------------------------------------------------------------------|-----|

| Pe         | rform   | ance                                                                             | 64  |

| 3.4        | 4.3     | Effect of Interface Trap Charges at Low Temperature on Analog,                   |     |

| Lin        | nearity | v and Intermodulation Distortion                                                 | 68  |

| 3.4        | 1.4     | Influence of Interface Trap Charge's Polarity and Density                        | 71  |

| 3.5        | Sun     | nmary                                                                            | 74  |

| 3.6        | Refe    | erences                                                                          | 75  |

|            |         | Investigation of Parasitic Capacitances of In <sub>2</sub> O <sub>5</sub> Sn Gat |     |

|            |         | RECESSED CHANNEL MOSFET FOR ULSI SWITCHING APPLICA                               |     |

| 4.1        |         | oduction                                                                         |     |

| 4.2        |         | ice Design and its Description                                                   |     |

| 4.3        |         |                                                                                  |     |

|            |         | Impact of In <sub>2</sub> O <sub>5</sub> Sn on Parasitic Capacitances            | 82  |

|            |         | Impact of Gate Length $(L_G)$ Miniaturization                                    |     |

| 4.3        | 3.3     | Impact of Variation of Negative Junction Depth (NJD)                             |     |

| 4.4        | Sun     | nmary                                                                            |     |

| 4.5        | ·       |                                                                                  | 93  |

| Снарт      | ER 5:   | RF AND SMALL SIGNAL BEHAVIOUR OF IN2O5SN GATE ELECTRO                            | ODE |

| RECES      | SED C   | HANNEL MOSFET                                                                    | 97  |

| 5.1        | Intro   | oduction                                                                         | 98  |

| 5.2        | Dev     | ice Design and its Description                                                   | 99  |

| 5.3        | Sim     | ulation Methodology                                                              | 100 |

| 5.4        | Res     | ults and Discussion                                                              | 100 |

| 5.4        | 4.1     | Small Signal Behaviour Modeling                                                  | 100 |

| A.         | Admit   | tance (Y) Parameters                                                             | 101 |

| В.         | Imped   | lance (Z) Parameters                                                             | 103 |

| <i>C</i> . | Scatte  | ering (S) parameters                                                             | 106 |

| D.         | Hybri   | id (h) Parameters                                                                | 110 |

| 5.4        | 4.2 Extraction of RF FoMs                                             | 113                                                |

|------------|-----------------------------------------------------------------------|----------------------------------------------------|

| A.         | Transit Frequency $f_T$                                               | 113                                                |

| В.         | Maximum Oscillation Frequency $f_{MAX}$                               | 114                                                |

| 5.5        | Summary                                                               | 115                                                |

| 5.6        | 116                                                                   |                                                    |

|            |                                                                       |                                                    |

| Снарт      | TER 6: IN <sub>2</sub> O <sub>5</sub> Sn Gate Electrode Recessed Ch   | ANNEL MOSFET FOR AN X-                             |

| RAY D      | OSIMETER AND BIOSENSING APPLICATION                                   | 121                                                |

| 6.1        | Introduction                                                          | 122                                                |

| 6.2        | In <sub>2</sub> O <sub>5</sub> Sn Gate Electrode Recessed Channel MOS | SFET: An X-Ray Dosimeter                           |

|            |                                                                       | 125                                                |

| 6.2        | 2.1 Device Design and its Description                                 | 125                                                |

| 6.2        | 2.2 Simulation Methodology and Calibration                            | 127                                                |

| 6.2        | 2.3 Results and Discussion                                            | 129                                                |

| A.         | Impact of X-Ray Doses                                                 | 129                                                |

| В.         | Effects of Varying the Oxide Thickness on Radiati                     | on Sensitivity134                                  |

| 6.3        | Ultra-Low Power Dielectric Modulated Nano-ga                          | ap Embedded In <sub>2</sub> O <sub>5</sub> Sn Gate |

| Elect      | trode Recessed Channel MOSFET for Biosensing                          | Application136                                     |

| 6.3        | 3.1 Device Structure                                                  | 136                                                |

| 6.3        | 3.2 Results and Discussion                                            | 137                                                |

| A.         | Effect on Parasitic Capacitances                                      | 143                                                |

| В.         | Noise Assessment                                                      | 144                                                |

| <i>C</i> . | Effect of Nano-gap Cavity Length                                      | 145                                                |

| 6.4        | Summary                                                               | 147                                                |

| 6.5        | References                                                            | 149                                                |

|            |                                                                       |                                                    |

| Снарт      | TER 7: CONCLUSION AND FUTURE SCOPE                                    | 155                                                |

| 7.1        | Conclusion                                                            | 156                                                |

| 7.2        | Future Scope                                                          |                                                    |

| REPRI      | NTS OF JOURNAL PUBLICATIONS                                           |                                                    |

#### **ACRONYMS**

MOSFET Metal-Oxide Semiconductor Field-Effect Transistor

BJT Bipolar Junction Transistor

ICs Integrated Circuits

CMOS Complementary Metal Oxide Semiconductor

VLSI Very-Large-Scale-Integrated

IT Information Technology

SCEs Short Channel Effects

SS Subthreshold Swing

I<sub>OFF</sub> OFF Current

I<sub>ON</sub> ON Current

V<sub>th</sub> Threshold Voltage

DIBL Drain Induced Barrier Lowering

V<sub>DS</sub> Drain-to-Source Voltage

V<sub>GS</sub> Gate-to-Source Voltage

HCEs Hot Carrier Effects

SOI Silicon on Insulator

CNTs Carbon Nanotubes

RC Recessed Channel

TCOs Transparent Conducting Oxides

ITO Indium Tin Oxide

IoT Internet of Things

TGRC Transparent Gate Recessed Channel

CRC Conventional Recessed Channel

RF Radio Frequency

FOMs Figure of Merits

NJD Negative Junction Depth

TFP Transconductance Frequency Product

EDP Energy Delay Product

GBP Gain Bandwidth Product

S Scattering parameters,

Z Impedance parameters,

Y Admittance parameters,

*h* Hybrid parameters

$f_T$  Cut-off frequency

$f_{MAX}$  Maximum oscillator frequency

SRH Shockley-Read-Hall

ITRS International Technology Roadmap for Semiconductor

VIP2 Second order voltage intercept point

VIP3 Third order voltage intercept point

IIP3 Third order current intercept point

IMD3 Third order intermodulation distortion

HD3 Third-order harmonic distortion

HD2 Second order harmonic distortion.

IFM Integral Function Method

P<sub>DC</sub> DC power

P<sub>AC</sub> AC power

ITC Interface Trap Charges

NQS Non-Quasi-Static

APTES 3-aminoppropyltriethoxysilane

ELISA Enzyme-Linked Immunosorbent Assay

MDV Marek's disease virus

C<sub>gs</sub> Gate to source capacitance

C<sub>gd</sub> Gate to drain capacitance

$C_{gg}$  Gate capacitance

L<sub>gap</sub> Length of cavity gap

1

#### **CHAPTER**

#### Introduction

- ❖ This chapter discusses the brief overview of Nanoscale Metal Oxide Semiconductor Field Effect Transistor (MOSFET) and the scaling of MOSFET.

- ❖ Various adverse effects arise due to the scaling of dimensions and different engineering schemes to overcome the limitations; have been discussed in this chapter.

- ❖ Moreover, the chapter describes the reliability issues of CMOS devices. In this respect, the origin of interface trap charges, that are inevitably present in any practical device are discussed and is followed by the discussion of the reliability of TGRC MOSFET.

- ❖ Further, the chapter describes the research gaps that are found while literature survey and is followed by the several possible solutions to overcome these gaps.

- ❖ In this regard, the chapter introduces Indium Tin Oxide (In<sub>2</sub>O<sub>5</sub>Sn) popularly known as ITO as a conducting gate material on to the recessed channel (RC) MOSFET.

- ❖ Thereafter, the significant merits offered by TGRC MOSFET are discussed that is extended with the major challenges faced by the conventional RC MOSFET.

- ❖ Thus, the chapter describes the primary objective of this thesis followed by an overview of all the chapters.

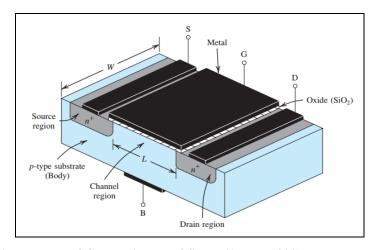

#### 1.1 OVERVIEW OF NANOSCALE MOSFET

Metal-Oxide Semiconductor Field-Effect Transistor (MOSFET) and bipolar junction transistor (BJT) are two major types of three-terminal semiconductor devices. Although both transistors offer unique features and areas of application, especially in the design of integrated circuits (ICs), MOSFET has become the most widely used electronic device and using this as the basic component, the entire circuits are fabricated on a single silicon chip. MOSFETs can be made quite small (requiring a small area on the silicon IC chip), and has simple manufacturing process and also requires very low power consumption as compared to BJT. The unrelenting ever increasing demand for high speed and dense ICs is the driving force for scaling down the CMOS technology to nanometer nodes that has resulted into transforming the state of art of designing the IC, by providing the stability of operation, low static power dissipation, and noise immunity to devices (Heyns & Tsai, 2009; Moore, 1975). These properties have made it possible on a single IC chip to implement very sophisticated, very-large-scale-integrated (VLSI) digital circuits.

Figure 1.1: Schematic structure of Conventional MOSFET (Arora, 1993).

From past four decades, progress in IC technology has become the driving power in revolution of Information Technology (IT), and marvelously changed the whole world and our lives too. The great triumph of the CMOS devices is necessarily offered by the enhanced drive current and the higher cut off frequency acquired by scaling down the CMOS devices. The scaling of the CMOS devices follows the wellknown Moore's law proposed by Gordon Moore (the co-founder of Intel Corporation) in 1960's which predicts that the number of transistors per IC would double approximately every two years (Moore, 1975). Aggressive scaling of MOSFET down to nanometer regime is administered by the need of higher packing density, low operating power, and high switching speed. The constant scaling of MOSFET enhances its switching speed and also the cut-off frequency to Giga-Hertz regime and thus makes it appropriate for wireless and high-frequency applications.

However, the aggressive scaling of MOSFET fallouts into several critical issues such as various short channel effects (SCEs) (Chaudhry & Kumar, 2004). These SCEs degrades the performance of MOSFET and also increases the subthreshold swing (SS) to a value greater than the fundamental limit of MOSFET, i.e., 60mV/decade. Moreover, the SCEs increases the leakage current, while the supply voltage can no longer be scaled down, both of which result in increased power consumption. Along with various SCEs, and reduced channel length, the passive power density approaches the active power density (in magnitude). To mitigate the standby power dissipation, lower OFF-state current (I<sub>OFF</sub>) is required. However, the leakage current increases exponentially because the SS of MOSFET has a minimum value of 60mV/decade at room temperature. To overcome these flaws, various novel device architectures and materials engineering have been proposed such as multi-gate architectures of MOSFET, new gate dielectric materials, asymmetric channel doping engineering, and much more (Ferain et al, 2011; Kranti et al, 2004). Since MOSFET is employed as a switch in digital applications; thus, the prime requirement for switching applications is steeper ON/OFF transitions, i.e., lower SS and higher current switching ratio, i.e., I<sub>ON</sub>/I<sub>OFF</sub> ratio. The lower SS reduces the static power dissipation whereas, the higher I<sub>ON</sub>/I<sub>OFF</sub> ratio determines the performance level of the device. However, the variously reported device architectures for MOSFET successfully enhances the I<sub>ON</sub>/I<sub>OFF</sub> ratio, but the fundamental limit of MOSFET put constraints on SS and limit SS to 60mV/decade. Thus, the MOSFET has a fundamental limitation on SS to 60mV/decade at room temperature that is primarily offered by its current switching process, i.e., thermionic (temperature dependent) injection of electrons over the energy barrier. This fundamental limit on SS restricts

further scaling of supply voltage below 1V due to the increased leakage current and various SCEs (Abuelma'atti, 2013; Seabaugh & Zhang, 2010).

#### 1.2 SCALING OF MOSFET

Reduction of cost per logic function and per stored bit, and simultaneously increasing the switching speed of logic gates is the key aim of the entire research and development efforts in VLSI electronics. Further, the aim has been achieved and resulted in new generations of microchips having a higher clock frequency than their predecessor and comprising more transistors.

Scaling was first proposed by Dennard et al (Dennard et al, 1974) with the idea of reducing the device without affecting the voltage-current behavior of large devices. Rules of scaling given by him are known as constant field scaling. In constant field scaling, all the dimensions and voltages are reduced by a scaling factor  $\kappa(>1)$ , that result constant electric field inside the device as those of an original device (Chatterjee et al, 1980; Majima et al, 2001).

Constant voltage scaling and constant field scaling are the commonly used types of scaling. Constant field scaling requires a reduction in the power supply voltage as one decreases the minimum feature size. However, it yields the largest reduction in the power-delay product of a single transistor. Constant voltage scaling is a preferred scaling method since it provides voltage compatibility with older circuit technologies. Increase in electric field with the reduction in the minimum feature length is the disadvantage of constant voltage scaling and it leads to mobility degradation, velocity saturation, lower breakdown voltages, and increased leakage currents. There is another scaling theory, Brew's scaling theory (Brews, 1979), according to which the channel doping concentration in bulk MOSFET's should be increased to alleviate the short-channel effects. The channel length of the MOSFET was around 10 µm when it developed in 1960. Today most of the ICs utilize CMOS technology with channel length around 30 nm.

Scaling-down has the following advantages:

- With shorter interconnects and smaller transistors, more circuits can be fabricated on to the each silicon wafer. This leads to reduction in cost of circuits.

- Smaller transistors and shorter interconnects also lead to reduction in parasitic capacitances which increases the speed of ICs.

- When transistor is scaled down, it leads to reduction in power supply voltages as well as power consumption.

However, downscaling has its own problem at very short gate length (sub-nm range) (Hu et al, 2010). These are:

- Static and dynamic power consumption.

- Overheating and possible evaporation become major concerns.

- Increased electric field within the oxide and increased leakage gate-current.

#### 1.3 SHORT CHANNEL EFFECTS (SCES)

The channel length and width must be reduced for the future design of ULSI to realize high packing densities and cut-off frequencies. Reducing the channel length leads to SCEs, whereas reduction in current drive is obtained owing to sinking the channel width (Chau et al, 2004). To overcome such scaling limitations and realize high-performance MOS transistors, several techniques have been proposed. MOSFET scaling results in increased SCEs, the most pronounced of which is threshold voltage  $(V_T)$  roll-off, DIBL, hot carrier effect, mobility degradation and velocity overshoot.

#### 1.3.1 Threshold Voltage $(V_{th})$ Roll-off

The key parameter that characterizes SCEs is the degradation of  $V_{th}$  with decrease in channel length. The change (decrease) in threshold voltage with change (reduction) in gate length is called the "Threshold voltage roll-off". When the device is reduced to nanoscale regime, the charge distribution in the channel is influenced by the field originating from the source/drain. Thus, the value of threshold voltage in a short channel device decreases from the constant value maintained in a long channel

device. Mathematically, threshold voltage roll-off is the difference between the threshold voltage of a short channel MOSFET and that of a long channel MOSFET.

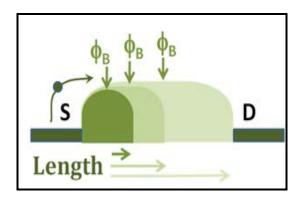

#### 1.3.2 Drain Induced Barrier Lowering (DIBL)

In 1988, Kit Man Cham et al. (Cham et al, 2012) reported that drain induced barrier lowering (DIBL) results an increment in the leakage current in short channel devices as the drain to source voltage is increased (as shown in Figure 1.2). In a short channel MOSFETs, the potential barrier can be controlled by both the drain-to-source voltage (V<sub>DS</sub>) and the gate-to-source voltage (V<sub>GS</sub>). When V<sub>DS</sub> increases, potential barrier in the channel decreases which leads to DIBL. The reduction in the potential barrier eventually allows electron flow between the source and the drain, even if V<sub>GS</sub> is lower than the threshold voltage. The channel current that flows under these circumstances (V<sub>GS</sub><V<sub>T</sub>) is called the sub-threshold current (Hu et al, 1985).

Figure 1.2: Drain Induced Barrier Lowering (Al-Mistarihi et al, 2013).

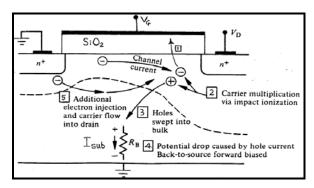

#### 1.3.3 Hot Carrier Effects (HCEs)

Since device voltages are difficult to scale to arbitrarily small values, electric fields tend to be increased at smaller geometries. Thus, short channel devices reflected various hot carrier effects as shown in Figure 1.3, and carrier multiplication and impact ionization may result owing to the reversed biased drain junction. Impact ionization breaks covalent bond and creates holes which contribute to substrate current and some of the holes move to the source, where they lower the source barrier that result in electron injected into p-region from source (Hu et al, 1985).

Figure 1.3: Cross-Sectional View of n-channel MOSFET showing Injection of Hot-Carriers due to shortening of channel length (Arora, 1993).

Transport of the energetic electrons over (or tunneling through) the barrier into the oxide is another hot electron effect. These electrons become trapped in the oxide, resulting in the change in the threshold voltage and transfer characteristics of the device (Ogura et al, 1980).

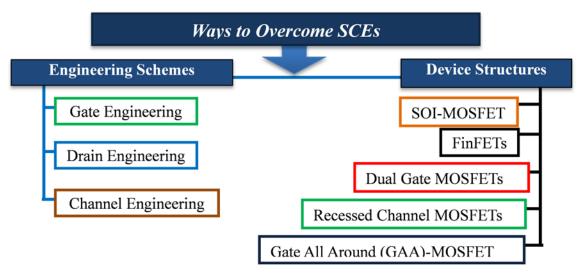

#### 1.4 Engineering Schemes to Overcome SCEs

Since, SCEs hampered the device operation and reduce device performance; these SCEs should be minimized or eliminated, so that a physical short channel device can preserve the electrical long channel behaviour. There are numerous device engineering schemes (as shown in **Figure 1.4**) that have been reported in literature in last few years to get over these problems.

Figure 1.4: Different schemes to alleviate SCEs in nano-scale MOSFET.

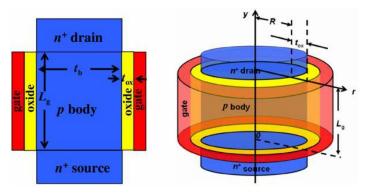

# 1.5 DEVICE CONCEPTS

Continuous increase in the packaging density and the speed of operation of integrated circuits are the major concern for the researchers around the world. Eventually the classical or conventional MOSFET structures have disappeared and new class of devices with new structures using new innovative materials have been introduced. In addition, the recent scaling process has led to arise of novel design concepts for further increase in the integration density.

These concepts span from strained-silicon MOS devices where the silicon channel is replaced by strained silicon to enhance the carrier mobility, to depletedsubstrate devices such as FinFETs, single-gate or double-gate silicon on insulator (SOI) devices (Hisamoto et al, 2000), vertical transistors, and even carbon nanotubes (CNTs) (Lin et al, 2011) which represent a completely new device structure.

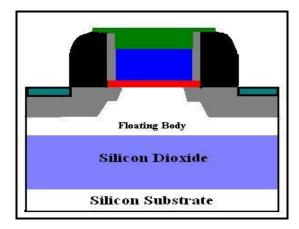

### 1.5.1 Silicon on Insulator (SOI)

One can obtain significant reduction of SCEs by sandwiching a fully depleted SOI device (Choi et al, 1999) between the gate electrodes connected together as shown in Figure 1.5. The SOI technology dielectrically isolates components and in conjunction with the lateral isolation, reduces various parasitic circuit capacitances, and thus, eliminates the possibility of latch-up failures.

Figure 1.5: Silicon-On-Insulator MOSFET(Choi et al, 1999).

SOI technology offers superior devices with excellent radiation hardness and high device density. In addition, for scaling devices into deep-submicron regime, SOI devices are more suitable with their steeper sub threshold slope which facilitates scaling of the threshold voltage for low-voltage low-power applications.

### 1.5.2 Dual Gate MOSFET

F. Balestra et.al in 1987 (Balestra et al, 1987) proposed a new structure the "Double-Gate" which appears to be one of the most promising due to the shield-effect played by the double gate (**Figure 1.6**), which strongly reduces drain-induced barrier lowering and minimizes threshold sensitivity to channel length. The main idea of a Double Gate MOSFET is to control the Si channel very efficiently by choosing the Si channel width to be very small and by applying a gate contact to both sides of the channel. This concept helps to suppress short channel effects and leads to higher currents as compared to a MOSFET having only one gate. Main problem with this structure is fabrication, since it requires alignment of the two gates.

Figure 1.6: Double-Gate MOSFET (Balestra et al, 1987).

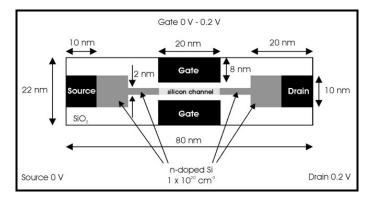

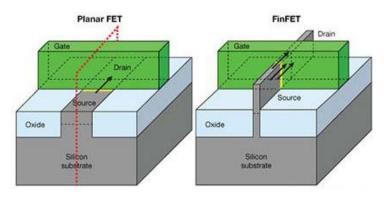

### **1.5.3** Fin FET

FinFET is a three dimensional device in which the channel is built on top of the silicon substrate between the source and drain, called fin. FinFET leads to enhance the current driving capability and reduced leakage current owing to its wrapped channel by gate electrode, so that there can be formed several gate electrodes on each side (Fossum et al, 2003).

Fin-FET offers several advantages such as:

- Low wafer cost