# IMPLEMENTATION OF ANALOG CIRCUITS USING CD-DITA

A PROJECT REPORT

SUBMITTED IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE AWARD OF THE DEGREE OF

MASTER OF TECHNOLOGY

IN

VLSI Design &Embedded System

Submitted by:

HARPREET KAUR

2K16/VLS/10

Under the supervision of

Mr. A. K. SINGH Associate Prof. DTU, Delhi

## **Electronics & Communication Engineering**

DELHI TECHNOLOGICAL UNIVERSITY

(Formerly Delhi College of Engineering) Bawana Road, Delhi-110042

June, 2018

## IMPLEMENTATION OF ANALOG CIRCUITS USING CD-DITA

#### A PROJECT REPORT

SUBMITTED IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE AWARD OF THE DEGREE OF

# MASTER OF TECHNOLOGY IN VLSI Design & Embedded System

Submitted by:

HARPREET KAUR

2K16/VLS/10

Under the supervision of

Mr. A. K. SINGH Associate Prof. DTU, Delhi

## **Electronics & Communication Engineering**

DELHI TECHNOLOGICAL UNIVERSITY

(Formerly Delhi College of Engineering) Bawana Road, Delhi-110042

June, 2018

**Electronics & Communication Engineering**

DELHI TECHNOLOGICAL UNIVERSITY

(Formerly Delhi College of Engineering)

Bawana Road, Delhi-110042

**CANDIDATE'S DECLARATION**

I, Harpreet Kaur, Roll No. 2K16/VLS/10, student of M. Tech. (VLSI DESIGN AND

EMBEDDED SYSTEM), hereby declare that the project Dissertation titled

"IMPLEMENTATION OF ANALOG CIRCUITS USING CD-DITA" which is submitted by

me to the Department of ELECTRONICS AND COMMUNICATION ENGINEERING, Delhi

Technological University, Delhi in partial fulfillment of the requirement for the award of the

degree of Master of Technology, is original and not copied from any source without proper

citation. This work has not previously formed the basis for the award of any Degree, Diploma

Associate ship, Fellowship or other similar title or recognition.

Date:

HARPREET KAUR

**Roll No. 2K16/VLS/10**

M. Tech. (VLSI)

i

**Electronics & Communication Engineering**

DELHI TECHNOLOGICAL UNIVERSITY

(Formerly Delhi College of Engineering)

Bawana Road, Delhi-110042

**CERTIFICATE**

I hereby certify that the Project Dissertation titled "IMPLEMENTATION OF ANALOG

CIRCUITS USING CD-DITA" which is submitted by HARPREET KAUR, Roll No 2K16/VLS/10

Department of Electronics and Communication Engineering, Delhi Technological University, Delhi

in partial fulfillment of the requirement for the award of the degree of Master of Technology, is a

record of the project work carried out by the students under my supervision. To the best of my

knowledge this work has not been submitted in part or full for any Degree or Diploma to this

University or elsewhere.

Place: Delhi

Date

Mr. A.K. SINGH (Associate Professor) ECE DEPTT.

DELHI TECHNOLOGICAL UNIVERSITY

ii

**Electronics & Communication Engineering**

DELHI TECHNOLOGICAL UNIVERSITY

(Formerly Delhi College of Engineering)

Bawana Road, Delhi-110042

**ACKNOWLEDGEMENT**

I express my deepest gratitude to my project guide Associate Prof. A. K. SINGH, Department

of Electronics and Communication Engineering, Delhi Technological University

whose encouragement, guidance and support from the initial to the final level enabled me to

develop an understanding of the subject. His suggestions and ways of summarizing the things

made me to go for independent studying and trying my best to get the maximum in my

topic, this made my circle of knowledge very vast. I am highly thankful to him for guiding me

in this project.

I also wish to express my gratitude to Prof. S. Indu (HOD, ECE Dept.), Prof. D. R. Bhaskar,

Prof. Neeta Pandey and Prof. Rajeshwari Pandey for their constant support and guidance.

Finally, I take this opportunity to extend my deep appreciation to my family and friends, for all

that they meant to me during the crucial times of the completion of my project.

Date:

HARPREET KAUR

**Roll No. 2K16/VLS/10**

M. Tech. (VLSI)

iii

## **INDEX**

| Ti | tle                                                              | Page No. |

|----|------------------------------------------------------------------|----------|

| Li | st of figures                                                    | vi       |

| Li | st of Tables                                                     | xi       |

| Li | st of Abbreviations                                              | xii      |

| Al | ostract                                                          | XV       |

| 1. | Introduction                                                     | 1-6      |

|    | 1.1. Development of technologies                                 | 2        |

|    | 1.2. Voltage and current mode signal processing                  | 2        |

|    | 1.3. Motivation for CM design circuit                            | 3        |

|    | 1.4. Evolvement of CM blocks                                     | 4        |

|    | 1.5. Objective                                                   | 5        |

|    | 1.6. Organization of Thesis                                      | 6        |

| 2. | Literature Survey                                                | 7-12     |

|    | 2.1. Introduction                                                | 7        |

|    | 2.2. Review of CDTA Implementations                              | 8        |

|    | 2.3. Review of CM universal filters                              | 9        |

|    | 2.4. Review of Grounded Inductor Simulations                     | 10       |

|    | 2.5. Review of MM filters                                        | 11       |

| 3. | Realization of CD-DITA                                           | 13-50    |

|    | 3.1. Introduction                                                | 13       |

|    | 3.1.1. Ideal CD-DITA                                             | 13       |

|    | 3.1.2. Non Ideal CD-DITA                                         | 15       |

|    | 3.2. Realization of Flipped Voltage Follower (FVF) based CD-DITA | 16       |

|    | 3.2.1. Flipped voltage follower                                  | 16       |

|    | 3.2.2. Current Mirror based on FVF                               | 18       |

|    | 3.2.3. Current differencing unit                                 | 20       |

|    | 3.2.4. Dual output OTA (DO-OTA)                                  | 21       |

|    | 3.3. Characterization of CD-DITA                                 | 24       |

|    | 3.3.1.       | DC characteristics or Large signal analysis                   | 25     |

|----|--------------|---------------------------------------------------------------|--------|

|    | 3.3          | 3.1.1 DC characteristics of CDU section                       | 25     |

|    | 3.3          | 3.1.2 DC characteristics of DO-OTA section                    | 28     |

|    | 3.3          | 3.1.3 DC characteristics of CD-DITA Block                     | 30     |

|    | 3.3.2.       | Small signal analysis (AC characteristics)                    | 33     |

|    | 3.4. Realiz  | zation of CD-DITA based on translinear loop                   | 42     |

| 4. | CD-DITA      | based applications                                            | 50-70  |

|    | 4.1. Basic   | building blocks                                               | 50     |

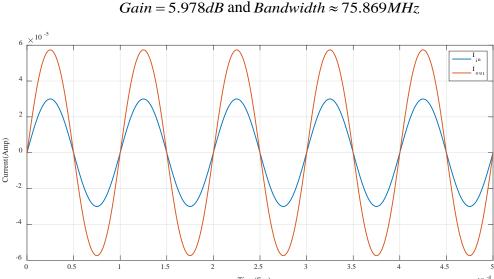

|    | 4.1.1.       | Simple current amplifier                                      | 50     |

|    | 4.1.2.       | Adder or summing amplifier                                    | 52     |

|    | 4.1.3.       | Subtractor or the differential amplifier                      | 54     |

|    | 4.1.4.       | Lossless integrator                                           | 55     |

|    | 4.2. First ( | Order All Pass Filter using CD-DITA                           | 57     |

|    | 4.3. CD-D    | OITA based CM-SIMO type universal filter                      | 60     |

|    | 4.3.1.       | Basic Introduction                                            | 60     |

|    | 4.3.2.       | CM filter based on single CD-DITA                             | 60     |

|    | 4.3.3.       | Sensitivity Analysis                                          | 63     |

|    | 4.3.4.       | Effect of non-idealities of the CD-DITA on filter performance | 63     |

|    | 4.3.5.       | Sensitivity analysis including Non-Idealities                 | 67     |

|    | 4.3.6.       | Simulation results of CD-DITA based CM-SIMO universal filter  | 68     |

| 5. | Proposed     | Applications of CD-DITA                                       | 71-102 |

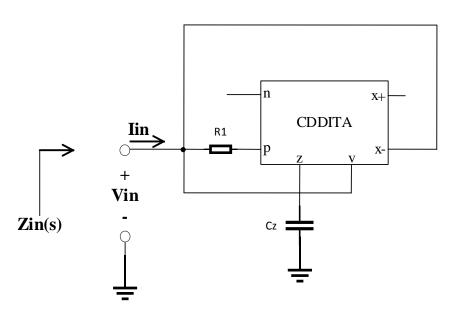

|    | 5.1. Propo   | sed Grounded Inductor and its BPF implementation              | 71     |

|    | 5.1.1.       | Proposed configuration of grounded inductor                   | 71     |

|    | 5.1.2.       | Implementation of BPF using grounded inductor                 | 74     |

|    | 5.2. Propo   | sed MM filter using CD-DITA                                   | 75     |

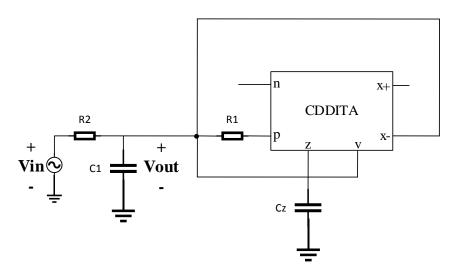

|    | 5.2.1.       | Proposed MM filter circuit                                    | 76     |

|    | 5.2.2.       | Sensitivity Analysis                                          | 78     |

|    | 5.2.3.       | Effect of non-idealities on filter performance                | 79     |

|    | 5.2.4.       | Sensitivity analysis including Non-idealities                 | 82     |

|    | 5.2.5.       | Simulation results                                            | 83     |

| 6. | Conclusio    | on and future work                                            | 103    |

## **LIST OF FIGURES**

| Fig. No.  | Title                                                                              | Page No. |

|-----------|------------------------------------------------------------------------------------|----------|

| Fig. 2.1  | Block diagrams: (a) CDTA (b) CD-DITA                                               | 7        |

| Fig. 3.1  | CD-DITA (a) Schematic symbol and (b) Behavioral model                              | 13       |

| Fig. 3.2  | Non ideal CD-DITA                                                                  | 15       |

| Fig. 3.3  | (a) CD amplifier or Source Follower (b) Flipped Voltage                            |          |

|           | Follower (FVF)                                                                     | 17       |

| Fig. 3.4  | Current Mirror based on FVF                                                        | 19       |

| Fig. 3.5  | CDU based on FVF                                                                   | 20       |

| Fig. 3.6  | DO-OTA[46]                                                                         | 22       |

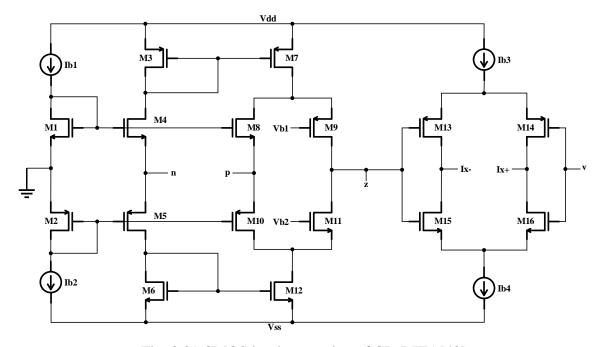

| Fig. 3.8  | CD-DITA based on FVF                                                               | 24       |

| Fig. 3.8  | PSPICE schematic diagram of the CDU                                                | 25       |

| Fig. 3.9  | Current transfer from the $p$ -terminal to the $z$ -terminal                       |          |

|           | $(I_z \text{ vs } I_p)$ with the condition $I_n = 0$ $I_n = 0$                     | 26       |

| Fig. 3.10 | Current transfer from the $p$ -terminal to the $z$ -terminal                       |          |

|           | $(I_z \text{ vs } I_p)$ with parametric sweep on $I_n$                             | 26       |

| Fig. 3.1  | 1 Current transfer from the $n$ -terminal to the $z$ -terminal                     |          |

|           | $(I_z vs I_n)$ with the condition $I_p = 0$                                        | 27       |

| Fig. 3.12 | Current transfer from the $n$ -terminal to the $z$ -terminal                       |          |

|           | $(I_z vs I_n)$ with parametric sweep on $I_p$                                      | 28       |

| Fig. 3.17 | PSPICE schematic diagram of the DO-OTA                                             | 28       |

| Fig. 3.14 | Transconductance transfer from the $z$ -terminal to the                            |          |

|           | $x \pm \text{terminal} (I_{x\pm} \text{vs } V_z) \text{ with } I_{b2} = 100 \mu A$ | 29       |

| Fig. 3.1: | Transconductance transfer from the $z$ -terminal to the                            |          |

|           | $x \pm \text{terminals}(I_{x+} \text{ vs } V_z)$ with $I_{b2}$ as parametric sweep | 30       |

| Fig. 3.16 | PSPICE schematic of CD-DITA block                                                   | 31 |

|-----------|-------------------------------------------------------------------------------------|----|

| Fig. 3.17 | Current transfer from the $p$ terminal to the $x$ + terminal                        |    |

|           | $(I_{x+} \text{ vs } I_p)$ with parametric sweep on $R_z \& I_n = 0$                | 31 |

| Fig. 3.18 | Current transfers from $p$ terminal to $x \pm$ terminal ( $I_{x\pm}$ vs $I_p$ )     |    |

|           | with $I_n = 0$ and $R_z = 3.55k\Omega$                                              | 32 |

| Fig. 3.19 | Current transfer from the $p$ terminal to the $x$ + terminal                        |    |

|           | $(I_{x\pm} \text{ vs } I_p)$ keeping $I_n = 0$ , $R_z = 3.55k\Omega$ and parametric |    |

|           | sweep on $I_{b2}$                                                                   | 33 |

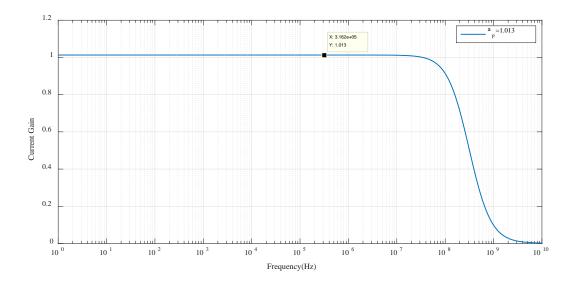

| Fig. 3.20 | Parasitic Current gain from the terminal $p$ to the terminal $z$                    |    |

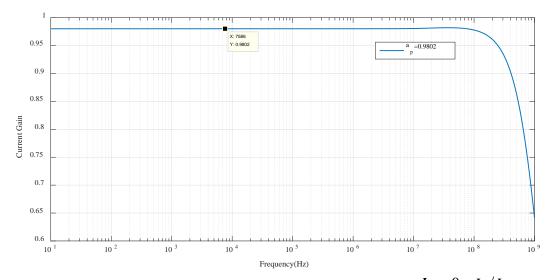

|           | $(I_z/I_p \text{ vs frequency})$ with condition $I_n = 0$                           | 34 |

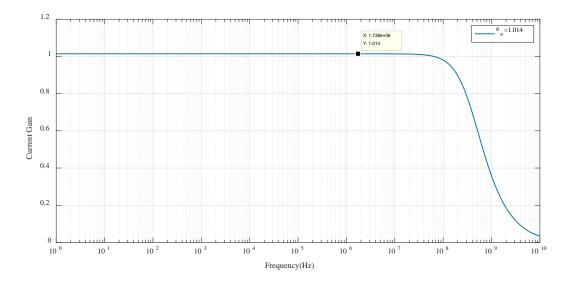

| Fig. 3.21 | Parasitic Current gain from terminal $n$ to terminal $z$                            |    |

|           | $(I_z/I_n \text{ vs frequency }) \text{ with condition } I_n = 0$                   | 34 |

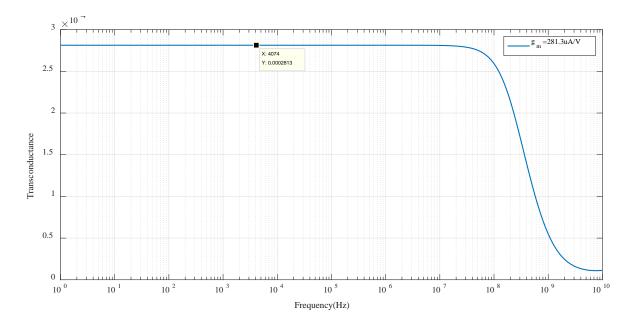

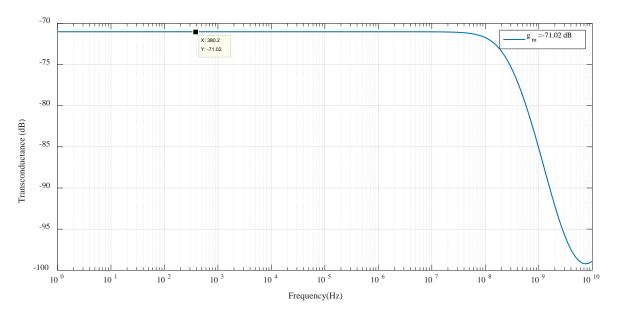

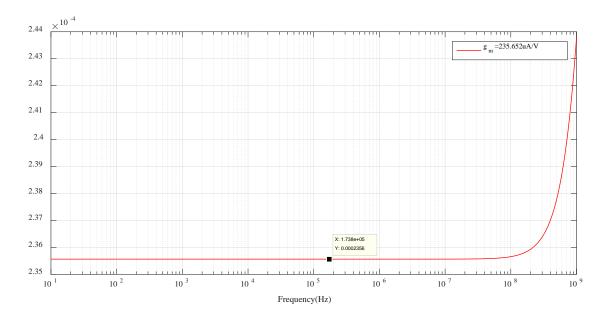

| Fig 3.22  | Transconductance $g_m(I_{x+}/V_z)$ vs frequency (with the                           |    |

|           | condition $I_{b2} = 100 \mu A$                                                      | 35 |

| Fig. 3.23 | Transconductance gain $g_m$ in $dB$ ( $I_{x+}/V_z$ vs frequency)                    |    |

|           | with the condition $I_{b2} = 100 \mu A$                                             | 36 |

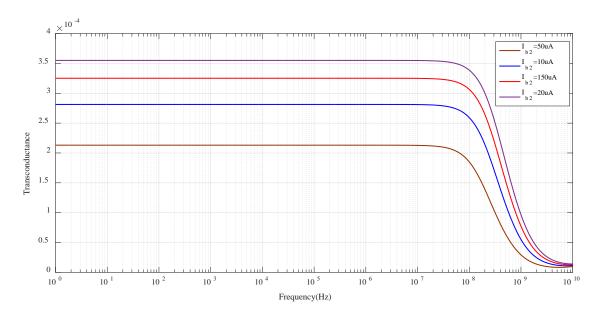

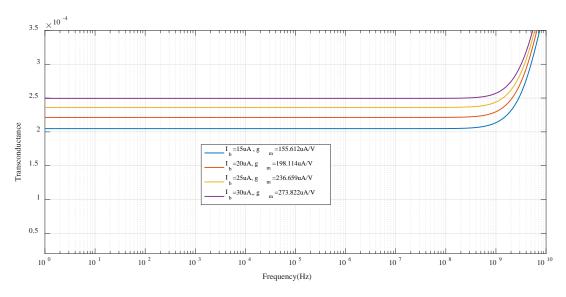

| Fig. 3.24 | Transconductance gain $g_m$ ( $I_{x+}/V_z$ vs frequency)                            |    |

|           | keeping $I_{b2}$ as parametric sweep                                                | 37 |

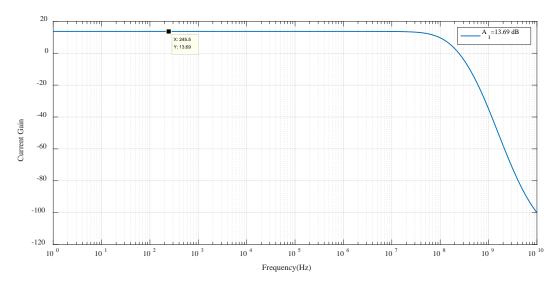

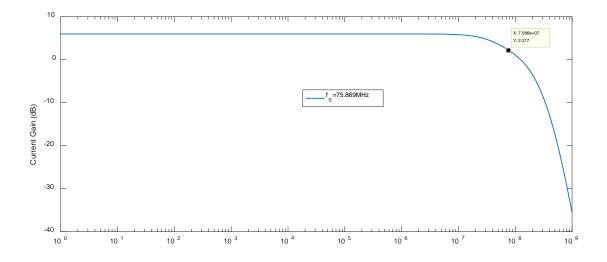

| Fig. 3.25 | Overall Gain of CD-DITA ( $I_{x+}/I_p$ vs frequency)                                |    |

|           | with $I_n = 0$ , $I_{b2} = 100 \mu A$ and $R_z = 17.74 k\Omega$                     | 37 |

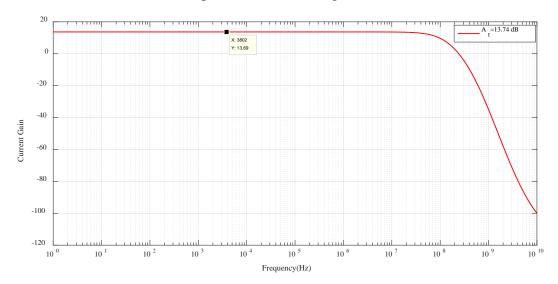

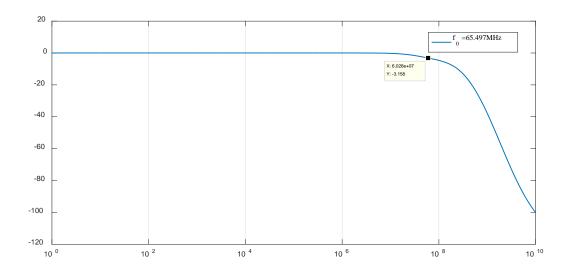

| Fig. 3.26 | Overall Gain of CD-DITA ( $I_{x+}/I_n$ vs frequency) with                           |    |

|           | $I_p = 0$ , $I_{b2} = 100 \mu A$ and $R_z = 17.74 k\Omega$                          | 38 |

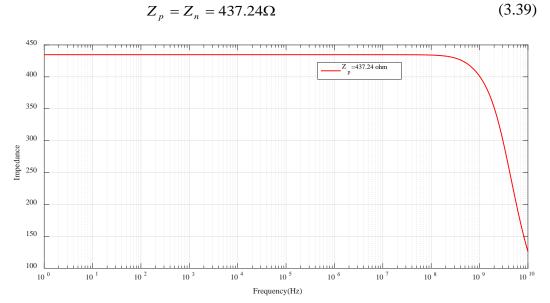

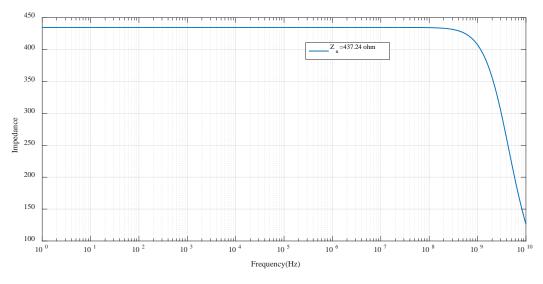

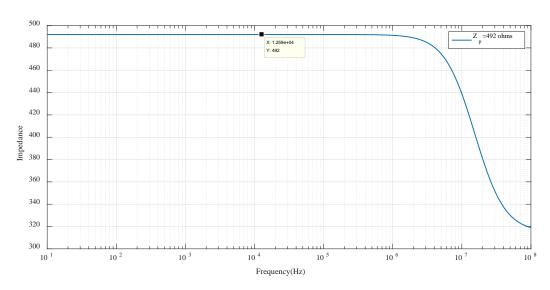

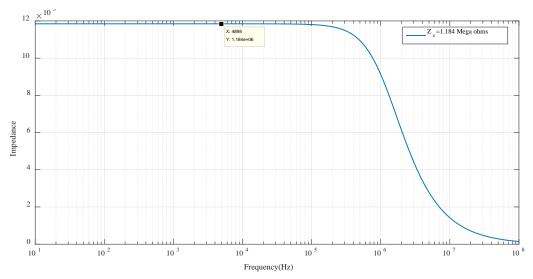

| Fig. 3.27 | Impedance seen through the p-terminal                                               |    |

|           | $(Z_p \text{ vs frequency})$                                                        | 39 |

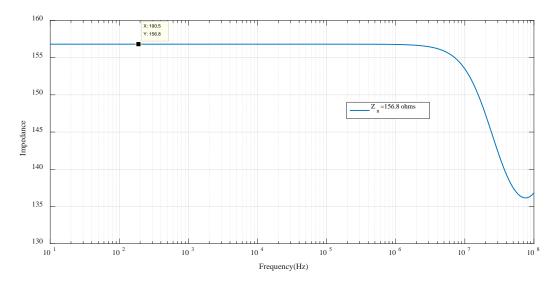

| Fig. 3.28 | Impedance seen through $n$ -terminal ( $Z_n$ vs frequency)                      | 39 |    |

|-----------|---------------------------------------------------------------------------------|----|----|

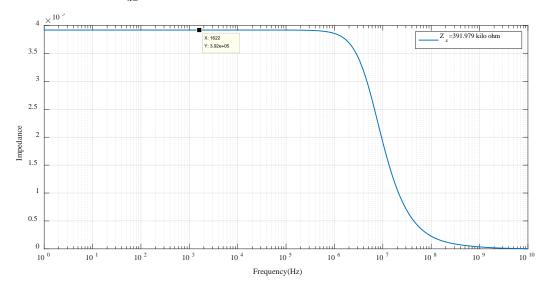

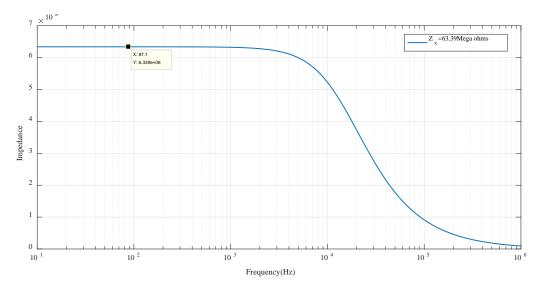

| Fig. 3.29 | Impedance seen through $z$ -terminal ( $Z_z$ vs frequency)                      | 40 |    |

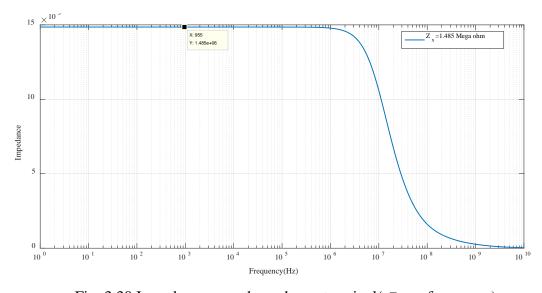

| Fig. 3.30 | Impedance seen through $x \pm \text{terminal} (Z_{x\pm} \text{ vs frequency})$  | 40 |    |

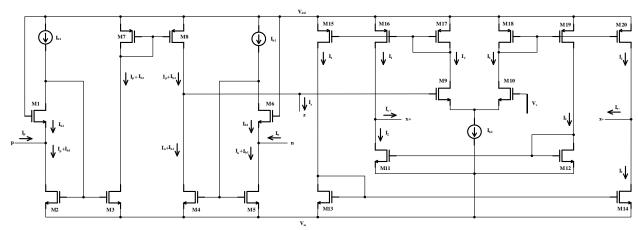

| Fig. 3.31 | CMOS implementation of CD-DITA                                                  | 41 |    |

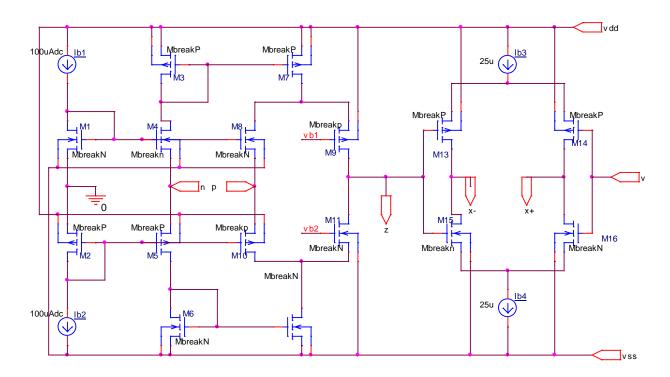

| Fig. 3.32 | PSPICE schematic of CD-DITA block                                               | 44 |    |

| Fig. 3.33 | Parasitic Current gain from $p$ terminal to $Z$ terminal                        |    |    |

|           | with $I_n = 0$ ( $I_z/I_p$ vs frequency)                                        | 45 |    |

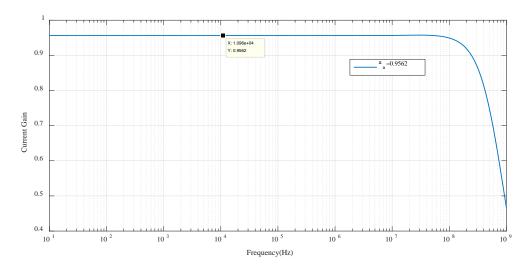

| Fig 3.34  | Parasitic Current gain from $n$ terminal to $z$ terminal with                   |    |    |

|           | $I_p = 0 \ (I_z/I_n \text{ vs frequency})$                                      | 45 |    |

| Fig. 3.35 | Transconductance gain $g_m$ from $\mathcal{Z}$ -terminal to $x$ + terminals     | 46 |    |

| Fig. 3.36 | Transconductance gain $g_m$ from $\mathcal{Z}$ -terminal to $x$ + terminals     |    |    |

|           | with $I_{b3}$ and $I_{b4}$ as parametric sweep ( $I_{x+}  /  V_z$ vs frequency) |    | 46 |

| Fig. 3.37 | Impedance seen through $p$ -terminal ( $Z_p$ vs frequency)                      | 47 |    |

| Fig. 3.38 | Impedance seen through $n$ -terminal ( $Z_n$ vs frequency)                      | 47 |    |

| Fig. 3.39 | Impedance seen through $z$ -terminal ( $Z_z$ vs frequency)                      | 48 |    |

| Fig. 3.40 | Impedance seen through $x \pm \text{terminal } (Z_{x\pm} \text{ vs frequency})$ | 48 |    |

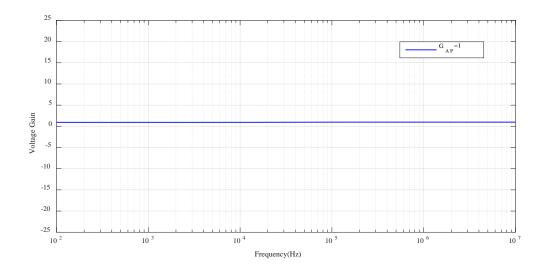

| Fig. 4.1  | Circuit Schematic of current amplifier based on CD-DITA.                        | 50 |    |

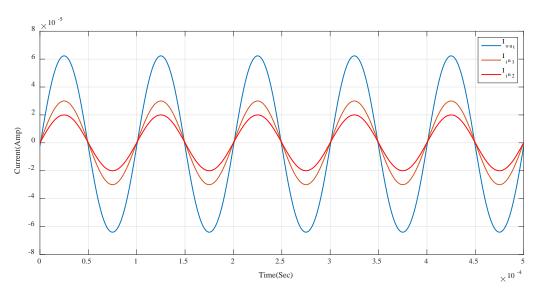

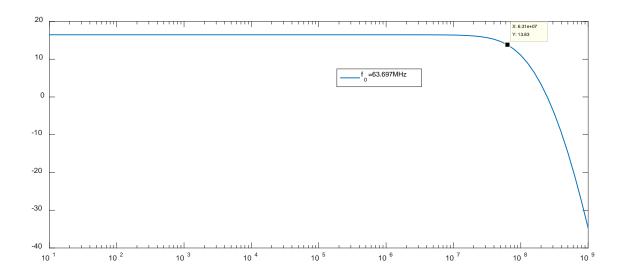

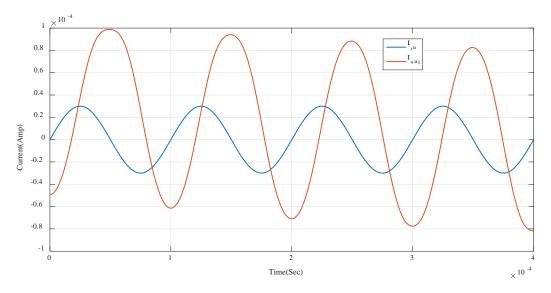

| Fig. 4.2  | o/p waveform of the simple current mirror amplifier matching                    |    |    |

|           | to the sinusoidal i/p waveform                                                  | 51 |    |

| Fig. 4.3  | frequency response of simple current mirror amplifier                           | 51 |    |

| Fig. 4.4  | Schematic of the summing amplifier based on CD-DITA                             | 52 |    |

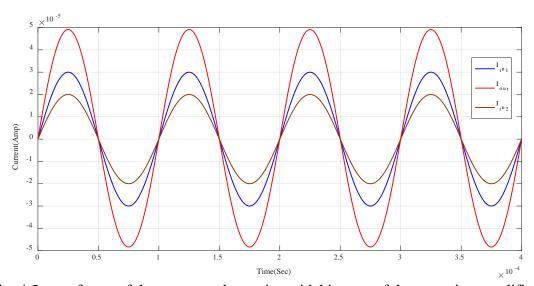

| Fig. 4.5  | waveforms of the output and two sinusoidal inputs of the                        |    |    |

|           | summing amplifier                                                               | 53 |    |

| Fig. 4.6  | the frequency response of the summing amplifier                                 | 53 |    |

| Fig. 4.7   | Schematic of the current differential amplifier              |    |

|------------|--------------------------------------------------------------|----|

|            | based on CD-DITA.                                            | 54 |

| Fig. 4.8   | Simulated waveforms of outputs to two sinusoidal i/p's       |    |

|            | of current differential amplifier based on CD-DITA           | 55 |

| Fig. 4.9   | the frequency response of the current differential amplifier |    |

|            | based on CD-DITA                                             | 55 |

| Fig. 4.10. | Schematic of lossless integrator based on CD-DITA.           | 56 |

| Fig. 4.11  | Simulated o/p waveform of lossless integrator corresponding  |    |

|            | to sinusoidal i/p's                                          | 56 |

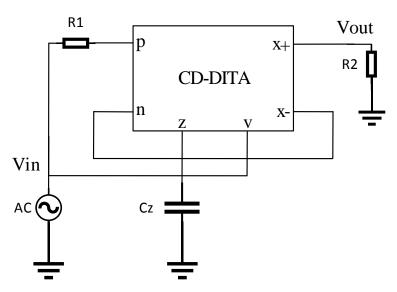

| Fig: 4.12  | Schematic of first order APF based on CD-DITA                | 57 |

| Fig. 4.13  | PSPICE schematic of CD-DITA                                  | 58 |

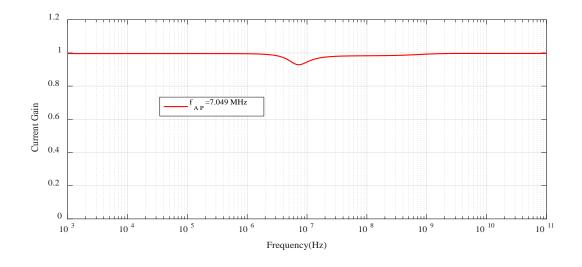

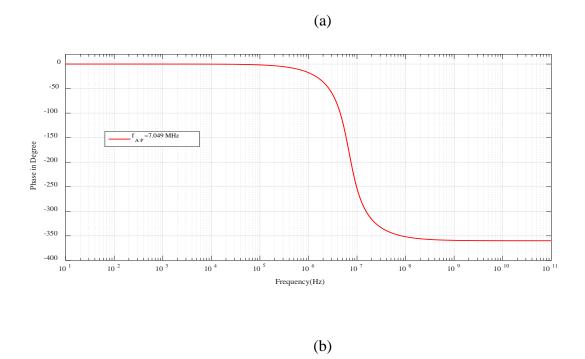

| Fig. 4.14  | Magnitude response of the first order APF                    | 59 |

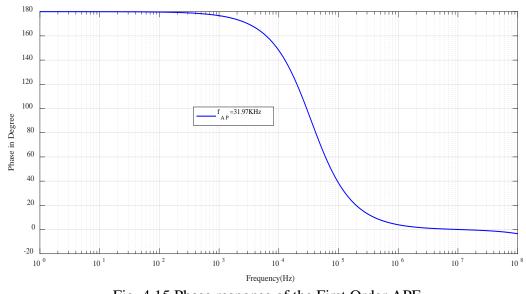

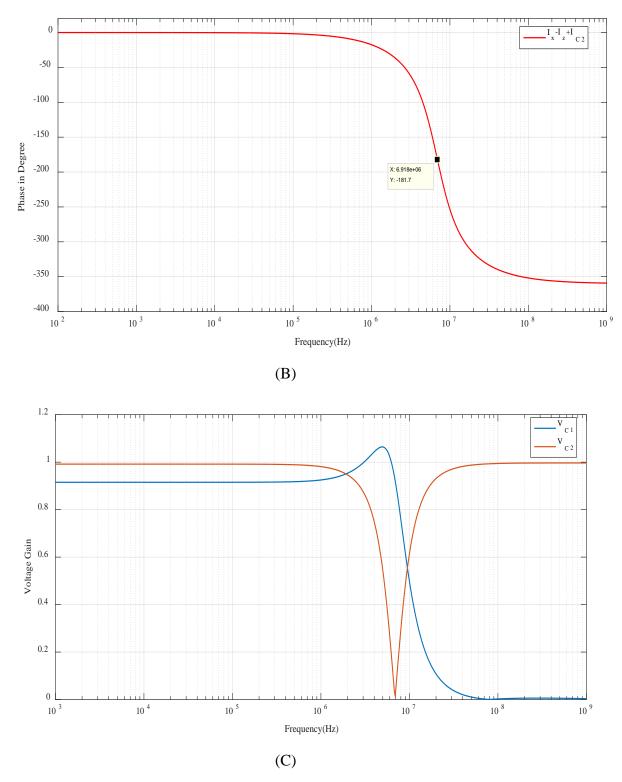

| Fig. 4.15  | Phase response of the First Order APF                        | 59 |

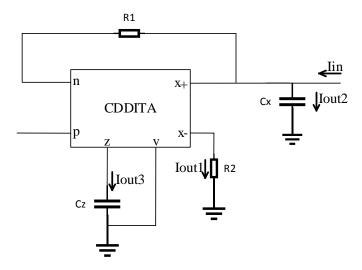

| Fig. 4.16  | CD-DITA based SIMO-type CM Universal filter circuit.         | 60 |

| Fig. 4.17  | CD-DITA circuit model with non-idealities                    | 64 |

| Fig. 4.18  | Simulated filter responses of CD-DITA based                  |    |

|            | CM-universal filter                                          | 69 |

| Fig. 4.19  | Simulated APF: (a) magnitude and (b) phase response          |    |

|            | CM Biquad filter                                             | 70 |

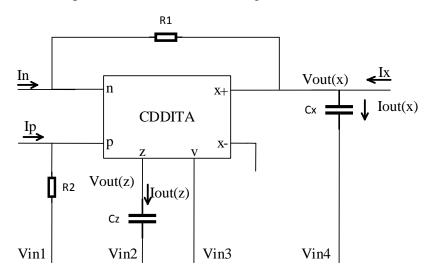

| Fig. 5.1.  | Proposed Grounded Inductor Based on CD-DITA                  | 71 |

| Fig. 5.2   | CD-DITA based on FVF                                         | 73 |

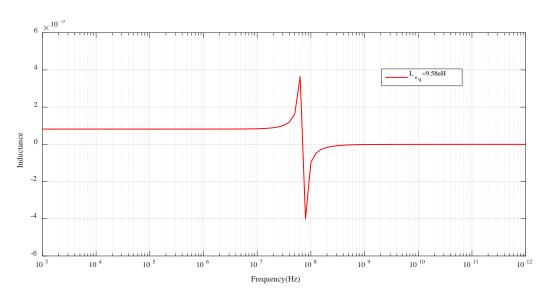

| Fig. 5.3   | Frequency response of the Grounded Inductor Based            |    |

|            | on CD-DITA                                                   | 73 |

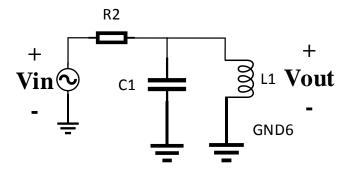

| Fig. 5.4   | BPF using Simple $R, L, C$                                   | 74 |

| Fig. 5.5   | Schematic Symbol for Second Order BPF Using                  |    |

|            | Proposed Grounded Inductor                                   | 75 |

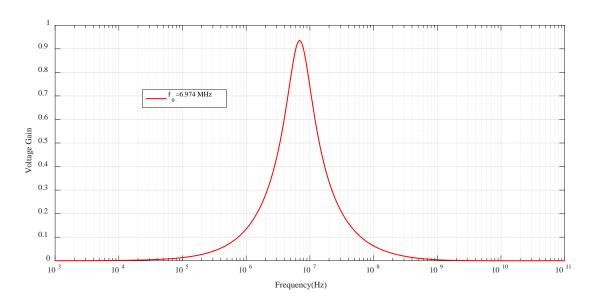

| Fig.5.6    | Frequency Response of BPF using Grounded Inductor            | 75 |

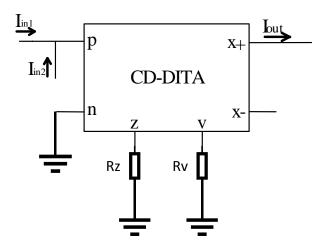

| Fig. 5.7  | Schematic Symbol for Proposed MM filter                             | 76  |

|-----------|---------------------------------------------------------------------|-----|

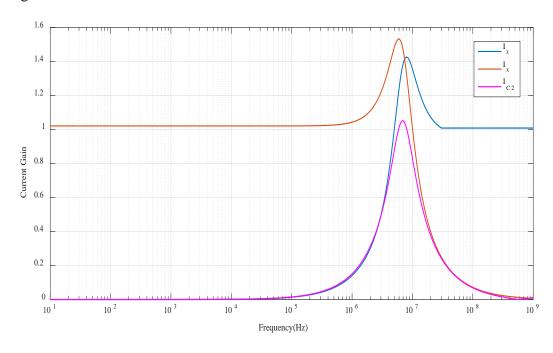

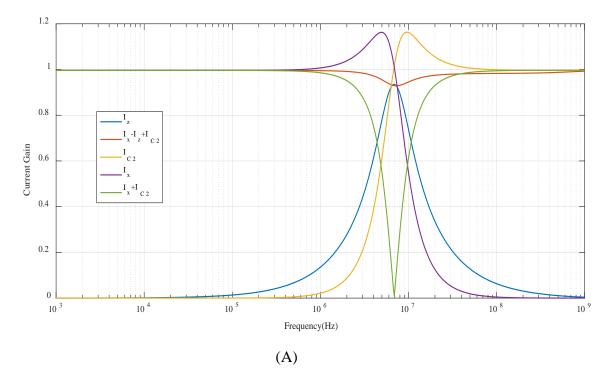

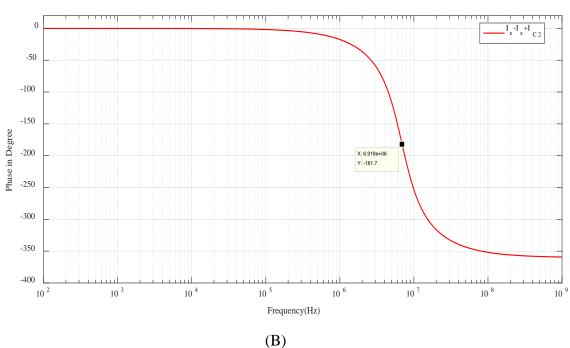

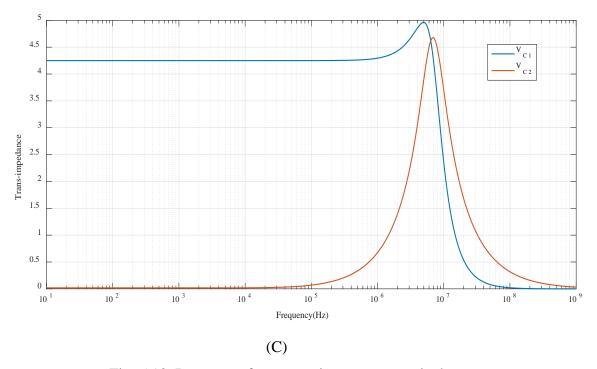

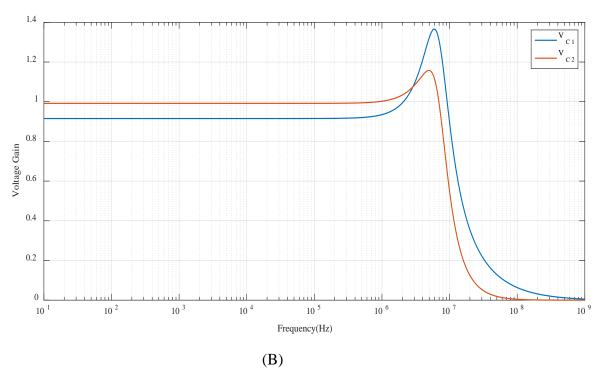

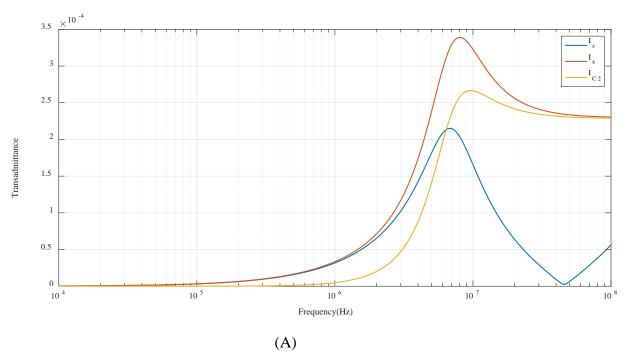

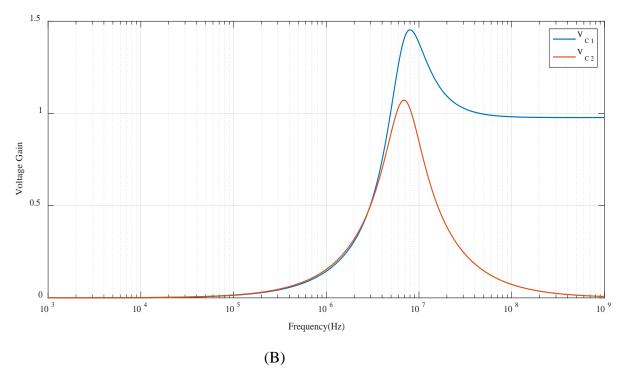

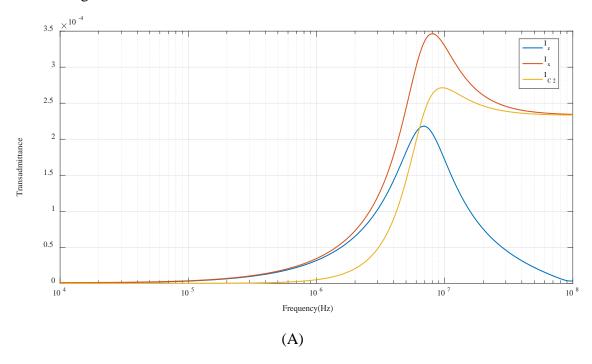

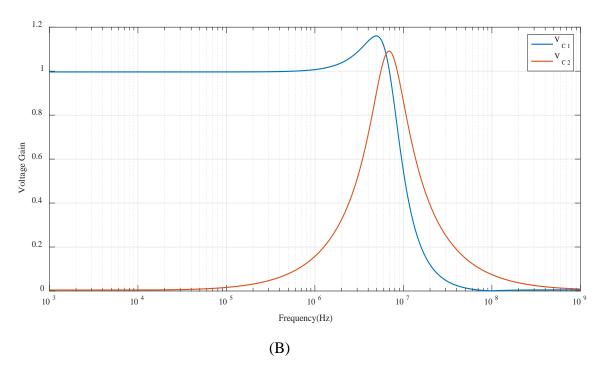

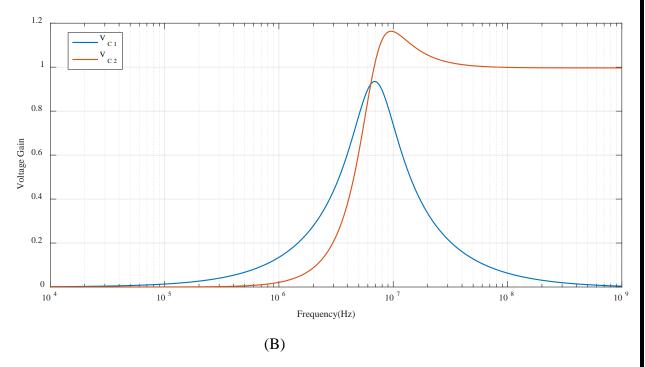

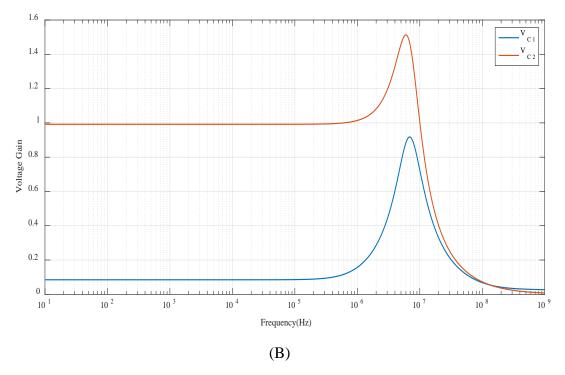

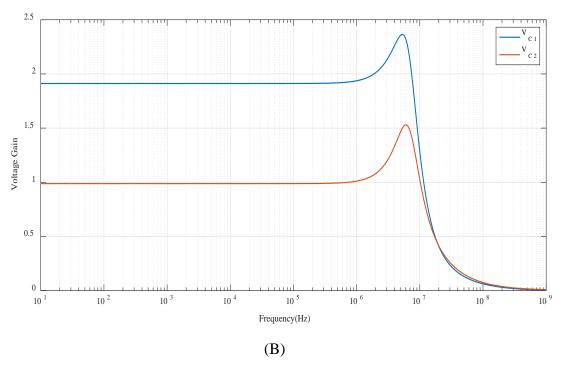

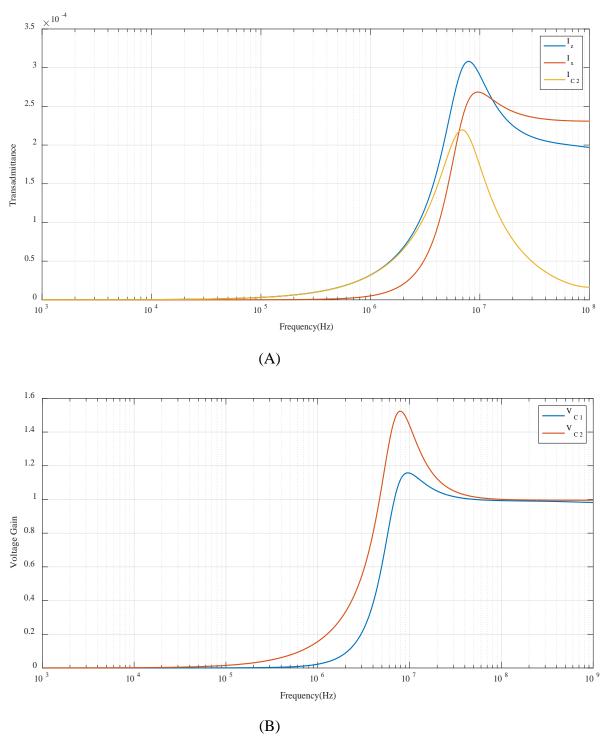

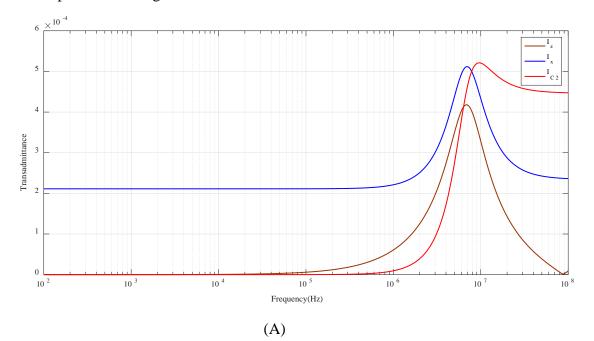

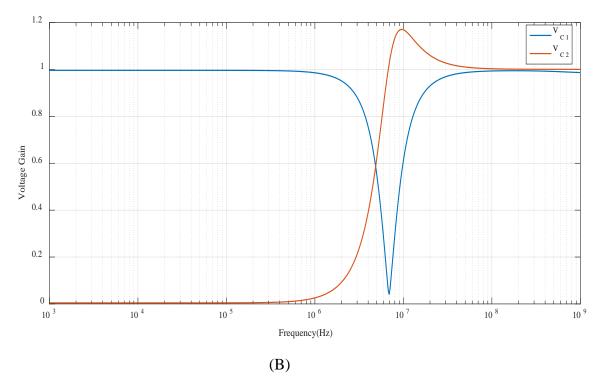

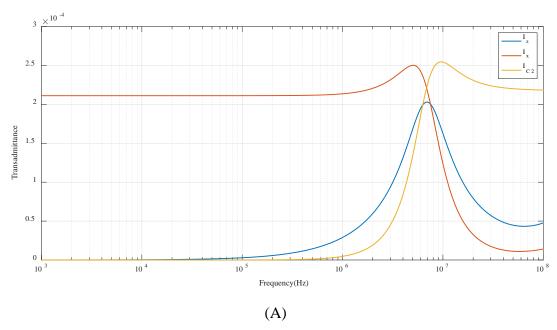

| Fig: 5.8  | Responses for current input at p terminal                           | 84  |

| Fig: 5.9  | Responses for current input at n terminal                           | 85  |

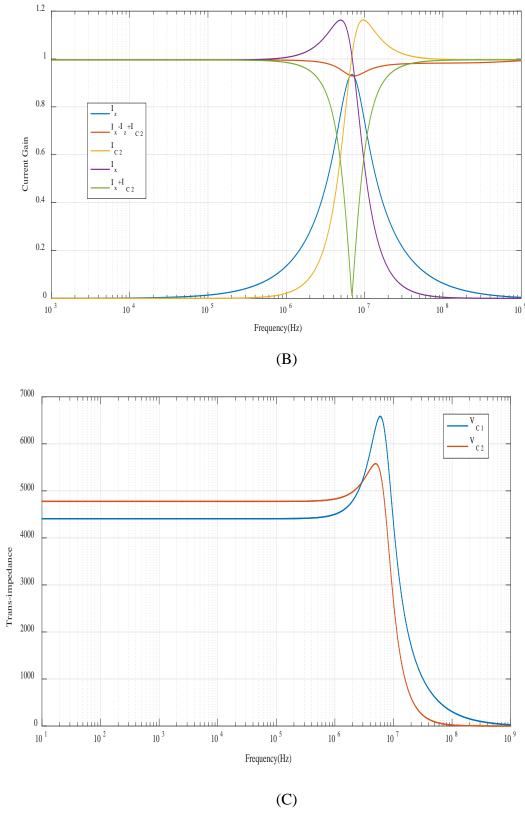

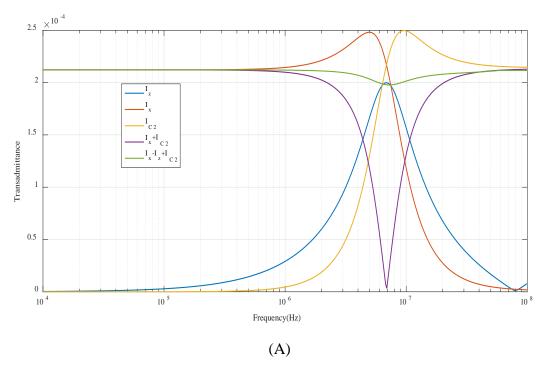

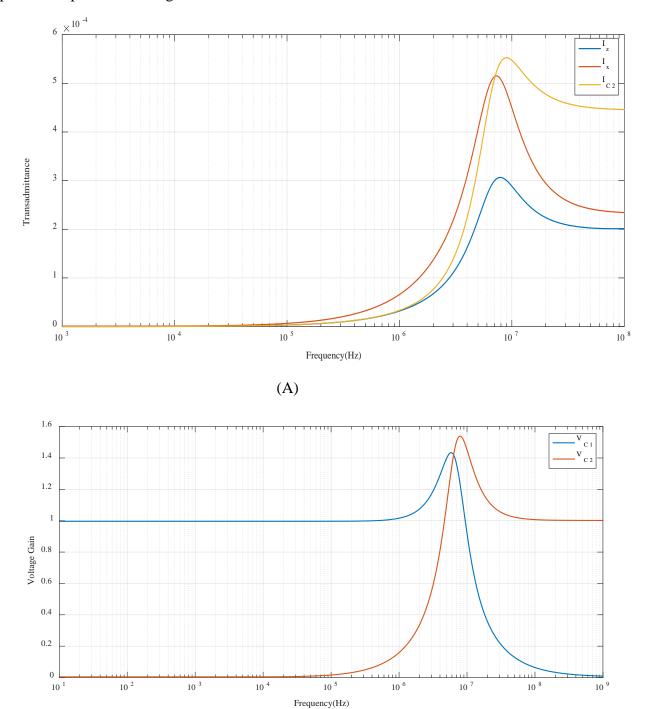

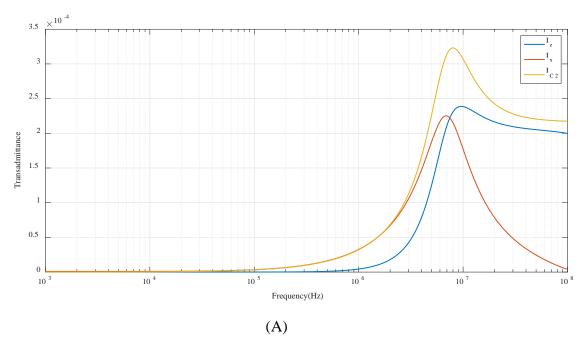

| Fig: 5.10 | Responses for current input at X terminal                           | 87  |

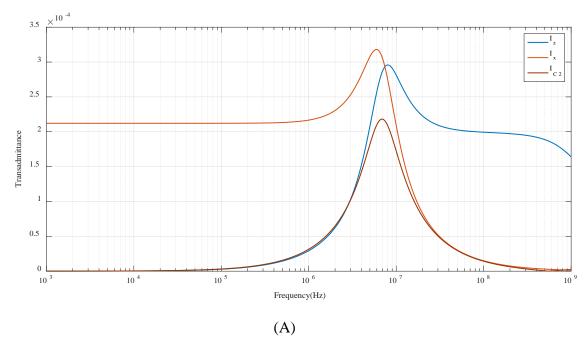

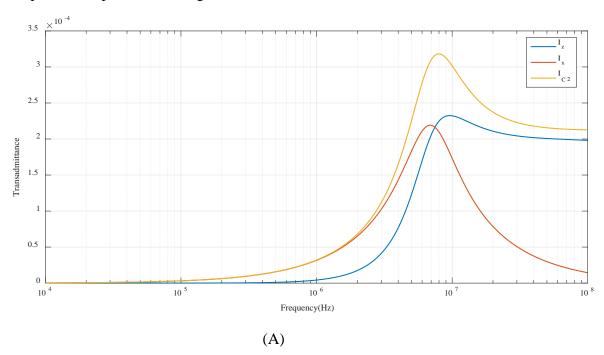

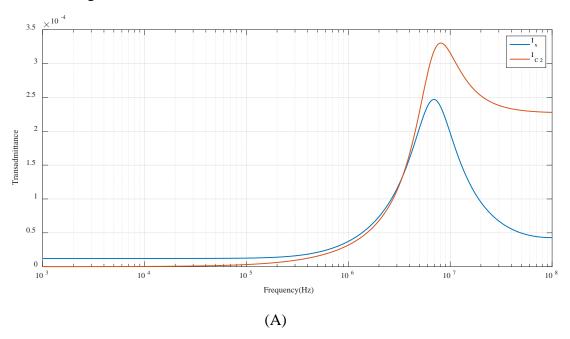

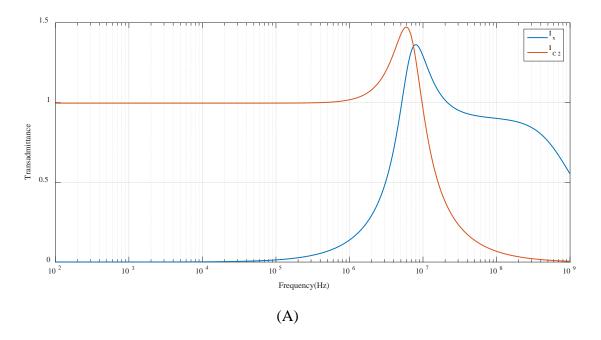

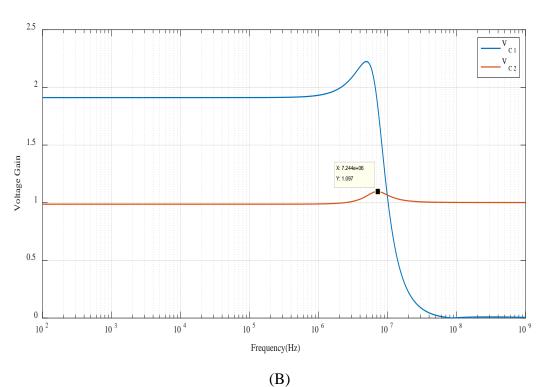

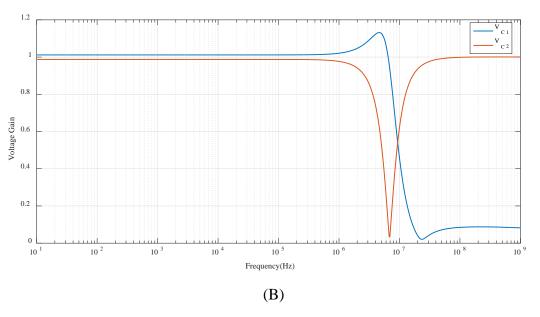

| Fig: 5.11 | Responses for voltage input $V_p = V_{in1}$                         | 88  |

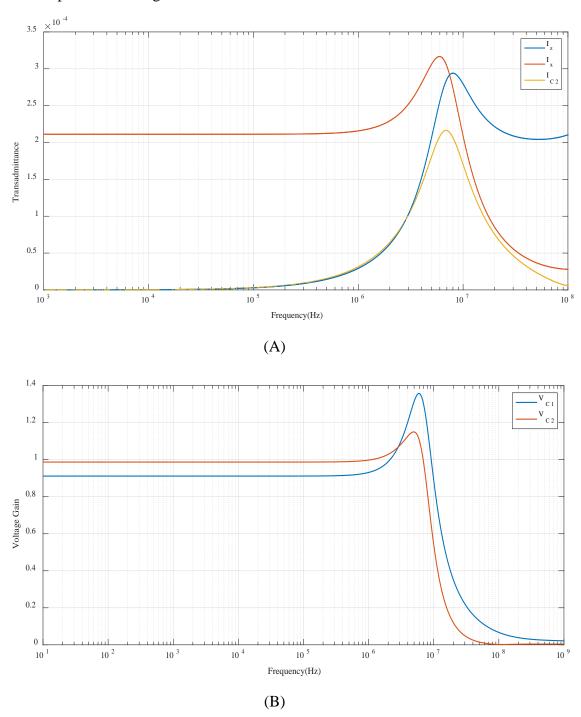

| Fig: 5.12 | Responses for voltage input $V_{in2}$                               | 89  |

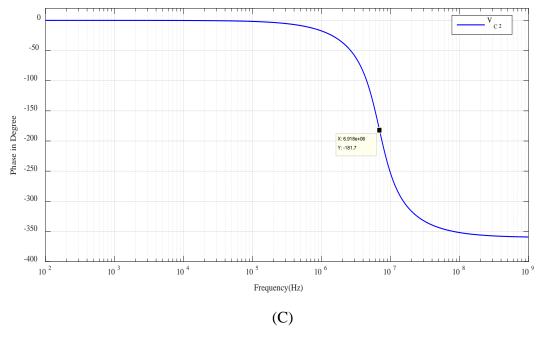

| Fig: 5.13 | Responses for voltage input $V_V = V_{in3}$                         | 90  |

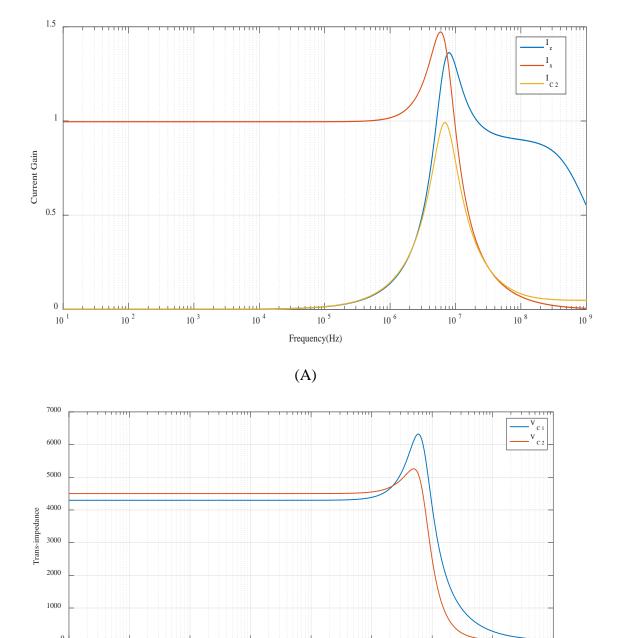

| Fig: 5.14 | Responses for voltage input $V_{in4}$                               | 91  |

| Fig: 5.15 | Responses for voltage input $V_{in1} + V_{in2}$                     | 92  |

| Fig: 5.16 | Responses for voltage input $V_{in1} + V_{in3}$                     | 93  |

| Fig: 5.17 | Responses for voltage input $V_{in1} + V_{in4}$                     | 94  |

| Fig: 5.18 | Responses for voltage input $V_{in2} + V_{in4}$                     | 95  |

| Fig: 5.19 | Responses for voltage input $V_{in3} + V_{in4}$                     | 96  |

| Fig: 5.20 | Responses for voltage input $V_{in1} + V_{in2} + V_{in3}$           | 97  |

| Fig: 5.21 | Responses for voltage input $V_{in1} + V_{in2} + V_{in4}$           | 98  |

| Fig: 5.22 | Responses for voltage input $V_{in2} + V_{in3} + V_{in4}$           | 100 |

| Fig: 5.23 | Responses for voltage input $V_{in1} + V_{in2} + V_{in3} + V_{in4}$ | 101 |

## **LIST OF TABLES**

| Table No. | Title                                                  | Page No. |

|-----------|--------------------------------------------------------|----------|

| Table 2.1 | Comparison of several CDTA structures                  | 9        |

| Table 2.2 | Comparison of various CM-SIMO universal filters        | 10       |

| Table 2.3 | Comparison of Various Grounded Inductor configurations |          |

|           | with the New Proposed Grounded Inductor                | 11       |

| Table 2.3 | Comparison of Various MM filter configurations with    |          |

|           | CD-DITA based Proposed MM filter                       | 12       |

| Table 3.1 | Aspect ratios of the transistors for CD-DITA based     |          |

|           | on FVF                                                 | 24       |

| Table 3.2 | Performance parameters of CDTA                         | 41       |

| Table 3.3 | Aspect ratios of MOS transistors used in CD-DITA       |          |

|           | Implementation                                         | 43       |

| Table5.1  | Filter responses for MM biquad filter                  | 101      |

## **LIST OF ABBREVIATIONS**

**Abbreviation** Full Form

IC Integrated Circuit

CMOS Complementary Metal Oxide Semiconductor

DSP Digital Signal Processing

ADC Analog to Digital Convertor

DAC Digital to Analog Convertor

DC Direct Current

AC Alternating Current

VLSI Very Large Scale Integration

CM Current Mode

VM Voltage Mode

MM Mixed Mode

Op-Amp Operational Amplifier

SR Slew Rate

ASP Analog Signal Processing

ABBs Active Building Blocks

MOS Metal Oxide Semiconductor

CC Current Conveyor

CCII 2<sup>nd</sup> generation Current Conveyor

CFOA Current Feedback Operational Amplifier

BJT Bipolar Junction Transistor

TA Transconductance Amplifier

LPF Low Pass Filter

BPF Band Pass Filter

HPF High Pass Filter

BRF Band Reject Filter

APF All Pass Filter

MIMO Multiple Input Multiple Output

SIMO Single Input Multiple Output

CDTA Current Differencing Transconductance Amplifier

CD-DITA Current Differencing Differential Input Transconductance Amplifier

VCCS Voltage Controlled Current Source

DVCCS Differential Voltage Controlled Current Source

DCCCS Differential Current Controlled Current Source

CDU Current Differencing Unit

FVF Flip Voltage Follower

OTA Operational Transconductance Amplifier

DO-OTA Dual Output OTA

FVFCS. Flip Voltage Follower Current Source

B.W Bandwidth

CDBA Current Differencing Buffered Amplifier

DDCC Differential Difference Current Conveyor

OTRA Operational Transresistance Amplifier

DVCC Differential Voltage Current Conveyor

DVCCII 2<sup>nd</sup> Generation Differential Voltage Current Conveyor

FBVDBA Full- Balanced Voltage Differencing Buffered Amplifier

TIM Trans Impedance Mode

TAM Trans Admittance Mode

CCCII 2<sup>nd</sup> generation Current Controlled Current Conveyor

CCCDTA Current Control CDTA

DDCC Differential Difference Current Conveyor

OTRA Operational Transresistance Amplifier

VD-DIBA Voltage Differencing – Differential input Buffered Amplifier

## **ABSTRACT**

CD-DITA based basic filtering applications such as first order APF and current mode SIMOtype universal biquad filter have been implemented and CD-DITA based grounded inductor and mixed mode filter have been proposed. CD-DITA is an extension of CDTA having extra voltage input than CDTA increasing its usability of differential inputs. For a suitable CMOS based implementation of CD-DITA, several CDTA realizations are studied and the suitable one is modified to implement the proposed CD-DITA block. A FVF based CD-DITA is characterized and its applications in analog signal processing circuits such as basic current amplifier, adder subtractor and integrator are also studied. The proposed CD-DITA based grounded inductor is realized with one resistors and one capacitor and further using proposed inductor band pass filter has been simulated. The proposed CD-DITA based mixed mode filter using two resistors and two capacitors with independent tuning of natural frequency and quality factor is simulated. The proposed filter also offers low active and passive sensitivities. In addition, the effects of parasitics and errors on the proposed filter are also investigated. The characteristics of CD-DITA and its applications are verified by PSPICE simulations using TSMC 0.25µm CMOS technology. The characteristics of CD-DITA and validity of proposed biquad filter is verified by SPICE simulation using TSMC 180nm technology.

#### Chapter 1

#### **Introduction**

The efficient and compact implementation of various types of digital and analog signal processing algorithms is possible on silicon chip due to the evolution of integrated circuit (IC) technology. Simulation of any block or function indigital domain has been easier due to the evolution of CMOS technology to lower technology nodes. Using CMOS technique,more efficient and smaller in size circuits can be designed.

Although the functions can be implemented and handled efficiently, digital signal processing (DSP) also faces some issues such as:

- Additional complexity: Every signal is analogue in nature. So Analog to Digital Converter (ADC) and Digital to Analog Converter (DAC) have to be used before processing any analogue information into digital. Also the reconstruction filters contribute to system complexity.

- Limited bandwidth: Wireless transmission of digital signals is not possible and transmission of digital signals for long distance using cables causes distortion and attenuation.

Hence repeaters should be used to regenerate these signals and thus bandwidth is limited for digital signals

- **Clock skew:** Clock skew is also called timing skew and occurs in synchronous digital circuits. It's a phenomenon in which the sourced clock will arrive at different times at different components in the same circuit, thus causing skew between any two clocks. Thus clock skew arises due to the distribution of a large amount of data and timing of clock over a large chip.

- **Trade-off:** A trade-off is there between operating frequency, power dissipation, cost, noise and level of the interferer.

However, there are many analogue domain functions for example signal rectification, signal amplification, conversion of signals from analog to digital and digital to analog, continuous time filtering that cannot be performed by digital circuits [1].

Hence to implement the above functions, analogue circuits holding high speed of operation with high precision are needed. As the technology is shifting to lower technology nodes,

analogue circuits should also attain features of low power dissipation and operate on low supplies [2].

#### 1.1 Development of technologies:

Since the establishment of the integrated circuits, the operational amplifiers (Op-Amp) have been used as the main and basic building block in analogue circuit design applications. Since then, new analogue applications have been found and the performance conditions for analogue circuits have been changed.

In Voltage mode (VM) Op-Amp blocks very high closed loop gains trade off with bandwidth is present. It means op-amp have limited bandwidth due to the constant gain-bandwidth product at high closed-loop gains. Further, op-amps also suffer from the limited slew rate that in turn affects the large signal operation and also high frequency operation.

When any application demands wide bandwidth, low-voltage and low power operations simultaneously, the VM op-amp becomes very complex and also their characteristics are not needed e.g. DC accuracy. Similarly on the other hand, the circuit techniques that are used in radio or high frequency applications are usually simple so that required accuracy can be achieved. Therefore there is always a growing need for new circuit techniques.

#### 1.2. Voltage and current mode signal processing:

Since the last two decades in VLSI design, the development of the latest analogue applications have been following the lead of the so called current mode techniques due to the advantages it offers over the VM. Any application is said to be processed in Current Mode (CM), when the information processed is in the form of currents instead of the conventional VM.

Another important advantage of CM over VM is use of the low supply voltages because the design of CM blocks deals with the processing of current signals that can be achieved with lower voltage swings .Also the mixed mode (MM) blocks are also synthesized and analyzed along with developing the CM blocks. From the literature survey its known that CM blocks or techniques always provide a large number of important analogue signal processing (ASP) and signal generator applications. Due to large growth in IC technology in last two decades, the

circuit designers have exploited the CM analogue techniques to provide the efficient solutions to many circuit design problems. As a result, the CM approach for many analogue signal processing applications offers many advantages like as

- High Operating Frequency Range.

- High Slew Rate(SR)

- High Precision

- Better Linearity

- Accuracy

- Low Power Dissipation.

While comparing VM and CM blocks, we should consider that here is no perfect or precise definition for any block to be current mode or voltage mode. Some authors say that signals are represented through currents in CM blocks and by voltages in VM blocks. But in every circuit a node has associated voltage and each branch has a current.

In spite of this, CM approach has a large impact on IC design. Our procedure is basically finding circuit realizations that are alternative of the exited circuits but are simple. So for this, the procedure is basically using current signals rather than voltage signals for signal processing applications.

#### 1.3. Motivation for CM design circuit:

One method for finding the substitute of these VM circuit techniques is to go for current signals instead of voltage signals for ASP. Circuits with MOS transistors are highly simplified with the usage of current signals for processing in-stead of voltage signals. Also CM integrated circuit realizations are more immediate to transistor level design than the conventional VM realizations and thus results in simpler systems and circuits. Where in the circuits, wide distribution of signals as voltages and the parasitic effects are more in the form of more capacitances which are discharged and charged with full dynamic voltage swing which results in limited speed and increase in dynamic consumption of power in VM circuits.

In CM circuits, it is difficult to avoid nodes having higher voltage swing but the positive side is these nodes usually come with relatively less parasitic capacitances [3]. Thus it results in higher speed and very low power dissipation.

When the current input signal is applied to a MOS transistor, the voltage developed will be directly proportional to square root of the input current, if all the transistors are assumed to be operating in saturation region. In the similar way, in BJT circuits voltage are logarithmic functions of input signal. Therefore, the voltage swing compression also results in reduction of voltage supply in CM blocks. This very feature is used in many applications such as log filters [4], switched current filters [5], and nonlinear applications of CM usually. But unfortunately, due to the result of mismatching of the devices, this nonlinearity can cause an enormous distortion for the applications which need high linearity specifications or conditions. Therefore, many CM circuits need to utilize more techniques to provide linearity in the circuits.

#### 1.4. Evolvement of CM blocks:

The very first building block meant for current signal processing was published in 1968 [6], and was named as current-conveyor (CC). And the enhanced version of the first generation of CC appeared in 1970 and named as the 2<sup>nd</sup>generation CCII [7] but due to the introduction of the integrated voltage mode operational amplifier none of these CC got popular at that time.

In 1980's, First fast pnp transistors were introduced in the bipolar ICs. In the mean while, the research institutes started noticing problems in the analogue design using the VM Op-Amp and hence it was not clearly the optimal solution to all analogue applications. New researches on CM signal processing with various applications using CC were presented. Furthermore, a new block was available i.e. Current Feedback Op-Amp (CFOA) [8]. The main advantages that CFOA offered over Op-Amp were high bandwidth and high SR due to which it gained popularity in video applications.

Mostly used CCs and the CFOAs relied on the complementary BJT technology. In order to realize the CM circuits with cheap circuit technologies, various kinds of circuit topologies and operational principles were needed. Therefore, in 1988 current mirror using MOS was presented [9].

The primary set of the active building blocks (ABBs) for analogue applications and signal processing applications is developing basically in two modes i.e. the first way that basic blocks that are already presented should be modified to new active blocks such as current mirrors, trans-conductance amplifiers (TA), CCs, voltage feedback amplifiers and also CFOA. The requirement for these modified blocks is that these should have simple structure so that high speed operation is achieved and also low power dissipation. The 2<sup>nd</sup> way is to characterize these ABBs with new elements.

For novel ABBs, some factors that one should seek are:

- Universality of ABB should be increased

- Electronic control of parameters

- Reduction or elimination of parasitics

- Design circuit application with minimum no. of ABBs and also minimum no of Passive components

- To find the solutions for trading off between the accuracy and speed

Current-differencing differential-input transconductance-amplifier (abbreviated CD-DITA) i.e. is an extension to Current-Differencing Transconductance-Amplifier (CDTA) is one among these ABBs. This block has been characterized by high output and low input impedances and thus making it suitable for the implementation of various ASP applications in CM. The universality of the CD-DITA block leads to the applications using less active and passive components and leading to simpler circuits.

#### 1.5. Objective:

In accordance with the above discussion, the work in this thesis has mainly concentrated its attention on the objectives that has to be achieved for CD-DITA and these objectives are given as:-

- Design of the CD-DITA block

- Development of CD-DITA block

- Design of various applications employing single CD-DITA block

Objectives of this thesis is to modify the existing applications and also to implement new applications such as realizing CD-DITA based proposed grounded inductor and employing its BPF application, implementing CD-DITA based CM universal filter of single-input multi-output (SIMO)-type configuration, implementing first order all pass filter (APF) using CD-DITA, designing and implementing one CD-DITA based proposed MM filter of multi-input multi-output (MIMO)-type configuration. To meet the objective of this work, the existing and the proposed designs have been simulated by using the PSPICE software in 0.250um TSMC technology node i.e. for grounded inductance simulation and 180nm TSMC technology node i.e. for filter applications. Also, the simulated results have been compared with the theoretical results.

#### 1.6. Organization of Thesis:

**Chapter 1:** Presents the brief introduction of the current mode signal processing in analogue circuit design. In this chapter the motivation for CM blocks and also the objective of the work in thesis have been discussed.

**Chapter 2:** A brief survey of both CDTA and CD-DITA literature and the survey of several grounded inductor circuits, CM biquad filter circuits employing CM ABBs and MM filter are presented.

**Chapter 3:** FVF based and Translinear Loop Based CD-DITA has been realized and its non-idealities are studied and simulated. It's DC and AC responses have been characterized and various performance parameters have been extracted through simulations.

**Chapter 4:** Some basic mathematical signal processing applications and filtering applications has been implemented using FVF based and TL based CD-DITA respectively.

**Chapter 5:** Proposed grounded inductor and CD-DITA based Proposed MM-MIMO filter has been implemented.

**Chapter 7:** This chapter presents summary of the work presented in this thesis and the future work has been discussed.

#### **Chapter 2**

#### **Literature Survey**

#### 2.1 Introduction:

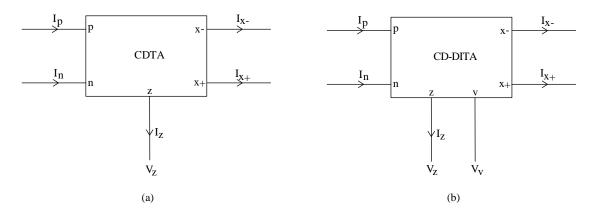

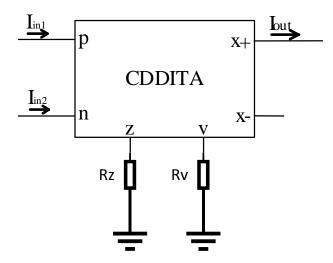

In the past few years, the CM analogue signal processing blocks have received a considerable amount of interest due to its advantages over VM blocks which have been explained briefly in this chapter. As a result of this CM analogue blocks have been emerged, CDTA and CD-DITA are among of these blocks. D. Biolek [10] . The basic block diagram of the CDTA and CD-DITA block is shown in Fig. 2.1(a)

Fig. 2.1 Block diagrams (a) CDTA (b) CD-DITA

CDTA can be seen as a cascading of current differencing unit (CDU) and an operational transconductance amplifier (OTA). CDTA has two low-impedance input terminals n and p, CDU takes the difference of the input signals and then transfer this difference to the intermediate terminal z, and this current is converted into voltage via external impedance connected at the z- terminal. This voltage is again converted back into balanced currents  $I_{x+}$  and  $I_{x-}$  at  $x \pm$  terminal with the gain of OTA i.e.  $g_m$ .

CDTA finds many applications in the circuits which are highly sensitive to the stray capacitances because CDTA have input terminals with low-impedance nodes. Thus this advantage makes CDTA a very useful and right choice for the high frequency applications.

CDTA block has been referred to as a true CM block in the literature because it is a current input and current output block.

CD-DITA is an improved version of CDTA. CD-DITA employs one differential-input OTA instead of using a single-input OTA which has been used in the traditional CDTA as shown in the Fig 2.1(b). This active element can provide various applications with advance features and characteristics such as employing minimum passive elements, providing the electronic tenability and controllability of various parameters like gain and quality factor and also realizing MM operation.

A very vast literature is offered on CDTA block which specifically includes realization of CDTA [11] using various techniques and a large variety of the CDTA based signal generation and processing applications [12-13]. However it is obvious from the literature survey, that the CD-DITA has found only single application, i.e. VM first-order APF presented in [14]. This work offers the development of CD-DITA block and its applications in CM and MM filtering area.

#### 2.2 Review of CD-DITA Implementations:

CD-DITA has been derived from CDTA with opening v terminal which was initially grounded; the basic internal circuitry of CD-DITA remains same as of CDTA except the v terminal. So, let's proceed with the review of the Wide-ranging literature of CDTA which suggests that the both bipolar [11], and CMOS [12-13] technologies have been used for implementing CDTA block.

CDTA realization using bipolar technology is presented in [17]. The advantages of BJT based CDTA is its large overall gain when compared to the CMOS based implementations.BJT based CDTA suffers from high power dissipation due to the leakages in BJT.

CMOS technology based CDTA structures have also been presented in the literature [18]. These circuits hold an advantage of very high impedance at z -terminal. A low power CMOS realization of CDTA has been presented in [19]. In this structure, flipped voltage follower (FVF) has been used to construct the input stages, because FVF based CDTA offers very low resistances at input terminals. One more CMOS based CDTA structure is given in [20]. This structure exhibits very low impedance at the inputs and high output impedance (typically in  $G\Omega$ ).

A comparison of all the available CDTA structures in terms of technology, supply voltage, gain and number of transistors, terminal impedances and power dissipation is shown in the table 2.1 Table 2.1 Comparison of several CDTA structures

| Ref  | Technology<br>used | Supply<br>Voltage | Bias current | Transconductance gain (g <sub>m</sub> ) | Power dissipation | Impedances<br>at p, n and<br>z |

|------|--------------------|-------------------|--------------|-----------------------------------------|-------------------|--------------------------------|

| [11] | Bipolar            | ±3V               | 100 μΑ       | 2 mS                                    | -                 | -                              |

| [17] | Bipolar            | ±2.5V             | 50 μΑ        | 0.96 mS                                 | -                 | -                              |

| [22] | Bipolar            | ±1.5V             | 100 μΑ       | -                                       | 8.11 mW           |                                |

| [18] | 0.25 μ<br>CMOS     | ±1.2V             | 150 μΑ       | 624.9 μS                                | -                 | -                              |

| [19] | 0.35 μ<br>CMOS     | ±0.75V            | 54 μΑ        | 210 μS                                  | 0.37 mW           | -                              |

| [23] | 0.35 μ<br>CMOS     | ±1.5V             | 100 μΑ       | 673 μS                                  | 3.61 mW           | 812 Ω, 348<br>Ω, 1.08 ΜΩ       |

| [20] | 0.5 μ<br>CMOS      | ±2.5V             | 125 μΑ       | 670 μS                                  | 1.4 mW            | 654 Ω, 506<br>Ω, 1GΩ           |

#### 2.3 Review of CM universal filters:

Analogue active filter is commonly used block for ASP. This block finds various applications in many fields, such as control systems, wireless communications and instrumentation signal measurement [25]. The synthesis and design of the analogue active filter circuits using electronically controllable blocks i.e. ABBs, taking several measures into account, for example minimum number of the active and passive elements used for implementing any circuit or others, has been receiving significant attention now a days.

Such ABBs provides convenience, versatility, flexibility for analogue circuit designer. Recently, the filters namely the universal or multifunction biquadratic filters, that can perform several functions using only single topology have been receiving significant attention from designers. The most popular universal analogue filters topology among all these filter topologies is a SIMO type CM filters. By simply just applying one current input signal, basic

filter applications such as LPF, BPF and HPF can be realized simultaneously and then by connecting various current outputs the remaining two filter functions such as BRF and APF can be realized simultaneously.

Many universal biquadratic filter configurations employing different ABBs, holding CM-SIMO type topology, have been designed and also implemented in past two decades. The main comparison of various active blocks is given in table 2.2. The CD-DITA based CM-SIMO filter is also compared with these filters and its advantages and disadvantages are also discussed in the coming chapters.

Table 2.2 Comparison of various CM-SIMO universal filters

| Reference | No. of | No. of    | No. of     | Electronic | All 5 filter |

|-----------|--------|-----------|------------|------------|--------------|

|           | ABBs   | Resistors | Capacitors | Tunability | responses    |

|           |        | used      | Used       |            | realized     |

| [26]      | 1      | 4         | 2          | NO         | NO           |

| [27]      | 1      | 4         | 3          | NO         | NO           |

| [28]      | 1      | 2         | 2          | NO         | NO           |

| [29]      | 1      | 2         | 2          | NO         | NO           |

| [17]      | 1      | 1         | 2          | YES        | NO           |

| [30]      | 1      | 1         | 2          | YES        | NO           |

| [31]      | 1      | 3         | 2          | NO         | YES          |

| [32]      | 1      | 2         | 2          | YES        | YES          |

| CD-DITA   | 1      | 1         | 2          | YES        | YES          |

#### 2.4 Review of Grounded Inductor Simulations:-

In the network synthesis using active element to replace the actual bulky inductor there is a huge demand of grounded simulated inductor [33]. Several active elements to simulate grounded inductance such as op-amps [34], CCs [35], CCCIIs [36], CFOAs [37], DVCCIIs [38], CDTAs [39], DVCCs [40] have been reported in the vast literature and in this work a new grounded inductor has been simulated using CD-DITA.

In the table given below the comparison of various grounded inductor configurations with the proposed Grounded Inductor based on CD-DITA has been presented.

Table 2.3:- Comparison of Various Grounded Inductor configurations with the New Proposed Grounded Inductor

| Ref.     | No. of Active elements | No. of resistors | No. of capacitors | Requirement of Matching | Electronic tunability |

|----------|------------------------|------------------|-------------------|-------------------------|-----------------------|

|          | used                   | used             | used              | condition               | availability          |

| [41]     | 1                      | 2                | 1                 | YES                     | NO                    |

| [36]     | 2                      | 0                | 1                 | NO                      | NO                    |

| [37]     | 2                      | 2                | 1                 | NO                      | NO                    |

| [38]     | 3                      | 4                | 1                 | NO                      | NO                    |

| [39]     | 2                      | 0                | 1                 | NO                      | YES                   |

| [40]     | 2                      | 0                | 1                 | NO                      | YES                   |

| [42]     | 2                      | 0                | 1                 | NO                      | YES                   |

| [43]     | 3                      | 3                | 1                 | NO                      | NO                    |

| Proposed | 1                      | 1                | 1                 | NO                      | YES                   |

#### 2.5 **Review of MM filters:**

In analogue signal processing applications it may be desirable to have active filters with input currents and/or voltages and output currents and/or voltages, that is mixed-mode filters. [55] Careful inspection of the available literature shows that the mixed-mode realizations with input current and output voltage and with input voltage and output current are available but limited circuit realization is available for realizing a generalized mixed-mode active filter with input current or voltage and output current or voltage. In recent past, mixed-mode filter circuits have been extensively studied and researched in open literature with renewed interest and hence, several mixed-mode filter circuits using different current-mode active elements such as CCII[56], FDCII[57], CCCII[58], OTAs [59]. However, these circuits employ too many active

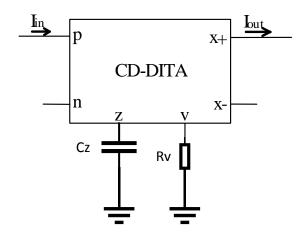

and passive elements in filter realization. Besides it, few of the circuits don't offer the current tunability feature of filter characteristic parameters too. As far as the topic of this paper is concerned, the mixedmode filter circuits using single active element are of great interest, because circuits employing minimum active components are more beneficial in terms of power dissipation and manufacturing cost point of view and also satisfy the supply related specifications of portable battery operated electronic gadgets. In this work mixed-mode filter employing single CD-DITA as active element and two capacitors, two resistors has been designed and implemented using 180nm TSMC parameters. Table2.4 for comparison of various MM filter configuration with the proposed MM filter can be given as:

Table 2.4: Comparison of Various MM filter configurations with CD-DITA based Proposed MM filter

| Ref.                        | [56]  | [59]         | [58]             | [57]             | Proposed        |

|-----------------------------|-------|--------------|------------------|------------------|-----------------|

| Active element              | CCII  | OTA          | CCCII            | FDCII            | CD-DITA         |

| No. of Active elements used | 6     | 5            | 2                | 1                | 1               |

| Passive elements            | 10    | 2            | 2                | 5                | 4               |

| Electronic tenability       | NO    | YES          | YES              | NO               | YES             |

| Supply(V)                   | ± 2.5 | ±1.65        | ± 2.5            | ±12.5            | ±.9             |

| Pole Frequency $(\omega_n)$ | .5MHz | 1 <i>MHz</i> | 638.5 <i>KHz</i> | 3.789 <i>MHz</i> | 6.97 <i>MHz</i> |

| Universality of filter      | YES   | YES          | NO               | NO               | NO              |

## Chapter 3

### **Realization of CD-DITA**

#### 3.1Introduction:

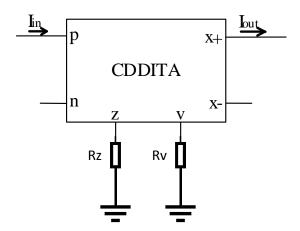

Current-differencing differential-input transconductance amplifier i.e. CD-DITA is one of the CM ABBs used for designing and implementing analogue circuits. In addition to the traditionally used op-amps, CD-DITA block not only supports VM but also supports CM and also the multi-mode or mixed mode operation. CD-DITA is growing as a flexible, versatile and universal ABB for analogue signal processing applications. Its profitable features and its usefulness have been renowned from [10] on active elements. The ideal and non-ideal analysis of CD-DITA can be summarized as following:-

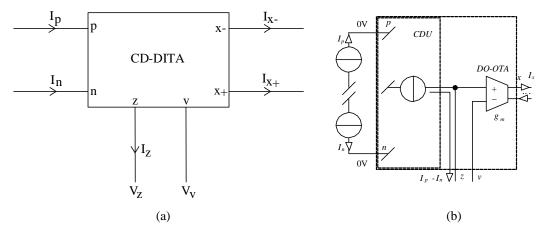

#### 3.1.1. Ideal CD-DITA:

CD-DITA block is a new active block, having six terminals with electronic control. The circuit symbol of CD-DITA and the behavioral model of CD-DITA [10] are presented in the Fig. 3.1(a) and (b), respectively. CD-DITA has two current input terminals and they are having low-impedance and ideally zero current input terminals i.e. p and n, and the remaining four terminals are high-impedance terminals i.e. ideally infinite impedance terminals. Out of these four terminals, two terminals are intermediate terminals that are specifically known as the current output terminal z and the input voltage terminal v and then the remaining two terminals are current output terminals i.e. x + and x -.

Fig. 3.1 CD-DITA (a) Schematic symbol and (b) Behavioral model[10]

The CD-DITA behavioral model includes two stages, which are basically controlled sources and these two stages are differential current-controlled current-source i.e. DCCCS with current gain unity, and differential voltage controlled current source i.e. DVCCS i.e. OTA with the transconductance gain. The input stage of CD-DITA can be realized by using a differential input single- out-put current differencing unit i.e. CDU, CDU basically produces the difference of the in-put currents  $I_p$  and  $I_n$  that are intended to further flow through the output terminal i.e. z terminal. There will be an appropriate voltage drop produced at the z terminal by the differential current i.e.  $I_z$  and the voltage drop that is produced will be according to any external load impedance is connected at the z terminal.

The output stage of the CDDITA block has been implemented by using a differential input and dual output OTA i.e. DO-OTA. The z output terminal of the CD-DITA block has also been internally connected to the non-inverting input terminal of the DO-OTA section. The terminal v has been brought out as the voltage input terminal of the CD-DITA block that is connected to the inverting input terminal of the DO-OTA section. The voltage difference at the input terminals of the DO-OTA section i.e. between the z and v terminals of the DO-OTA has been transformed though the DO-OTA's gain i.e. transconductance gain  $s_m$  into the output currents i.e.  $s_m$  intended to flow through the current output terminals of the CD-DITA block i.e.  $s_m$  and  $s_m$  intended to flow in the opposite directions but these currents  $s_m$  and  $s_m$  will be equal in magnitude. The gain of DO-OTA can be electronically controlled using the bias currents. The relationship between the inputs and the outputs terminals of the CD-DITA block can be shown by using the following terminal equations:

$$V_p = V_n = 0 (3.1)$$

$$I_{v} = 0 \tag{3.2}$$

$$I_z = I_p - I_n \tag{3.3}$$

$$I_{x+} = g_m(V_z - V_v) (3.4)$$

$$I_{v_{-}} = -g_{m}(V_{z} - V_{v}) \tag{3.5}$$

Therefore, Equation matrix of CD-DITA block has been given as

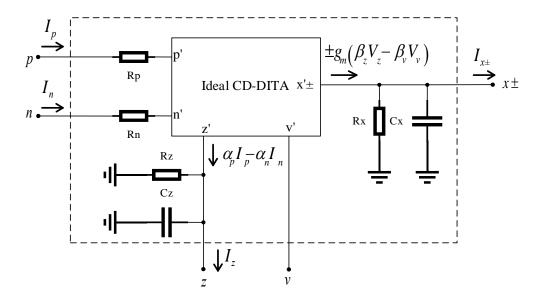

#### 3.1.2 Non ideal CD-DITA:-

In this section, the non-ideal CD-DITA block has been explained briefly. As presented in the Fig. 3.2, non-ideal equivalent schematic symbol of the CD-DITA has been observed to be very similar to the CDTA block, except than the addition of the error in the transconductance transfer  $\beta_{\nu}$  which is due to the terminal  $\nu$  that has been always kept grounded in the case of CDTA block but in CD-DITA block it has been brought as the external extra voltage input terminal. The errors from the z and the  $\nu$  terminals are defined by the following equations:-

$$\beta_z = 1 - \varepsilon_z; \beta_v = 1 - \varepsilon_v \text{ and } |\varepsilon_z| << 1; |\varepsilon_v| << 1$$

(3.7)

Fig. 3.2 Non ideal CD-DITA

Where  $\varepsilon_z$  is transconductance tracking error from the terminal z to the terminal  $x \pm z$

And  $\mathcal{E}_{\nu}$  is transconductance tracking error from the terminal  $\nu$  to the terminal  $x \pm 1$

In the non-ideal case, the terminal equations of the CD-DITA are slightly modified and given as follows:-

$$V_p = 0 (3.8)$$

$$V_n = 0 (3.9)$$

$$I_z = \alpha_p I_p - \alpha_n I_n \tag{3.10}$$

$$I_{x+} = +g_m \left(\beta_z V_z - \beta_v V_v\right) \tag{3.11}$$

$$I_{x-} = -g_m (\beta_z V_z - \beta_v V_v)$$

(3.12)

Therefore, the Non-ideal CD-DITA block in the absence of various parasitics is presented by the following equations matrix:-

#### 3.2 Realization of Flipped Voltage Follower(FVF) based CDDITA:-

#### 3.2.1 Flipped voltage follower:-

In Fig. 3.3(a), a simple MOS based Common drain (CD) amplifier is shown; CD amplifier is commonly used circuit in most of the ASP applications due to the voltage buffering operation of this amplifier.

If we consider that the body effect of transistor  $M_1$  is ignored, then with this assumption it has been observed that the output voltage signal of the CD amplifier circuit follows the input voltage signal with a dc level shift of  $V_{GS}$  of transistor  $M_1$

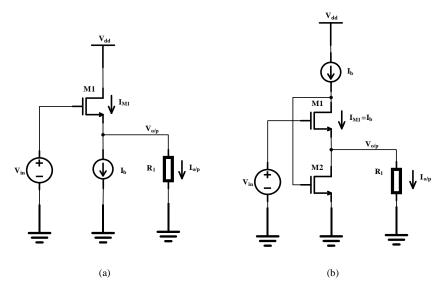

Fig. 3.3(a) CD amplifier or Source Follower, (b) Flipped Voltage Follower (FVF)

Thus the relation between the i/p and o/p voltages signals can be expressed as the following equation:-

$$V_{out} = V_{in} - V_{GS} \tag{3.14}$$

The DC analysis of the circuit in figure (a) shows some major drawbacks that are:

- The sinking capability of this circuit to load is large i.e. source follower can sink large amount

of current to the load, but biasing current i.e. I<sub>b</sub> is limiting the sourcing capability from output

node.

- One more drawback of CD amplifier is the dependence of its o/p current  $I_{out}$  on the current through the transistor  $M_1$  i.e.  $I_{M1}$ , such that if we vary transistor current then there is corresponding variation in its  $V_{GS}$  and, thus the voltage gain also changes resulting variable voltage gain i.e. not constant.

- Due to the DC shift, voltage gain of this circuit is also less than unity.

- If the loads are capacitive then also similar type of limitations exists in the circuit but at relatively higher frequencies.

The o/p impedance of source follower circuit is given as:

$$r_{out} = \frac{1}{g_m} \tag{3.15}$$

Where  $g_m$  is the transconductance of  $M_1$ . The typical value of  $r_{out}$  ranges from  $1k\Omega \cos k\Omega$ . In Fig. 3.4(b), the circuit shown is a negative-shunt-feedback amplifier which also acts as the source follower. Here in this circuit the usage of transistor  $M_1$  is to buffer signals from i/p to o/p. This circuit offers some major advantages over the conventional source follower circuit and these are as follows:

- Here in this circuit, current through transistor  $M_1$  i.e.  $I_{M1}$  is always constant with the help of bias current  $I_b$ , thus making  $I_{M1}$  independent of any variations in the o/p current  $I_{out}$ .

- Hence  $I_{M1}$  is always constant, thus  $V_{GS}$  of  $M_1$  also remains constant.

- In this circuit the variations in output current i.e.  $I_{out}$  have been absorbed by the transistor  $M_1$  which is nothing but a current sensing transistor. Thus as a result, the variations in the output voltage remains low even at the higher frequencies.

- This circuit provides the output node with very small value of the output impedance because of the *M*, transistor.

- FVF can source large amount of currents due to its low output impedance [44]

$M_2$  transistor provides the shunt feedback to the circuit. The bias current source  $I_b$  is connected to the drain terminal of transistor  $M_1$  instead of the source terminal, due to which this particular circuit has been named as the flipped voltage follower i.e. (FVF).

The o/p impedance of Flip Voltage follower circuit is given as:-

$$r_{out} = \frac{1}{g_{m1}g_{m2}r_{o1}} \tag{3.16}$$

Where  $r_{o1}$  is the output resistance of transistor  $M_1$  and  $g_{m1}$ ,  $g_{m2}$  are transconductance of transistors  $M_1$  and  $M_2$  respectively. The typical value of  $r_{out}$  ranges from  $10\Omega$  to  $100\Omega$ .

#### 3.2.2 Current Mirror based on FVF:

Considering FVF circuit, the output node of FVF follower circuit can be used as the current input node because at the output node of this circuit very low value of the impedance is shown

as is required in the current mirror. Therefore, this modified FVF, called as a current sensing cell, also named as FVF current sensor i.e. (FVFCS). In Fig. 3.5.One such circuit is shown:-

Fig. 3.4 Current Mirror based on FVF

In the above circuit, node B acts as i/p current sensing node because it's having low impedance and the negative shunt feedback is provided by transistor  $M_2$ . The variations in the input current signal at the node B will be transformed to the corresponding voltage variations at the node A. Transistor  $M_3$  is used to form a current mirror i.e.  $M_3$  produces the copy of the i/p current signal utilizing the variations at the node A. The i/p and the output current signals are related through the following expression:

$$I_{out} = I_{in} + I_b \tag{3.17}$$

The bias current  $I_b$  in the above expression can be easily eliminated by employing the current mirroring techniques.

The voltage levels required at the node A to keep both the transistors i.e.  $M_2$  and  $M_3$  are just  $V_{DSsat}$ , that is smaller than the voltage levels required for the traditional low-voltage current mirrors.

The impedance of this mirror at the input node A is very low i.e. ranging from  $10\Omega$  to  $100\Omega$  and the minimum level of voltage supply required at the node A is expressed as the following:-

$$V_{dd\,(\text{min})} = 2V_{DSsat} - V_t. \tag{3.18}$$

Thus FVF based current mirror has very low power supply requirements.

# 3.2.3 Current differencing unit:-

CDU can be realized using FVFCS [45] as shown in figure 3.5. In this CDU transistors from  $M_1$ - $M_3$  and  $M_4$ - $M_6$  are forming two consecutive FVF based current-mirrors and also transistor pairs  $M_7$  and  $M_8$  are used to realize the simple current-mirror. To bias the both FVF based current mirrors same bias current i.e.  $I_{b1}$  is used, due to which the currents through  $M_1$  and  $M_6$  transistors will be equal to the biasing current i.e.  $I_{b1}$ .

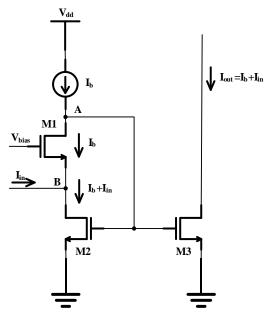

Fig. 3.5 CDU based on FVF

The input currents i.e.  $I_p$  and  $I_n$  have been applied at the current input terminals i.e. p and n of the CDU respectively. Thus the resulting currents flowing through the transistors  $M_2$  and  $M_5$  can be expressed by the following expressions:-

$$I_{M2} = I_p + I_{b1} (3.19)$$

$$I_{M5} = I_n + I_{b1} (3.20)$$

The currents flowing through the transistors  $M_2$  and  $M_5$  will be exactly mirrored into the transistors  $M_3$  and  $M_4$  because of the current mirror respectively. The current flowing through the transistor  $M_3$  will be further mirrored into the transistor  $M_8$  due to the usage of a simple current mirroring circuit. Thus, the resulting currents flowing through the transistors  $M_8$  and  $M_4$  can be expressed as the following expressions:-

$$I_{M8} = I_p + I_{b1} (3.21)$$

$$I_{M4} = I_n + I_{b1} (3.22)$$

In CDU unit, the z terminal has been considered as the current output and the difference of the currents flowing through the transistors  $M_8$  and  $M_4$  will be either sourced by the z terminal or sunk by the z terminal and hence this expressions of current flowing through the z terminal can be expressed as following:-

$$I_z = I_p - I_n \tag{3.23}$$

From the above expression it becomes clear that the current differencing operation has been realized by the z terminal of CDU unit. In CD-DITA, if some external impedance is connected at the z terminal of CDU, then the corresponding current though the z terminal i.e.  $I_z$  will be converted into the corresponding voltage  $\text{drop} V_z$  at the z terminal. The z terminal acts as one of the voltage input nodes for DO-OTA and hence the voltage drop i.e. at the z terminal i.e.  $V_z$  can be used as one of the inputs of the DO-OTA section of the CD-DITA.

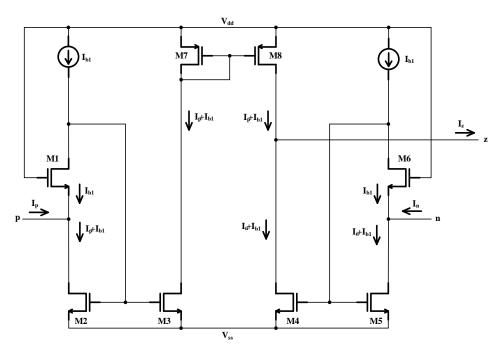

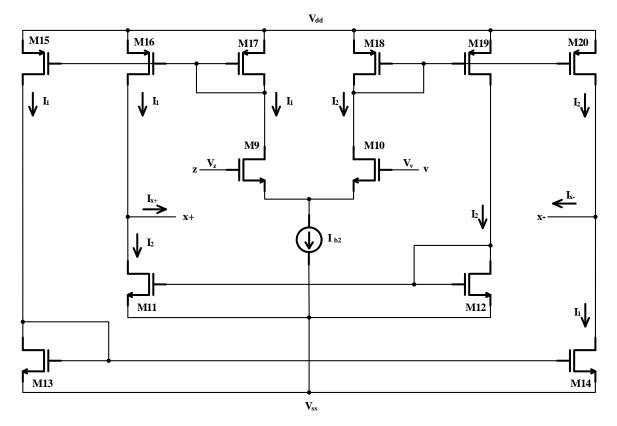

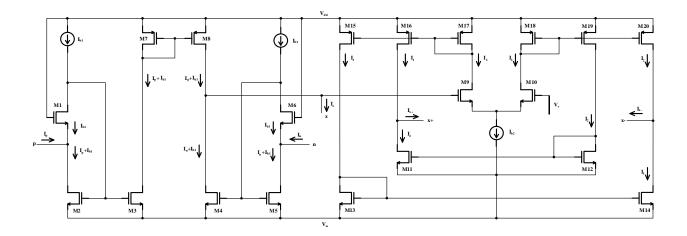

# 3.2.4 Dual output OTA (DO-OTA):-

As presented in the Figure. 3.6, the DO-OTA section of the CD-DITA block has been realized by using a differential pair amplifier formed using a transistor pair consisting transistors  $M_9$  and  $M_{10}$ . Transistors  $M_9$  and  $M_{10}$  have been biased using the biasing current i.e.  $I_{b2}$  and for the purpose of obtaining the dual output current i.e.  $I_x \pm$ , few simple current mirror circuits based on the NMOS and PMOS have been used.

Fig. 3.6 DO-OTA [46]

The input voltage signals i.e.  $V_z$  and  $V_v$  have been applied at input voltage terminals i.e. the z terminal and the v terminal respectively. The input voltages at these input terminals i.e. at z terminal and v terminal will produce the corresponding currents i.e.  $I_1$  and  $I_2$  flowing through the transistor  $M_g$  and the transistor  $M_{10}$  respectively. Here when the current  $I_1$  i.e. flowing through the transistor  $M_g$  has been mirrored using the transistor pair  $M_{16}$  and  $M_{17}$  and also when the current  $I_2$  i.e. flowing through the transistor  $M_{10}$  has been mirrored using the transistor pairs i.e.  $M_{11}, M_{12}, M_{18}$  and  $M_{19}$ . Thus by mirroring the currents  $I_1$  and  $I_2$  according to the above configurations, then output of the DO-OTA achieved at an output terminal v will be a positive difference of the currents v and v are terminal of the DO-OTA can be expressed as following:-

$$I_{x+} = I_1 - I_2 \tag{3.23}$$

Here when the current  $I_1$  i.e. flowing through the transistor  $M_9$  has been mirrored using the transistor pairs  $M_{13}$ ,  $M_{14}$ ,  $M_{15}$  and  $M_{17}$ , and also when the current  $I_2$  i.e. flowing through the

transistor  $M_{10}$  has been mirrored using the transistor pairs i.e.  $M_{18}$  and  $M_{20}$ . Thus by mirroring the currents  $I_1$  and  $I_2$  according to the above configurations, then the output of the DO-OTA achieved at an output terminal x- will be a negative difference of the currents  $I_1$  and  $I_2$ . Thus the current flowing through the x+terminal of the DO-OTA can be expressed as following:-

$$I_{r-} = -(I_1 - I_2) \tag{3.24}$$

Thus when the differential input voltage i.e.  $(V_z - V_v)$  has been applied at the input of the DO-OTA then the dual output current signals i.e.  $I_x \pm \text{can}$  be achieved. The expressions for the output currents of the DO-OTA section can be given as the following:-

$$I_{x+} = \pm (I_1 - I_2) = \pm g_m (V_z - V_v)$$

(3.25)

Where  $g_m$  is the transconductance gain of the DO-OTA section and this transconductance gain of the DO-OTA can be controlled by the biasing current i.e.  $I_{b2}$ . The transconductance gain of the DO-OTA i.e.  $g_m$  can be given as the following expression:-

$$g_{m} = \sqrt{I_{b2} \left[ \mu_{n} C_{ox} \left( \frac{W}{L} \right) \right]_{M_{9}, M_{10}}}$$

(3.26)

Where the parameters  $\frac{W}{L}$ ,  $\mu_n$  and  $C_{ox}$  are of the differential pair transistors i.e. of the transistors  $M_9$  or  $M_{10}$ . And  $g_m$  i.e. the transconductance gain of the DO-OTA can be varied by varying the bias current  $I_{b2}$ .

To realize the CD-DITA block, DO-OTA section has been clubbed with the CDU section and in the CD-DITA block the one of the voltage input terminal i.e. z terminal of DO-OTA section has been driven by the current output terminal i.e. z terminal of CDU section and the second input voltage terminals i.e. v terminal of the DO-OTA section is connected to some external input voltage signal. Depending upon the application requirement the connections to this v terminal of the DO-OTA can be made.

The complete schematic diagram of the CD-DITA block based on the FVF is presented in the Fig. 3.7:-

Fig. 3.7 CD-DITA based on FVF

In the above figure 3.7CD-DITA based on FVF consists of the CDU section followed by the DO-OTA section. And the aspect ratios of the transistors used to implement the realization of the CD-DITA block has been listed in the table 3.1 given below:-

Table 3.1 Aspect ratios of the transistors for CD-DITA based on FVF:

| Transistors       | W in (µm) | L in (µm) |

|-------------------|-----------|-----------|

| $M_1 - M_8$       | 24        | 1         |

| $M_9, M_{10}$     | 8         | 1         |

| $M_{11} - M_{14}$ | 5         | 1         |

| $M_{15} - M_{20}$ | 8         | 1         |

# 3.3 Characterization of CD-DITA:-

The CMOS implementation of the CD-DITA block based on FVF has been presented in the Fig 3.7. The CMOS implementation of the CD-DITA block has been simulated using the PSPICE simulations and also using the 0.25um technology mode i.e. 0.25um process parameter. And the power supply rails that are used are  $\pm 1.2V$ . This CD-DITA block characterization for both the large signal behavior i.e. the DC response of the CD-DITA block and for the small signal

behavior i.e. the Frequency response the CD-DITA block is given in the coming sections of this work:

### 3.3.1 DC characteristics or Large signal analysis:-

#### 3.3.1.1 DC characteristics of CDU Section:-

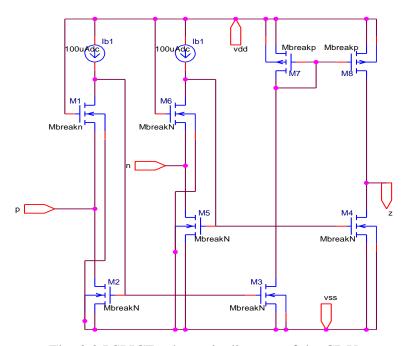

Fig. 3.8 PSPICE schematic diagram of the CDU

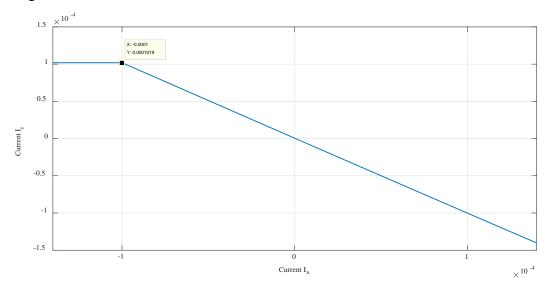

The PSPICE schematic diagram of the CDU Section of the CD-DITA block has been presented in the Fig. 3.8. the current that is used to bias the CDU section i.e.  $I_{b1}$  has been chosen as  $100\mu$ A. To verify the linear range of the ouput current when input currents are varied i.e. the dynamic range of the input currents at the current input terminal p and also along with the verification of the current tracking from p terminal to the z terminal.

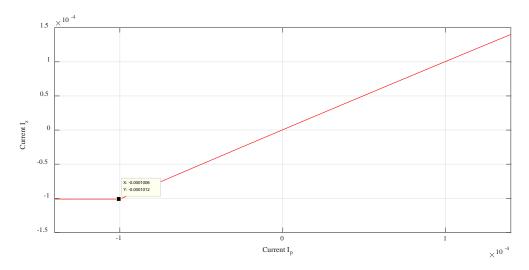

The DC analysis of the output current of the CDU vs. one of the input current signal provided the other input signal is zero i.e.  $I_z$  vs.  $I_p$  with the condition of  $I_n = 0$  has been plotted and To obtain this plot the current at p terminal i.e.  $I_p$  been varied from  $-150\mu$ A to  $150\mu$ A and presented in the Fig. 3.9

Fig. 3.9. Current transfer from the p-terminal to the z-terminal ( $I_z$  vs.  $I_p$ ) with the condition  $I_p = 0$

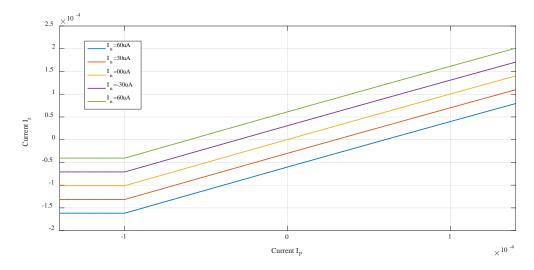

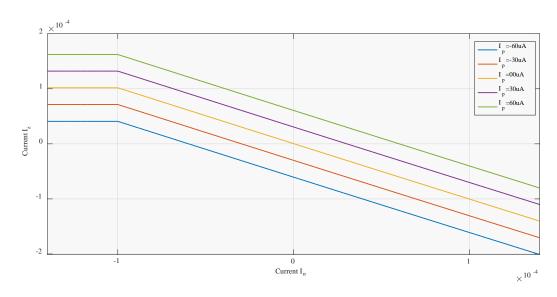

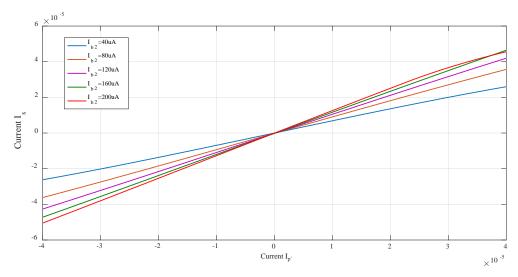

The DC analysis curves that are presented in the Fig. 3.10 show the effect of the variation of the current at the n terminal current i.e.  $I_n$  on the plot of  $I_z$  vs.  $I_p$ . To obtain this plot the current at p terminal i.e.  $I_p$  been varied from  $-150\mu A$  to  $150\mu A$  along with the parametric sweep of  $I_n$  that is ranging from the value of  $-60\mu A$  to  $60\mu A$  using interval value of  $30\mu A$ .

Fig. 3.10 Current transfer from the p-terminal to the z-terminal ( $I_z$  vs.  $I_p$ ) with parametric sweep on  $I_n$

To verify the linear range of the ouput current when input currents are varied i.e. the dynamic range of the input currents at the current input terminal n and also along with the verification of the current tracking from n terminal to the z terminal.

The DC analysis of the output current of the CDU vs one of the input current signal provided the other input signal is zero i.e.  $I_z$  vs  $I_n$  with the condition of  $I_p = 0$  has been plotted and To obtain this plot the current at n terminal i.e.  $I_n$  been varied from  $-150\mu A$  to  $150\mu A$  and presented in the Fig. 3.11.

Fig. 3.11. Current transfer from the *n*-terminal to the *z*-terminal ( $I_z$  vs  $I_n$ ) with the condition  $I_n = 0$

The DC analysis curves that are presented in the Fig. 3.12, show the effect of the variation of the current at the p terminal current i.e.  $I_p$  on the plot of  $I_z$  vs  $I_n$  To obtain this plot the current at n terminal i.e.  $I_n$  been varied from  $-150\mu A ag{to}150\mu A$  along with the parametric sweep of  $I_p$  that is ranging from the value of  $-60\mu A$  to  $60\mu A$  using interval value of  $30\mu A$ .

From the DC analysis of the of CDU conducted using the PSPICE simulations, it has been concluded that the input vs output characteristics of the CDU section will remain in linear range for the input dynamic range of  $-100\mu A to 100\mu A$  this can also be theoretically verified by the bias current  $I_{b1}$  that tends to limit the dynamic range of CDU section.

Fig. 3.12 Current transfer from the n-terminal to the z-terminal ( $I_z vs I_n$ ) with parametric sweep on  $I_p$

## 3.3.1.2 DC characteristics of DO-OTA Section:-

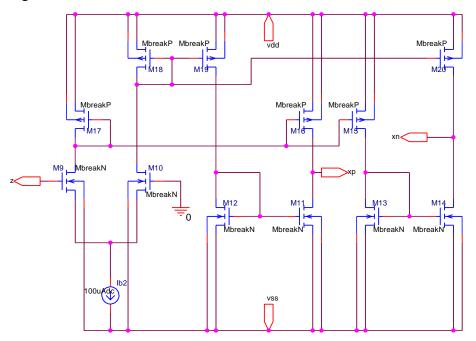

The PSPICE schematic diagram of the DO-OTA Section of the CD-DITA block has been presented in the Fig. 3.13.

Fig. 3.13 PSPICE schematic diagram of the DO-OTA

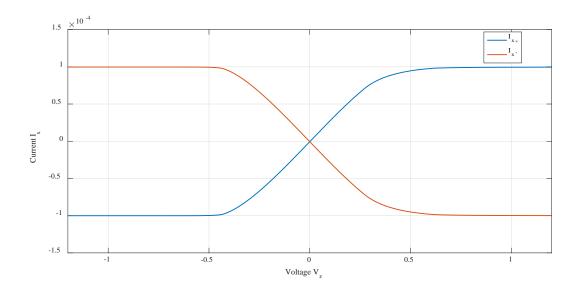

The current that has been used to bias the DO-OTA section i.e.  $I_{b2}$  has been chosen as  $100\mu$ A To verify the linear range of the output current when input voltages are varied i.e. the voltage dynamic range of the input voltage at the voltage input terminal z and also along with the verification of the of transconductance transfer from the input terminal i.e. the z terminal to the output current terminals i.e. the  $x\pm$  terminals , DC analysis is achieved by varying the input voltage at the input z terminal i.e.  $V_z$  from -1.2V to 1.2V and the resulting plot i.e. of output current vs. input voltage by keeping the other voltage terminal grounded i.e.  $I_{x\pm}$  vs.  $V_z$  with the condition of  $V_v = 0V$  has been presented in the Fig. 3.14.

Fig. 3.14 Transconductance transfer from the z-terminal to the  $x \pm$  terminal ( $I_{x\pm}$  vs  $V_z$ ) with  $I_{h2} = 100 \mu A$

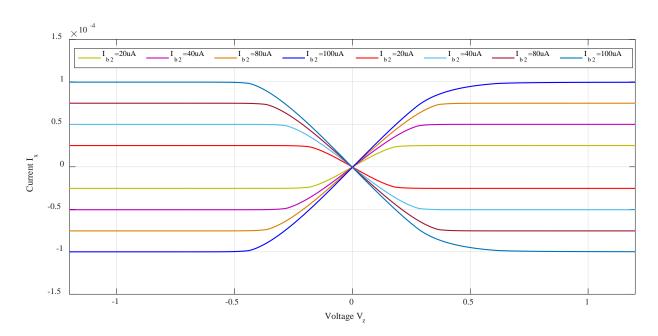

The effect of the variation of the bias current  $I_{b2}$  on the output current vs input voltage curves i.e.  $I_{x\pm} \, {\rm vs} \, V_z$  plot has been presented in Fig. 3.15. To achieve these DC curves, the input voltage of the DO-OTA section i.e.  $V_z$  has been varied from the  $-1.2V \, {\rm to} \, 1.2V$  along with the parametric sweep applied on biasing current i.e. on  $I_{b2}$  with the values  $25 \, \mu A$ ,  $50 \, \mu A$ ,  $75 \, \mu A$  and  $100 \, \mu A$ .

Fig. 3.15. Transconductance transfer from the z-terminal to the  $x \pm$  terminals ( $I_{x\pm}$  vs  $V_z$ ) with  $I_{b2}$  as parametric sweep

From the DC analysis of the of DO-OTA conducted using the PSPICE simulations, it has been concluded that the input vs output characteristics of the DO-OTA section will remain in linear range for the input dynamic range of -300mV to 300mV. This input dynamic range of the DO-OTA section has been further limited by the bias current i.e.  $I_{b2}$ .

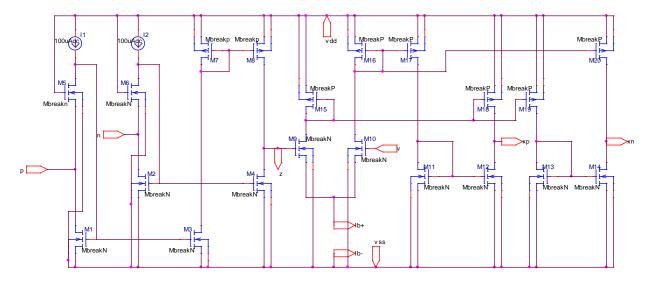

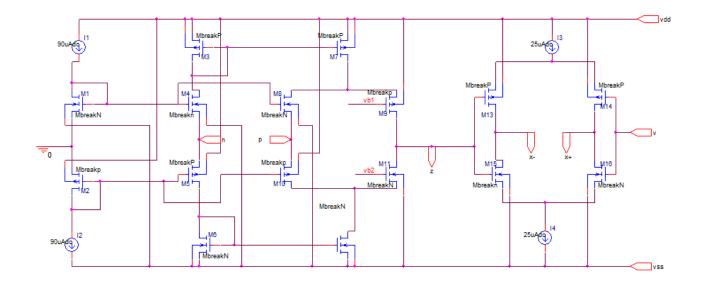

#### 3.3.1.3 DC characteristics of CD-DITA Block:-

To form the CD-DITA block both the CDU section and the DO-OTA section has been cascaded. The PSPICE schematic of CD-DITA has been presented in the Fig. 3.16 and the Bias current used to bias the both the CDU section and the DO-OTA section i.e.  $I_{b1}$  and  $I_{b2}$  has been chosen as  $100\,\mu$ A.

For verifying unity current gain i.e.  $A_1 = 1$  while transferring input current from the input current terminal i.e. p terminal to the output current terminal i.e.  $x \pm$  terminal, DC analysis curves between the output current and the input current i.e.  $I_{x+}$  vs  $I_p$  has been performed by varying the externally connected resistance  $R_z$  at the z-terminal has been plotted.

Fig. 3.16 PSPICE schematic of CD-DITA block

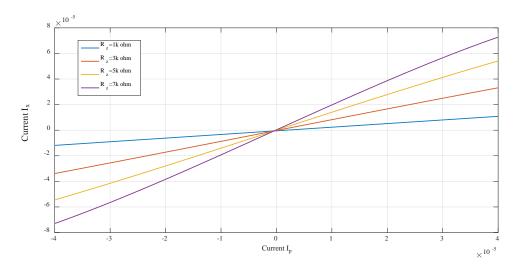

The DC analysis curves presented in the Fig. 3.17 shows the variation of externally connected resistance  $R_z$  at the z terminal on the output vs input i.e.  $I_{x+}$  vs  $I_p$  graph. The conditions that are used to achieve these plotted results are first the current at the input p terminal i.e.  $I_p$  has been varied from the  $-60\mu A$  to  $60\mu A$  along with applying the parametric sweep on  $R_z$  keeping the values of  $R_z$  as  $1k\Omega$ ,  $3k\Omega$ ,  $5k\Omega$  &  $7k\Omega$  secondly the current at the input p terminal i.e.  $I_p$  has been kept zero i.e.  $I_p = 0uA$ .

Fig. 3.17 Current transfer from the p terminal to the x + terminal ( $I_{x+}$  vs  $I_p$ ) with parametric sweep on  $R_z \& I_n = 0$

From these DC plotted results, the value of the external resistance connected at the z-terminal i.e.  $R_z$  for achieving unity current gain i.e.  $A_I = 1$  of the CD-DITA block, has come out to be the value of  $3.55k\Omega$  that has been conformed from the  $I_{x+}$  vs  $I_p$  curve.

DC plotted results the value of the external resistance connected at the z-terminal i.e.  $R_z$  for achieveing unity current gain i.e.  $A_I = 1$  of the CD-DITA block, has come out to be the value of  $3.55k\Omega$  these has been conformed from the  $I_{x+}$  vs  $I_p$  curve that has been plotted by using the value of  $R_z = 3.55k\Omega$  and has been presented in the Fig. 3.18.

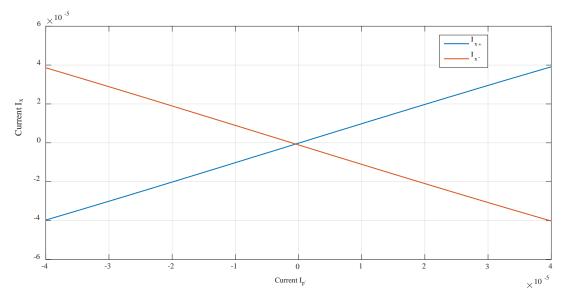

Fig. 3.18 Current transfers from p terminal to  $x \pm$  terminal ( $I_{x\pm}$  vs  $I_p$ ) with  $I_n = 0$  and  $R_z = 3.55k\Omega$

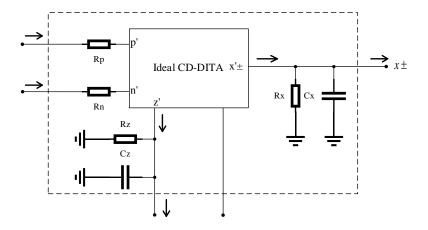

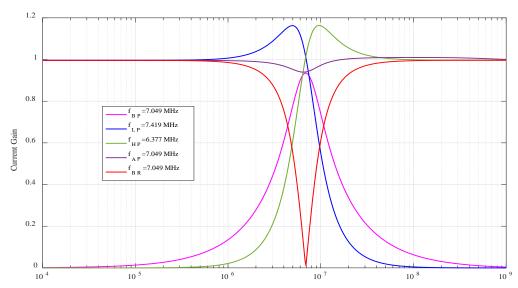

DC analysis curves between the output current and the input current i.e.  $I_{x+}$  vs  $I_p$  has been performed by varying the bias current  $I_{b2}$  as been plotted. The DC analysis curves presented in the Fig. 3.19 presents the effect of the variation of the bias current  $I_{b2}$  on the output current vs the input current graphs i.e.  $I_{x+}$  vs  $I_p$  graph with the condition of keeping  $I_n = 0$  and the externally connected resistance at the z-terminal i.e.  $R_z = 3.55k\Omega$ .