# GRID/OFF-GRID MULTILEVEL SPLIT VOLTAGE CONVERTER FOR PHOTOVOLTAIC SYSTEM FEEDING VARIETY OF LOADS

#### DISSERTATION

SUBMITTED IN PARTIAL FULFILLMENT OF THE REQUIREMENTS

FOR THE AWARD OF THE DEGREE OF

## DOCTOR OF PHILOSOPHY

Submitted by:

**Amritesh Kumar**

(Roll no. 2K11/PhD/EE/13)

Under the supervision of

Prof. Vishal Verma

# DEPARTMENT OF ELECTRICAL ENGINEERING

## **DELHI TECHNOLOGICAL UNIVERSITY**

(Formerly Delhi College of Engineering)

Bawana Road, Delhi-110042

2017

**DECLARATION**

I, AMRITESH KUMAR (2K11/PhD/EE/13) hereby declare that the work, which is

being presented in the project report entitled, "GRID/OFFGRID MULTILEVEL

SPLIT VOLTAGE CONVERTER FOR PHOTOVOLTAIC SYSTEM FEEDING

VARIETY OF LOADS" submitted for partial fulfilment of the requirements for the

award of the degree of Doctor of Philosophy is an authentic record of my own work

carried out under the able guidance of Dr. VISHAL VERMA, Professor, EED, DTU.

The matter embodied in the dissertation work has not been plagiarized from anywhere

and the same has not been submitted for the award of any other degree or diploma in

full or in part.

Submitted by:-

AMRITESH KUMAR

(2K11/PhD/EE/13)

**Electrical Engineering Department**

ii

#### DEPARTMENT OF ELECTRICAL ENGINEERING

#### DELHI TECHNOLOGICAL UNIVERSITY

(Formerly Delhi College of Engineering)

## **CERTIFICATE**

This is to certify that the thesis entitled, "GRID/OFF-GRID MULTILEVEL SPLIT VOLTAGE CONVERTER FOR PHOTOVOLTAIC SYSTEM FEEDING VARIETY OF LOADS", submitted by Mr. AMRITESH KUMAR, Roll No. 2K11/PhD/EE/13, student of Doctor of Philosophy in Electrical Engineering Department at Delhi Technological University (Formerly Delhi College of Engineering), is a dissertation work carried out by him under my guidance during session 2011-2017 towards the partial fulfillment of the requirements for the award of degree of Doctor of Philosophy.

The uniqueness of the thesis pertains to grid/off-grid multilevel split voltage converter for photovoltaic system feeding variety of loads, which has not been reported elsewhere.

I wish him all the best in his endeavors.

(Dr. VISHAL VERMA)

Professor, EED, DTU

SUPERVISOR

#### **ACKNOWLEDGMENT**

One looks back with appreciation to the brilliant teachers, but with gratitude to those who touched our human feelings. The curriculum is so much necessary raw material, but warmth is the vital element for the growing plant and for the soul of the child.

— Carl Jung

It is my pleasure to be indebted to various people, who directly or indirectly contributed to the development of this work and who influenced my thinking and behavior during the course of study. Firstly I would like to express my deep gratitude to my esteemed supervisor **Prof. Vishal Verma** for his invaluable guidance, constant encouragement with praise, effective criticism by example and for creating an environment so conducive for learning. His ability to manage students amidst his administrative work is something which puzzles so many people around. He showed me different ways to approach a research problem and the need to be persistent to accomplish any goal. His wide knowledge and his logical way of thinking have been of great value for me. His understanding, encouraging and personal guidance have provided a good basis for the present thesis.

I am grateful to **Prof. Madhusudan Singh**, Head of Department of Electrical Engineering for his constructive help, suggestions, and encouragement during the whole course of the work. I would also like to thank all the faculty of Electrical Engineering Department for their constant support.

I thank my comprehensive examination and DRC committee members: Prof. Bhim Singh (IIT Delhi), Prof. Bhuvaneshwari (IIT Delhi), Prof. Pragati Kumar, Prof. Narendra Kumar –II, Prof Rajiv Kapoor, Dr. Alka Singh, Dr. Mini Sreejeth for guiding me throughout my research work.

I am extremely grateful to authorities of Delhi Technological University (DTU) for

providing me cutting edge technology and valuable resources to carry out my research

work.

I would like to extend thanks to my colleagues Mr. Peeyush Pant, Ms. Aarti Kane, Dr.

Manoj Badoni, Ms. Lovely Goyal, Mr. Ajeet Dhakar, Mr. Ramesh Singh, Ms. Ritika

Gour, Ms. Vandana Arora, Mr. Shirish Raizada and Ms. Pankhuri Asthana and Mr.

Anil Butola for their support and cooperation from time to time during my Ph.D

tenure. I would also like to thank Mr. Dhruv, Mr. Dayaram, Mr. Kapil, Mr. Sarthak

Jain and Mr. Aditya Narula for their kind assistance throughout my Ph.D.

My heartfelt thanks to my father and mother for their constant motivation and support

during various phases of Ph.D. It is very difficult to find the right words to express my

gratitude towards my wife, Manisha Mani, my son, Reyansh Kashyap, brother

Pushkar and my In-Laws. Their support without any complaint or regret has enabled

me to complete this Ph.D. thesis. I extend my very sincere and special thanks to them

for their love, understanding, support, endless patience, tolerance during the writing

of this thesis and encouragement when it was most required.

And last, but certainly not least, my sincere thanks to all people who have helped

directly or indirectly towards the completion of this thesis.

Above all, I thank God for everything.

Above all, I wish to deeply thank God for his blessings and providing me the strength

to complete my Ph.D.

Mr. Amritesh Kumar Delhi Technological University

New Delhi

$\mathbf{v}$

## GRID/OFF-GRID MULTILEVEL SPLIT VOLTAGE CONVERTER FOR PHOTOVOLTAIC SYSTEM FEEDING VARIETY OF LOADS

#### **ABSTRACT**

With growing pressure on depleting fossil fuels reserves, the focus has been shifted for harnessing more and more energy from renewable sources for sustainable growth. Photovoltaic system has emerged as a most appropriate solution due to proximity to the load centers and more or less predictable nature of intermittency. Conventional centralized photovoltaic (PV) grid tie inverters suffer from the problem of lower efficiency, high filter size, and limited depth of operation for remaining in connection with the grid, particularly under lower insolation/partial shading condition. The effect is reported to be more pronounced for single stage inverters integrating with weak distribution systems.

Further with the advancement of technology the residential loads have witnessed a paradigm shift from linear loads to nonlinear, dynamic and constant power loads which are customizable and configurable to cater specific application. To avoid multiplicity of AC – DC through DC-DC or DC-AC conversions, the concept of DC nanogrids have also evolved to cater the need of a variety of such loads.

Investigation of a multirole bidirectional cascaded multilevel converter (CMC) configuration in which a single phase supply is split into 3 different DC links enabling staggered PV connections and possibility of feeding variety of loads have been carried out. The considered configuration is also utilized to feed isolated single phase loads in an off-grid mode using appropriate modulation technique. Considered loads include dynamic, constant power and passive loads in addition to open-end winding induction motor drive (OEIM), battery charging/discharging etc. The connectivity of the load is considered on DC buses while in off-grid/grid connected mode and on AC side too while in off-grid modes. The proposed system configuration and the considered control algorithm suits to the majority of the residential loads while enabling it to act smartly for stabilizing the grid in case of the need. Further investigation on algorithm involved the DC bus balancing embedded in the control to ensure balanced voltage operation or operation at different voltages dictated by individual MPPT controller

across the DC links. The control scheme is further explored for bidirectional power transfer with smartly charging/discharging control of the split battery stacks at customized rates depending on the SoC's of battery stacks and on feeder loading conditions, without disturbing the DC bus voltages. The exploration has been extended for operation during under-voltage grid condition where the customization in proposed algorithm enables the rotating charge control algorithm which helps the grid to stabilize its voltage in conjunction with maintaining life cycle of the battery.

The proposed configuration and control enjoys the advantage of 3 separate DC buses having both voltage and power level  $1/3^{rd}$  of the total DC voltage and power, which enables the reduction in the voltage rating of capacitor; making system more modular and compact and deriving power from AC is with reduced voltage THD and providing immunity against unbalanced DC link voltages across the H-bridges.

The complete model of the CMC with a variety of loads and their embedded control is analytically derived and simulated in MATLAB Simulink environment before testing on hardware prototype for its validation. A detailed stability analysis is also presented in the d-q frame for the control design to access the feasibility of operation with a variety of loads. The effectiveness of the control algorithm under low grid frequency and dip in voltage conditions are clearly demonstrated through results. The results clearly show derived current from the grid at unity power factor ensuring improved power quality operation. Further, keeping the entire voltages on the DC buses constant or at voltage dictated by MPPT controller ensures immunity against disturbance both from AC or DC side. A comparative analysis is also done for the operation of PV under partial shading condition for a conventional 2 -level PV inverter vis-à-vis proposed CMC-based approach. Further PV-CMC system for enhanced performance under voltage sag is studied to demonstrate the LVRT capability. The d-q based control provides efficient independent and smartly control with active/reactive or both power support depending on the voltage sag and PV panel power condition. The thesis also proposes control techniques for off-grid mode, which will match the utilization and storage of power provided by the PV panels of the same capacity and same size of the battery connected at each level. The control method utilizes rotation policy for the operation of each bridge at each level in three

fundamental cycles, to enhance both the lifetime of the battery, the operation of H-bridges and PV panels used.

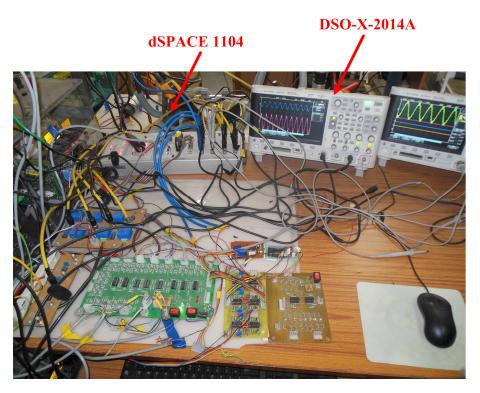

Same scale hardware prototype using open end induction motor, passive loads and battery loads (charging/discharging) on different DC links is developed and experimentally validated using requisite hardware and DSP controllers (dSPACE 1104 and dspic33FJ16GS502). The development of hardware including fabrication of various control cards, interface card, voltage and current measurement cards etc. have been indigenously done. Both simulation and experimental results are presented which always show good agreement with theoretical analysis.

## TABLE OF CONTENTS

| Declaration       | ü                                                                |

|-------------------|------------------------------------------------------------------|

| Certificate       | iii                                                              |

| Acknowledgmen     | tiv                                                              |

| Abstract          | vi                                                               |

| Table of Content  | isix                                                             |

| List of Figures   | xix                                                              |

| List of Tables    | xxix                                                             |

| List of Abbreviat | ionsxxx                                                          |

| CHAPTER – I       | INTRODUCTION1                                                    |

|                   | 1.1 General                                                      |

|                   | 1.2 Solar Photovoltaic System: Issues and Opportunities 3        |

|                   | 1.3 PV String and Arrays: Challenges                             |

|                   | 1.4 Converter/Inverter for PV System                             |

|                   | 1.5 Multilevel Topologies for PV System                          |

|                   | 1.6 Cascaded Multilevel Topology for PV System                   |

|                   | 1.6.1 Basic Configuration and Operation                          |

|                   | 1.6.2 Issues of Multilevel Converter                             |

|                   | 1.6.3 Large PV farms connected to 3 phase system                 |

|                   | 1.6.4 Small PV grid system for residential PV                    |

|                   | 1.7 Controlling of Cascaded Multilevel Topology for PV System 15 |

|                   | 1.8 Variety of DC Loads in Residential Power System 15           |

|                   | 1.9 Scope of the work                                            |

|                   | 1.9.1 Development of 1φ to 3φ Voltage Splitter via CMC for       |

|                   | Feeding Power to Three Phase OEIM Drive Load 17                  |

|                   | 1.9.2 Development of Appropriate Simulink Model for the          |

|                   | Realization of Single Phase CMC for Feeding Variety of           |

|                   | Loads17                                                          |

|              | 1.9.3 Derivation of Smart Power Control of CMC Unit for        |    |

|--------------|----------------------------------------------------------------|----|

|              | OEIM Pump Drive                                                | 8  |

|              | 1.9.4 Development of Split Battery Charging / Discharging      |    |

|              | Topology using 1 φ CMC Unit for Bidirectional Power            |    |

|              | Flow 1                                                         | 8  |

|              | 1.9.5 Derivation of Control Logic for Customized Charging /    |    |

|              | Discharging of CMC for Life Cycle Improvement of               |    |

|              | Battery Units                                                  | 8  |

|              | 1.9.6 Derivation of Fast and Decoupled Control Logic for       |    |

|              | Integration of Separate PV Units on Individual DC Links        |    |

|              | of CMC1                                                        | 9  |

|              | 1.9.7 Development of PV – CMC Control Logic for Ride           |    |

|              | Through Capability under Dip in Grid Voltage 1                 | 9  |

|              | 1.10 Organization of Thesis                                    | 9  |

| CHAPTER – II | LITERATURE REVIEW 2                                            | 3  |

|              | 2.1 General                                                    | .3 |

|              | 2.2 Literature Survey                                          | .3 |

|              | 2.2.1 Solar PV System                                          | .3 |

|              | 2.2.2 MPPT techniques for PV system                            |    |

|              | 2.2.3 Converter / Inverter Topologies for Grid / Off-Grid PV   |    |

|              | System2                                                        | .5 |

|              | 2.2.4 Cascaded Multilevel Converter / Inverter Suitability for |    |

|              | PV System2                                                     | .7 |

|              | 2.2.5 Modulation Methods for Cascaded Multilevel Converter     |    |

|              | Inverter System                                                | 8  |

|              | 2.2.6 Low Voltage Ride Through (LVRT) capability of PV         |    |

|              | Converter System                                               | 9  |

|              | 2.2.7 Control Aspects of PV – CMC System                       |    |

|              | 2.2.8 PV – CMC system feeding variety of loads (Static load,   |    |

|              | dynamic load, and Constant power load)                         | 1  |

|              | 2.3 Research Gap                                               |    |

|              | 2.4 Conclusion                                                 |    |

|              |                                                                |    |

| CHAPTER – III | MODELING AND CONTROL OF PV INTERFACED CMC FOR                  |  |  |

|---------------|----------------------------------------------------------------|--|--|

|               | APPLICATION WITH GRID / OFF - GRID SYSTEM AND                  |  |  |

|               | SUBSYSTEMS                                                     |  |  |

|               | 3.1 General                                                    |  |  |

|               | 3.2 Modeling of PV System                                      |  |  |

|               | 3.2.1 Modeling of PV cell                                      |  |  |

|               | 3.2.2 Modeling of PV Panel                                     |  |  |

|               | 3.3 Modeling and Control of Cascaded Multilevel Converter 38   |  |  |

|               | 3.3.1 Basic Mathematical Modeling of Cascaded Multilevel       |  |  |

|               | Converter                                                      |  |  |

|               | 3.3.2 D-Q Based Modeling of Cascaded Multilevel Converter      |  |  |

|               |                                                                |  |  |

|               | 3.3.3 Plant Model Design of Cascaded Multilevel Converter. 40  |  |  |

|               | 3.3.4 Switching Technique for Cascaded Multilevel Converter    |  |  |

|               | 3.3.5 Phasor Representation for Multilevel System Operation 45 |  |  |

|               | 3.4 Modeling of Battery Energy System Emulating near Constant  |  |  |

|               | Power Load (CPL)                                               |  |  |

|               | 3.5 Modeling of Open End Winding Induction Motor (OEIM)        |  |  |

|               | Pump Drive                                                     |  |  |

|               | 3.6 Conclusion                                                 |  |  |

| CHAPTER - IV  | SINGLE PHASE OFF-GRID PHOTOVOLTAIC SOURCED CASCADED            |  |  |

|               | MULTILEVEL INVERTER FOR POWER BALANCED OPERATION 50            |  |  |

|               | 4.1 General                                                    |  |  |

|               | 4.2 Features of Single Phase Off-Grid PV System using Cascaded |  |  |

|               | Multilevel Inverter                                            |  |  |

|               | 4.3 System Configuration of Single Phase Grid Connected PV     |  |  |

|               | System using Cascaded Multilevel Inverter                      |  |  |

|               | 4.4 Control Theory for PV fed Cascaded Multilevel Inverter 52  |  |  |

|               | 4.5 MATLAB based Simulation of Single Phase PV Off-Grid        |  |  |

|               | Cascaded Multilevel Inverter System                            |  |  |

|               | 4.5.1 Performance Evaluation of Single Phase PV fed            |  |  |

|               | Multilevel System under Varying Insolation Condition 55        |  |  |

|            | 4.5.2 Performance Evaluation of CHBMLI for Power Balance         | е                    |

|------------|------------------------------------------------------------------|----------------------|

|            | Operation using Battery Support PV Systems                       | 56                   |

|            | 4.6 Hardware Implementation of Single phase PV Off-Grid          |                      |

|            | Cascaded Multilevel Inverter System                              | 58                   |

|            | 4.7 Result and Discussion                                        | 59                   |

|            | 4.7.1 Performance Evaluation of Off-Grid PV fed Single Phase     | se                   |

|            | Cascaded Multilevel Inverter for UPF operation                   | 59                   |

|            | 4.7.2 Performance Evaluation of Off-Grid PV Fed Multilevel       |                      |

|            | System with Power Transaction through Battery                    | 60                   |

|            | 4.8 Conclusion                                                   | 61                   |

|            |                                                                  |                      |

| CHAPTER -V | CONTROL AND IMPLEMENTATION OF OEIM PUMP DRIVE USING              | $\mathbf{\tilde{J}}$ |

|            | SINGLE PHASE CASCADED MULTILEVEL CONVERTER                       | 63                   |

|            | 5.1 General                                                      | 63                   |

|            | 5.2 Features of OEIM Pump Drive using Single Phase Cascaded      |                      |

|            | Multilevel Converter                                             | 63                   |

|            | 5.3 System Configuration Single Phase Cascaded Multilevel        |                      |

|            | Converter                                                        | 65                   |

|            | 5.4 Control Approach for Single Phase Cascaded Multilevel        |                      |

|            | Converter                                                        | 65                   |

|            | 5.5 Feasibility Analysis of the Designed Controller using Bode P | lot                  |

|            | for Cascaded Multilevel Converter                                | 67                   |

|            | 5.6 Control Approach for V/F Control of Open End Winding         |                      |

|            | Induction Motor                                                  | 67                   |

|            | 5.7 MATLAB based Simulation of Single Phase Cascaded             |                      |

|            | Multilevel Interfaced 3 Phase Pump Drive                         | 69                   |

|            | 5.8 Hardware Implementation of Single Phase Cascaded Multilev    | el                   |

|            | Interfaced 3 Phase Pump Drive                                    | 70                   |

|            | 5.9 Result and Discussion                                        | 73                   |

|            | 5.9.1 Performance Evaluation of Single Phase Cascaded            |                      |

|            | Multilevel Converter for Balanced DC links and UPF operation     | on                   |

|            |                                                                  | 74                   |

|              | 5.9.2 Performance Evaluation of Single Phase Cascaded           |

|--------------|-----------------------------------------------------------------|

|              | Multilevel Drive System under Perturbing Pump Load using        |

|              | V/F Control77                                                   |

|              | 5.10 Conclusion                                                 |

| CHAPTER – VI | SMART OEIM PUMP DRIVE AND DC LOADS USING CASCADED               |

|              | MULTILEVEL CONVERTER                                            |

|              | 6.1 General                                                     |

|              | 6.2 Features of OEIM Pump Drive using Single Phase Cascaded     |

|              | Multilevel Converter                                            |

|              | 6.3 System Configuration of Single Phase Cascaded Multilevel    |

|              | Converter83                                                     |

|              | 6.4 Smart Pump Load Management Control                          |

|              | 6.5 Control Theory of CMAR and DC Link Balancing Scheme 86      |

|              | 6.6 Control Approach for Vector Control of Open End Winding     |

|              | Induction Motor                                                 |

|              | 6.7 MATLAB based Simulation of Single Phase Cascaded            |

|              | Multilevel Interfaced 3 Phase Pump Drive                        |

|              | 6.8 Hardware implementation of Single Phase Cascaded Multilevel |

|              | Interfaced 3 Phase Pump Drive                                   |

|              | 6.9 Result and Discussion                                       |

|              | 6.9.1 Performance Evaluation of Single Phase Cascaded           |

|              | Multilevel Converter for Balanced DC Link and UPF Operation     |

|              | 97                                                              |

|              | 6.9.2 Performance Evaluation of Single Phase Cascaded           |

|              | Multilevel Converter under Perturbing Pump Load using Vector    |

|              | Control98                                                       |

|              | 6.9.3 Performance Evaluation of Single Phase Cascaded           |

|              | Multilevel Drive System under Changing Grid Frequency           |

|              | Condition102                                                    |

|              | 6.10 Conclusion 103                                             |

| CHAPTER - VII | ADALINE CONTROLLED CASCADED MULTILEVEL RECTIFIER             |

|---------------|--------------------------------------------------------------|

|               | FEEDING 3 PHASE SUBMERSIBLE PUMP ON SINGLE PHASE RURAL       |

|               | FEEDER105                                                    |

|               | 7.1 General                                                  |

|               | 7.2 Features of OEIM Pump Drive using Single Phase Cascaded  |

|               | Multilevel Converter                                         |

|               | 7.3 System Configuration of Single Phase Cascaded Multilevel |

|               | Converter                                                    |

|               | 7.4 Control Approach for Adaline Controlled Single Phase     |

|               | Cascaded Multilevel Converter                                |

|               | 7.4.1 ADALINE based Control Scheme for Parameter             |

|               | Extraction107                                                |

|               | 7.4.2 CMAR DC Bus Voltage Control Scheme based on            |

|               | ADALINE110                                                   |

|               | 7.4.3 Control Scheme for Handling Uneven Losses and          |

|               | Perturbing Grid Conditions111                                |

|               | 7.4.4 Working of Controller under Transient Condition113     |

|               | 7.5 MATLAB Simulation of Single Phase Cascaded Multilevel    |

|               | Interfaced 3 Phase Pump Drive115                             |

|               | 7.6 Hardware Implementation of ADALINE Controlled Single     |

|               | Phase Cascaded Multilevel Interfaced Pump Load for 3 Phase   |

|               | Drive                                                        |

|               | 7.7 Result and Discussion                                    |

|               | 7.7.1 Performance Evaluation of Single Phase Cascaded        |

|               | Multilevel Converter for Balanced DC Links and UPF           |

|               | Operations119                                                |

|               | 7.7.2 Performance Evaluation of Single Phase Cascaded        |

|               | Multilevel Converter under Perturbing Pump Load using Vector |

|               | Control                                                      |

|               | 7.7.3Performance Evaluation of Single Phase Cascaded         |

|               | Multilevel Drive System under changing Grid Voltage122       |

|               | 7.8 Conclusion 124                                           |

| CHAPTER – VIII SINGLE PHASE ON – BOARD SMART SPLIT VOLTAGE MULTI- |                                                                   |  |

|-------------------------------------------------------------------|-------------------------------------------------------------------|--|

|                                                                   | MODE INTEGRATED BIDIRECTIONAL CONVERTER FOR EV /                  |  |

|                                                                   | PHEV                                                              |  |

|                                                                   | 8.1 General                                                       |  |

|                                                                   | 8.2 Feature of Battery Charging / Discharging Topology using      |  |

|                                                                   | Bidirectional Single Phase Cascaded Multilevel Converter125       |  |

|                                                                   | 8.3 System Configuration of Bidirectional Single Phase Cascaded   |  |

|                                                                   | Multilevel Converter                                              |  |

|                                                                   | 8.4 Concept of Charging / Discharging of Battery in a String with |  |

|                                                                   | Dissimilar SOC's                                                  |  |

|                                                                   | 8.5 Phasor Analysis for Unity Power Factor (UPF) Operation of     |  |

|                                                                   | CMCS for Charging/Discharging                                     |  |

|                                                                   | 8.6 Control Theory for Multimode Operation131                     |  |

|                                                                   | 8.6.1 Droop Control for Smart Power Flow Control131               |  |

|                                                                   | 8.6.2 Control Analysis for Even/Uneven Charge/Discharge of        |  |

|                                                                   | Battery Stack                                                     |  |

|                                                                   | 8.7 MATLAB based Simulation of Bidirectional Single Phase         |  |

|                                                                   | Cascaded Multilevel Converter                                     |  |

|                                                                   | 8.8 Hardware Implementation of Bidirectional Single Phase         |  |

|                                                                   | Cascaded Multilevel Converter                                     |  |

|                                                                   | 8.9 Result and Discussion                                         |  |

|                                                                   | 8.9.1 Performance Evaluation of Single Phase Cascaded             |  |

|                                                                   | Multilevel Converter for Balanced DC Links and UPF                |  |

|                                                                   | Operation                                                         |  |

|                                                                   | 8.9.2 Performance Evaluation of Single Phase Cascaded             |  |

|                                                                   | Multilevel Converter under same/different Battery Charging        |  |

|                                                                   | Currents and Study its Dynamic Response144                        |  |

|                                                                   | 8.9.3 Performance Evaluation of Single Phase Cascaded             |  |

|                                                                   | Multilevel Converter for V2G Support ad its Transition from       |  |

|                                                                   | G2V and V2G                                                       |  |

|                                                                   | 8.10 Conclusion                                                   |  |

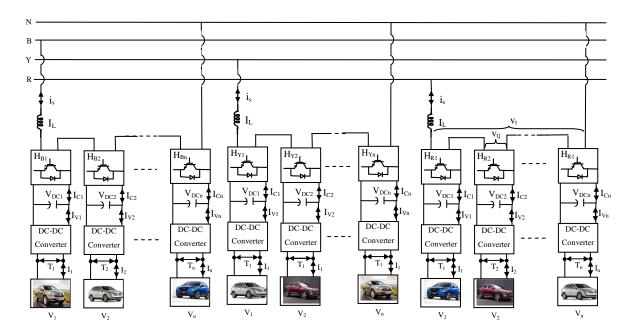

| CHAPTER-IX                                                        | SMART PARKING FOR PHEV / EV USING SOLID STATE SPLIT               |  |

|                                                                   | VOLTAGE BIDIRECTIONAL CONVERTER AT UPF WITH V2G                   |  |

|                                                                   | CAPABILITY                                                        |  |

|            | 9.1 General                                                      |

|------------|------------------------------------------------------------------|

|            | 9.2 Features of OEIM Pump Drive using Single Phase Cascaded      |

|            | Multilevel Converter                                             |

|            | 9.3 System Configuration of Single Phase Cascaded Multilevel     |

|            | Converter                                                        |

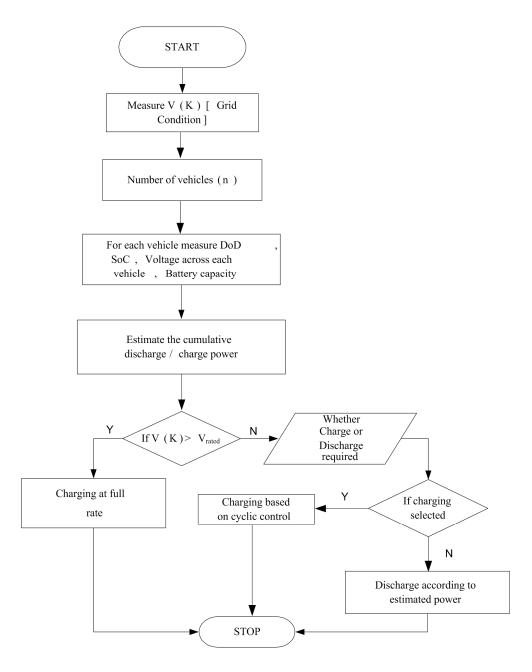

|            | 9.4 Flowchart for Smartly Charging / Discharging Operation150    |

|            | 9.5 Control Logic for SSSVC Operation                            |

|            | 9.6 MATLAB based Simulation of PHEV / EV using Solid State       |

|            | Split Voltage Bidirectional Converter                            |

|            | 9.6.1 Performance Evaluation of Bidirectional Cascaded           |

|            | Multilevel Converter under Cyclic Control152                     |

|            | 9.6.2 Performance Evaluation of Bidirectional Cascaded           |

|            | Multilevel Converter with Transition from Charging to            |

|            | Discharging Mode155                                              |

|            | 9.7 Hardware Implementation of PHEV / EV using Solid State Split |

|            | Voltage Bidirectional Converter                                  |

|            | 9.8 Result and Discussion                                        |

|            | 9.8.1 Performance Evaluation of Bidirectional Cascaded           |

|            | Multilevel Converter under Balanced DC Link Voltage              |

|            | Condition and Study Dynamic Response with Transition from        |

|            | Charging (G2V) to Discharging (V2G)156                           |

|            | 9.8.2 Performance Evaluation of Bidirectional Cascaded           |

|            | Multilevel Converter with Cyclic Control under Voltage Droop     |

|            | 157                                                              |

|            | 9.9 Conclusion                                                   |

| CHAPTER -X | PERFORMANCE ENHANCEMENT OF SINGLE PHASE GRID                     |

|            | CONNECTED PV SYSTEM UNDER PARTIAL SHADING USING                  |

|            | CASCADED MULTILEVEL CONVERTER160                                 |

|            | 10.1 General                                                     |

|            | 10.2 Features of Single Phase Grid Connected PV System using     |

|            | Cascaded Multilevel Converter                                    |

|            | 10.3 System Configuration of Single Phase Grid Connected PV      |

|            | System using Cascaded Multilevel Converter161                    |

|            | 10.4 PV Panel Sizing162                                          |

|            |                                                                  |

|              | 10.5 Partial Shading Condition / Non-Uniform Insolation165     |

|--------------|----------------------------------------------------------------|

|              | 10.6 Control Theory for PV – CMC Operation167                  |

|              | 10.7 MATLAB based Simulation of Single Phase Grid Connected    |

|              | PV Multilevel System169                                        |

|              | 10.7.1 Performance Evaluation of 2 Level Single Stage PV -     |

|              | VSC170                                                         |

|              | 10.7.2 Performance Evaluation of 2 Level Double Stage String   |

|              | PV – VSC171                                                    |

|              | 10.7.3 Performance Evaluation of Proposed Single Stage CMC     |

|              |                                                                |

|              | 10.8 Hardware Implementation of Single Phase Grid Connected PV |

|              | Multilevel System                                              |

|              | 10.9 Result and Discussion                                     |

|              | 10.9.1 Performance Evaluation of Single Phase Grid Connected   |

|              | PV Multilevel System for UPF Operation174                      |

|              | 10.9.2 Performance Evaluation of Single Phase Grid Connected   |

|              | PV Multilevel System When One Set of Panels is under Partial   |

|              | Shading Condition                                              |

|              | 10.9.3 Performance Evaluation of Single Phase Grid Connected   |

|              | PV Multilevel System with Load Perturbation on DC Link175      |

|              | 10.10 Conclusion                                               |

| CHAPTER – XI | LOW VOLTAGE RIDE THROUGH CAPABILITY OF PV – GRID               |

|              | CONNECTED CASCADED MULTILEVEL INVERTER THROUGH                 |

|              | MULTIMODE OPERATION                                            |

|              | 11.1 General                                                   |

|              | 11.2 Features of Low Voltage Ride Through Capability of PV –   |

|              | Grid Connected Cascaded Multilevel Inverter through Multimode  |

|              | Operation                                                      |

|              | 11.3 System Configuration of PV - Grid Connected Cascaded      |

|              | Multilevel Inverter for LVRT Capability through Multimode      |

|              | Operation                                                      |

|              | 11.4 Control Theory for Working Operation of PV – Grid         |

|              | Connected Cascaded Multilevel Inverter                         |

|              |                                                                |

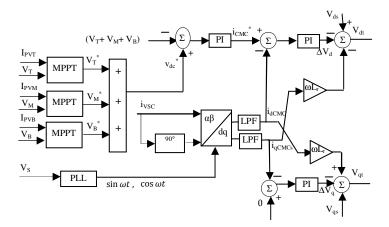

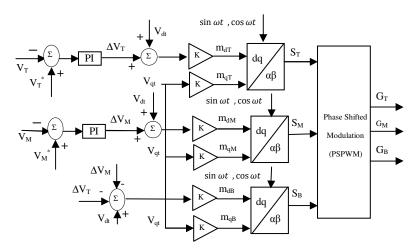

| 11.4.1 Voltage Control Loop183                                   |

|------------------------------------------------------------------|

| 11.4.2 Current Control Loop                                      |

| 11.4.3 Voltage Regulation Control of Individual DC Links185      |

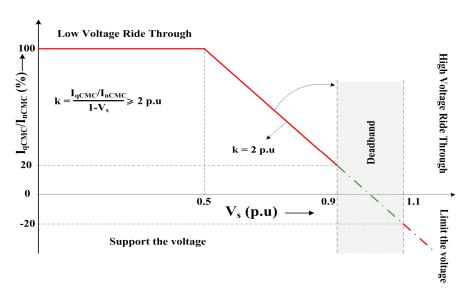

| 11.5 Capacity Limited Power Control of CMIPV under LVRT186       |

| 11.5.1 Mode 'a': When Generation is Less than Allocated          |

| Capacity Left after Catering the Mandated Requirement186         |

| 11.5.2 Mode 'b': When Generation is Above the Allocated Slot     |

| Left after Catering the Mandated Requirement of Reactive         |

| Power Support                                                    |

| 11.6 MATLAB based Simulation of PV Grid Connected PV             |

| Multilevel System through Multimode Operation                    |

| 11.6.1 Performance Evaluation of PV – Grid Connected             |

| Cascaded Multilevel Inverter through Multimode Operation         |

| under Mode 'a' Control                                           |

| 11.6.2 Performance Evaluation of PV – Grid Connected             |

| Cascaded Multilevel Inverter through Multimode Operation         |

| under Mode 'b' Control191                                        |

| 11.7 Hardware Implementation of PV – Grid Connected PV           |

| Cascaded Multilevel Inverter through Multimode Operation193      |

| 11.8 Result and Discussion                                       |

| 11.8.1 Performance Evaluation of PV – Grid Connected             |

| Cascaded Multilevel Inverter for UPF Operation194                |

| 11.8.2 Performance Evaluation of PV – Grid Connected             |

| Cascaded Multilevel Inverter through Mode 'a' Control195         |

| 11.8.3 Performance Evaluation of PV – Grid Connected             |

| Cascaded Multilevel Inverter through Mode 'b' Control197         |

| 11.9 Conclusion                                                  |

| CHAPTER – XII Main Conclusion and Suggestions for Future Work201 |

| 12.1 Main Conclusion201                                          |

| 12.2 Future Scope of the Work204                                 |

| REFERENCES 205                                                   |

| LIST OF PUBLICATIONS 216                                         |

| BIO-DATA                                                         |

## LIST OF FIGURES

| Fig. No.  | Figure Name                                                                                                                     | Page No |

|-----------|---------------------------------------------------------------------------------------------------------------------------------|---------|

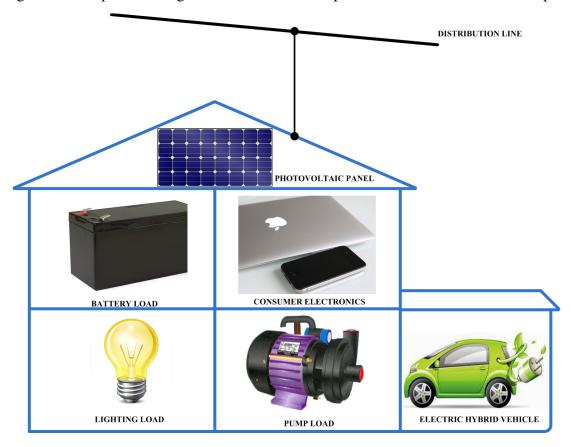

| Fig.1.1   | Simplified representation of residential loads having rooftop PV Panels                                                         | 2       |

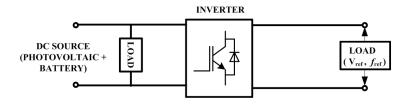

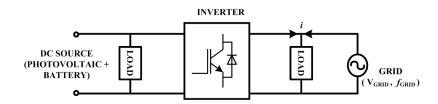

| Fig. 1.2  | Single Phase off-grid PV system                                                                                                 | 3       |

| Fig. 1.3  | Single Phase grid connected PV system                                                                                           | 3       |

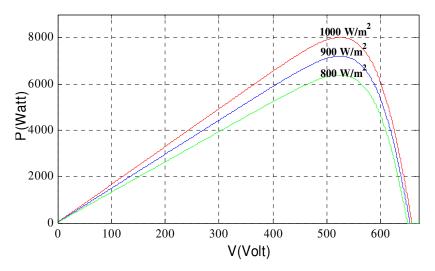

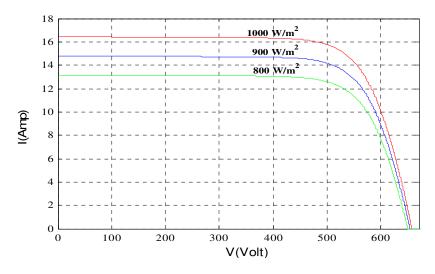

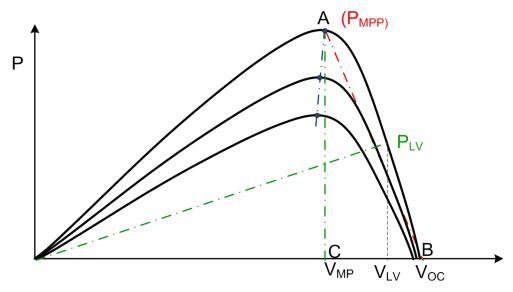

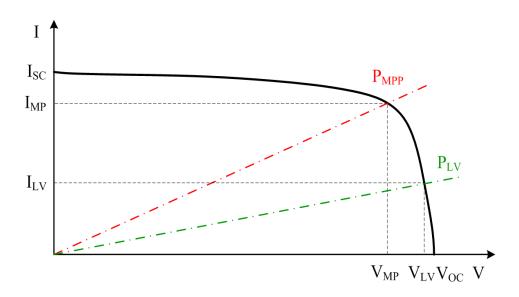

| Fig. 1.4  | P-V Characteristics of PV array                                                                                                 | 5       |

| Fig. 1.5  | I-V Characteristics of PV array                                                                                                 | 5       |

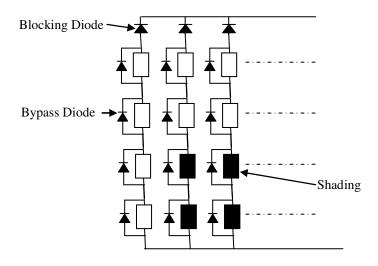

| Fig. 1.6  | Panel configuration showing partial shading                                                                                     | 6       |

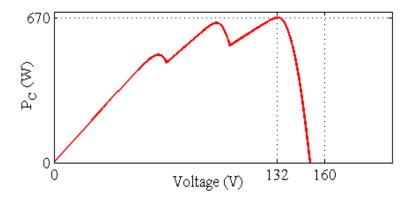

| Fig. 1.7  | P-V curve showing partial shading condition                                                                                     | 6       |

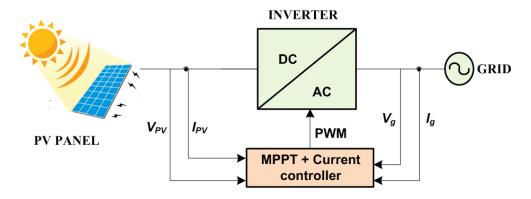

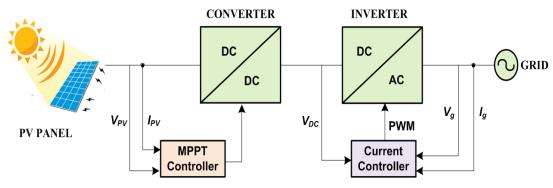

| Fig. 1.8  | Single stage topology where the dc-ac inverter is responsible for<br>the MPPT and the grid current control                      | 7       |

| Fig. 1.9  | Double stage topology where the dc-dc converter is responsible for<br>the MPPT and the dc-ac inverter controls the grid current | 7       |

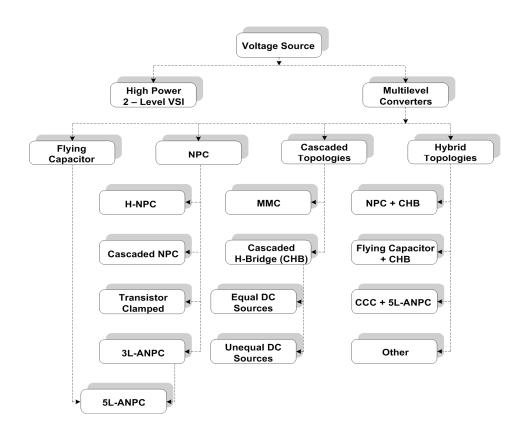

| Fig. 1.10 | Voltage source based multilevel converter classification                                                                        | 9       |

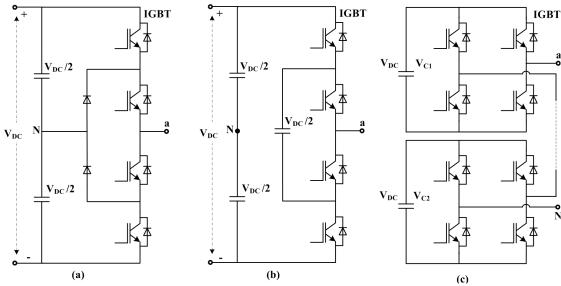

| Fig. 1.11 | Classic multilevel converter topologies (a) 3L-NPC (b) Three-level FC (c) Five-level CHB                                        | 10      |

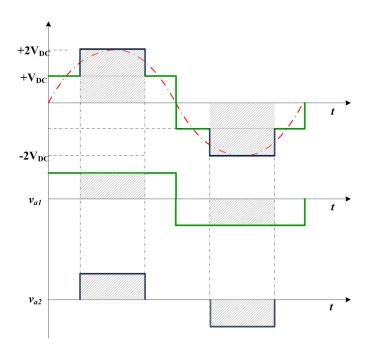

| Fig. 1.12 | Five-level CHB associated voltage waveforms                                                                                     | 11      |

| Fig. 1.13 | (a) Waveforms of phase shifted carrier signals and modulating signal                                                            | 12      |

|           | (b) Waveforms of level shifted carrier signals and modulating signal                                                            | 12      |

| Fig. 1.14 | Seven-level PV-CMC system housing various loads on the DC link                                                                  | 14      |

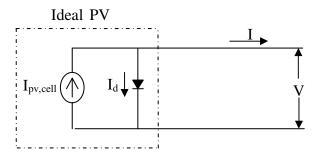

| Fig. 3.1  | Ideal PV cell model                                                                                                             | 36      |

| Fig. 3.2  | PV Panel model                                                                                                                  | 36      |

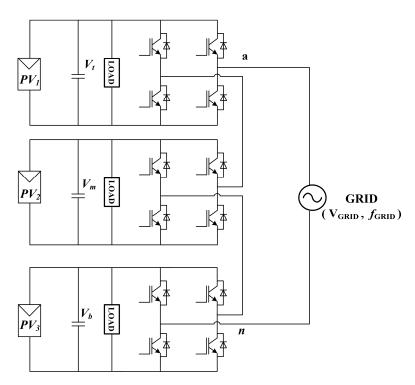

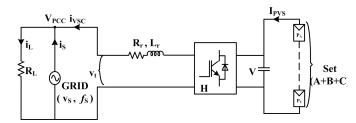

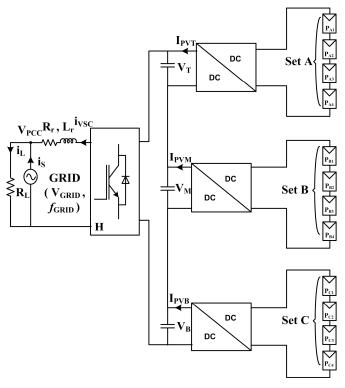

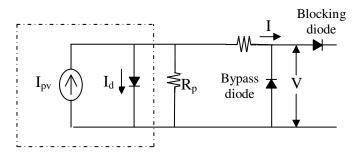

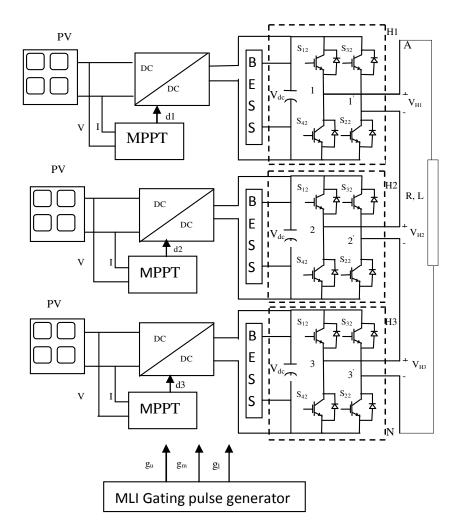

| Fig. 3.3  | System configuration of grid connected multilevel system                                                                        | 37      |

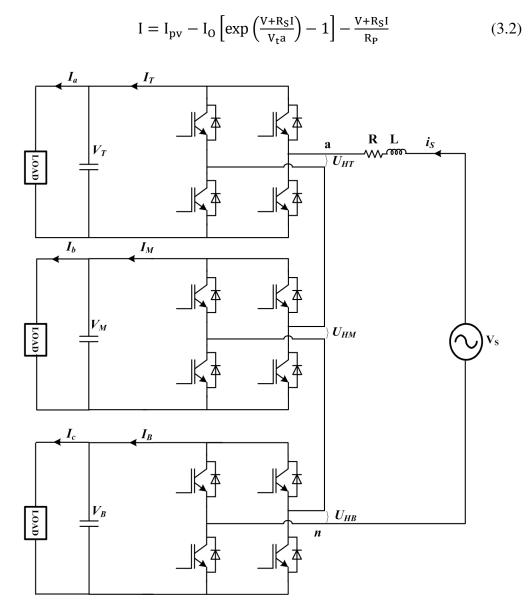

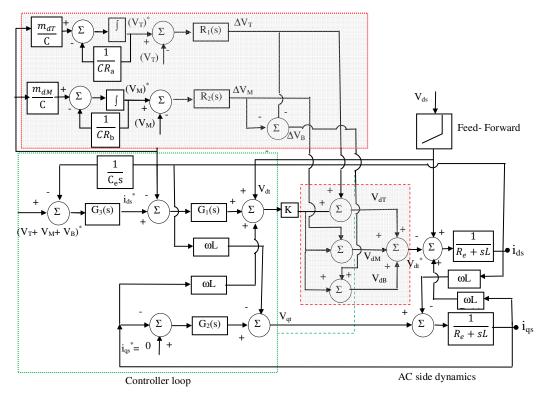

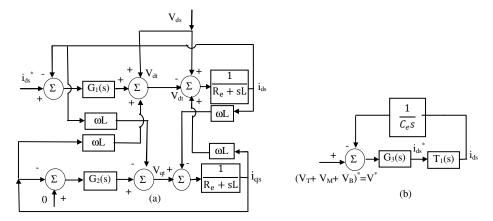

| Fig. 3.4  | Plant model of the cascaded multilevel system                                                                                   | 41      |

| Fig. 3.5  | (a) Simplified model for current loop                                                                                           | 43      |

|           | (b) Simplified model for voltage loop                                                                                           | 43      |

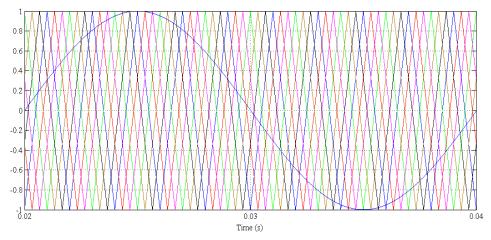

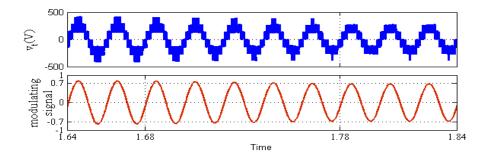

| Fig. 3.6  | Waveform for multilevel terminal voltage under varying modulation index                                                                                   | 44 |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Fig. 3.7  | Multilevel system control operation with phase shifted modulation technique                                                                               | 44 |

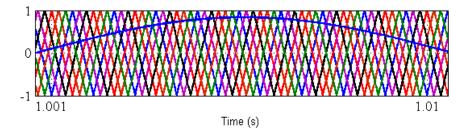

| Fig. 3.8  | Multilevel system instantaneous terminal Voltage of each H-bridge contributing towards formation of 7 level multilevel converter                          | 44 |

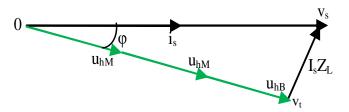

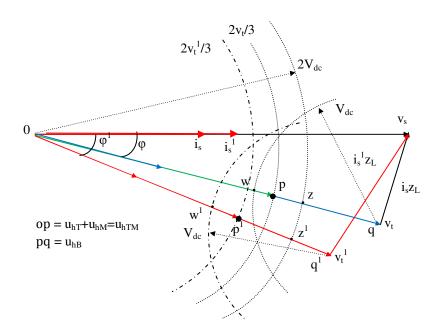

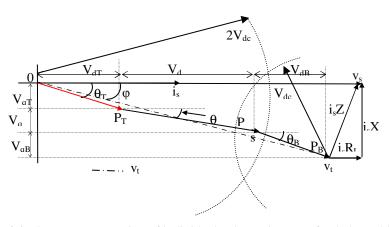

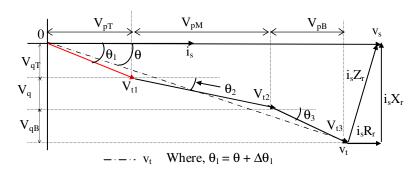

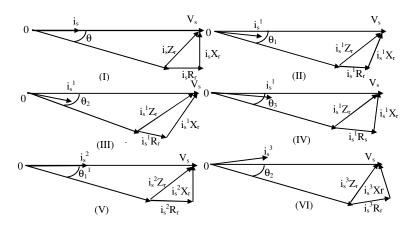

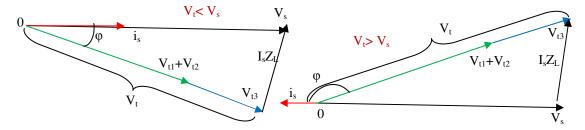

| Fig 3.9   | Phasor representation for unity power factor operation under balanced loading                                                                             | 45 |

| Fig 3.10  | Phasor diagram representing UPF and operating region with changing loading condition                                                                      | 46 |

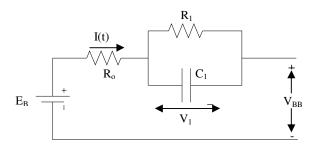

| Fig 3.11  | Randle's Li-Ion equivalent battery model application                                                                                                      | 48 |

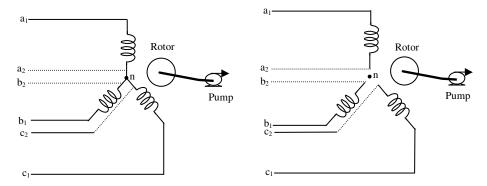

| Fig 3.12  | $3\phi$ (a) star winding induction motor (b) open end winding induction motor (OEIM)                                                                      | 48 |

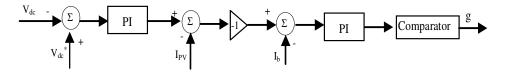

| Fig 4.1   | Block diagram for the proposed CHBMLI configuration for feeding off-grid loads                                                                            | 51 |

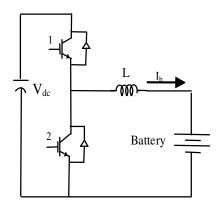

| Fig. 4.2  | Schematic of battery connection                                                                                                                           | 52 |

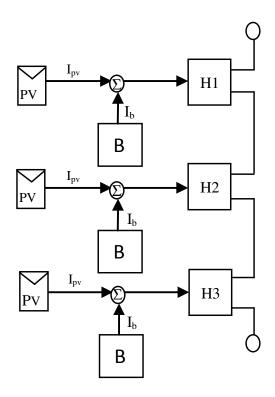

| Fig. 4.3  | Control logic for battery operation.                                                                                                                      | 52 |

| Fig. 4.4  | Single line diagram for 7 levels CHBMLI                                                                                                                   | 53 |

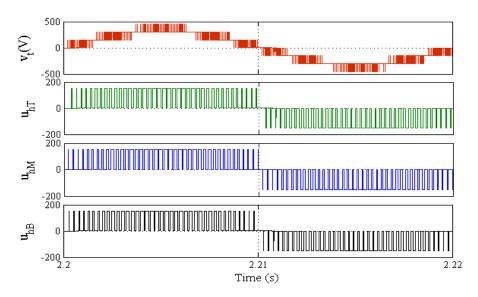

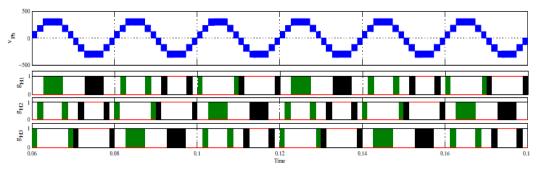

| Fig. 4.5  | Rotating gating pulse signal sequence for each H-bridge                                                                                                   | 55 |

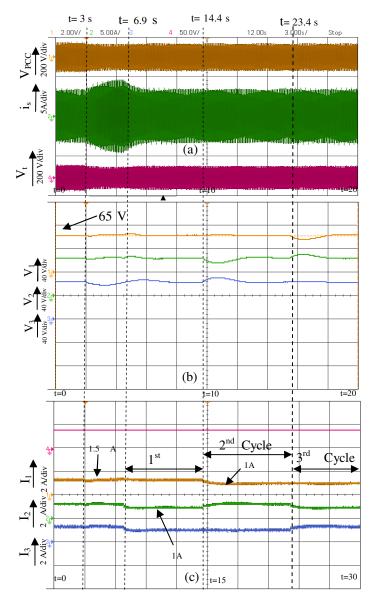

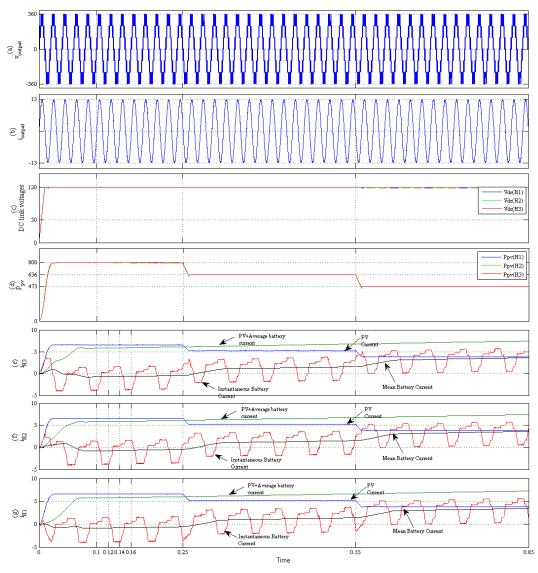

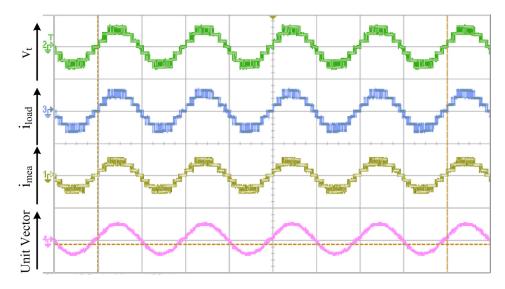

| Fig. 4.6  | Simulation waveforms for output terminal voltage and current, DC link voltages of each bridge, MPPT tracked power, PV and battery currents at each bridge | 56 |

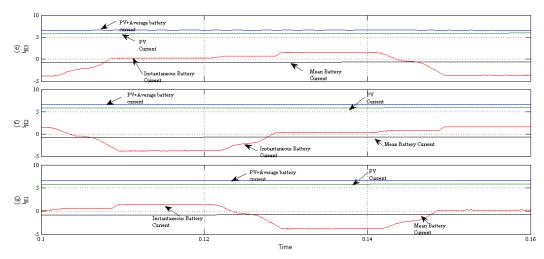

| Fig. 4.7  | Simulation waveforms for zoomed conditions of PV and battery currents.                                                                                    | 57 |

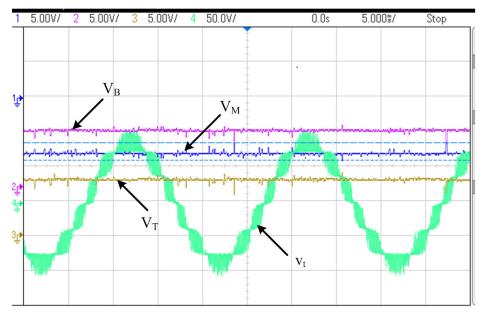

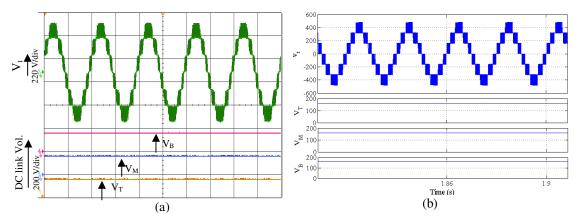

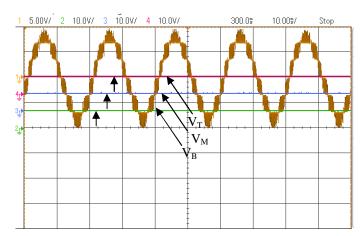

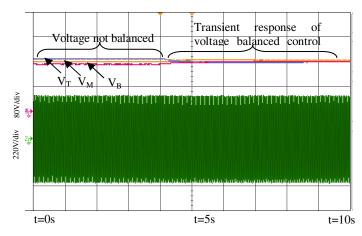

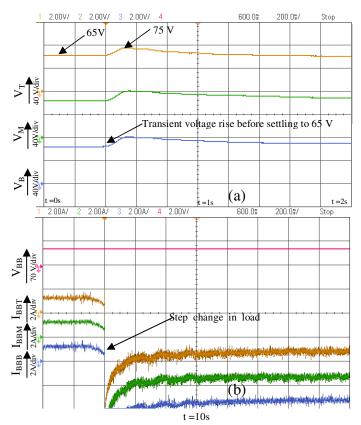

| Fig. 4.8  | Experimental results showing waveforms for DC link voltages ( $V_T$ , $V_M$ , $V_B$ ), terminal voltage ( $v_t$ )                                         | 58 |

| Fig. 4.9  | Simulation waveforms for zoomed conditions of PV and battery currents.                                                                                    | 59 |

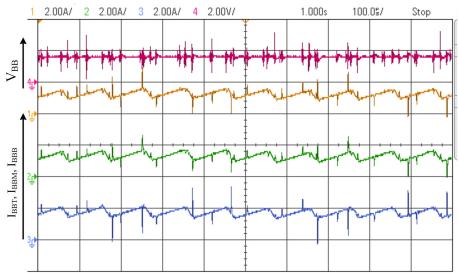

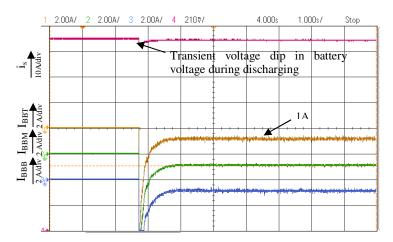

| Fig. 4.10 | Experimental result showing waveforms for Battery currents ( $I_{BBT}$ , $I_{BBM}$ , $I_{BBB}$ ), Battery voltage ( $V_{BB}$ ).                           | 60 |

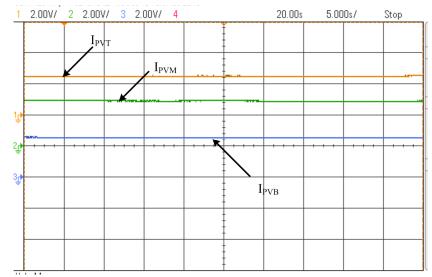

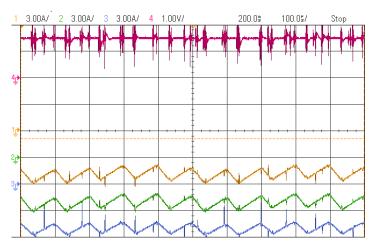

| Fig. 4.11 | Experimental result showing waveforms for PV currents ( $I_{PVT}$ , $I_{PVM}$ , $I_{PVB}$ )                                                               | 61 |

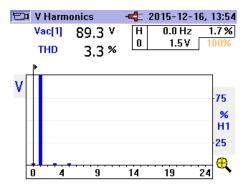

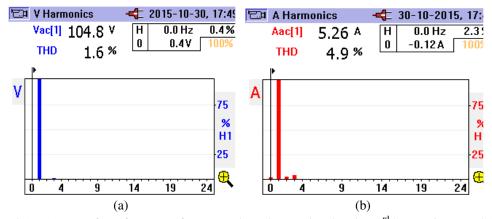

| Fig. 4.12 | Waveform showing THD of terminal voltage harmonics                                                                                                        | 61 |

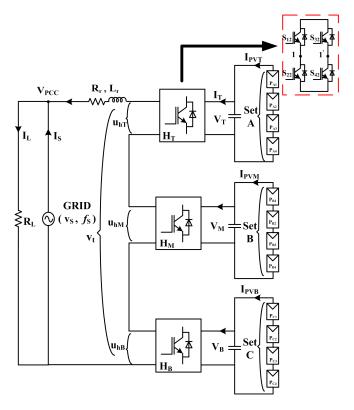

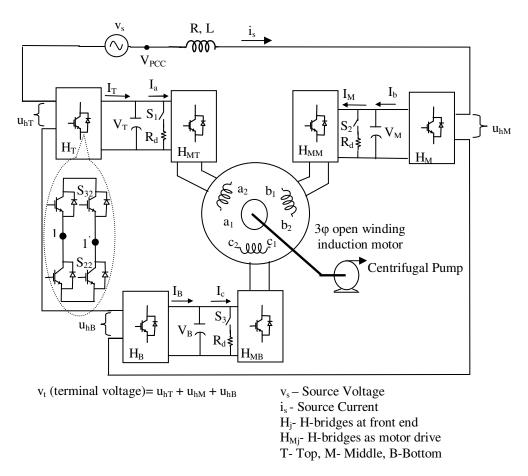

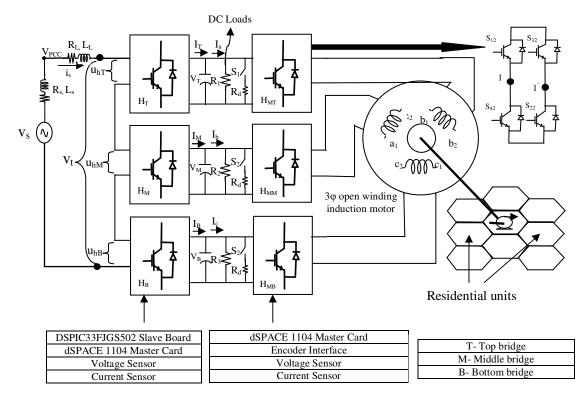

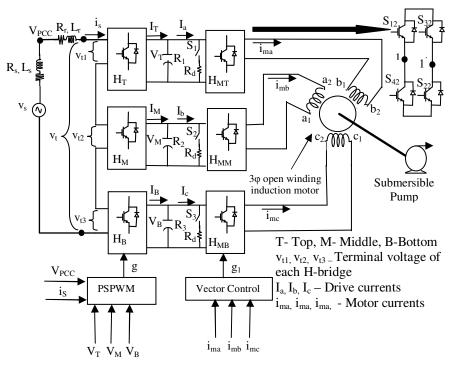

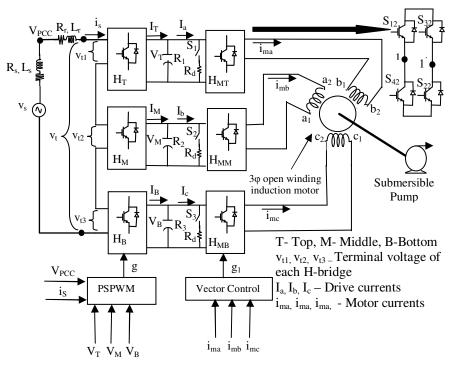

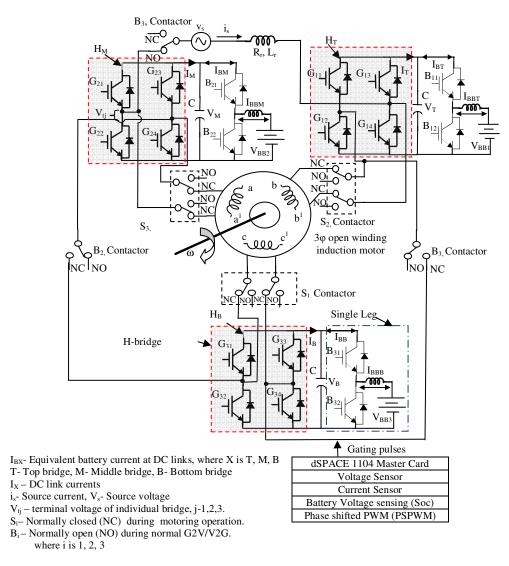

| Fig. 5.1  | System configuration of CCAR feeding OEIM Pump loads                                                                              | 64 |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------|----|

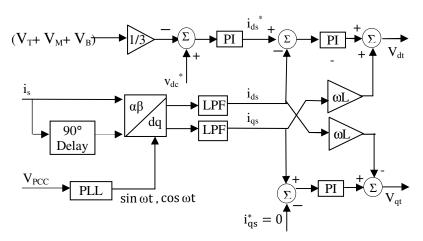

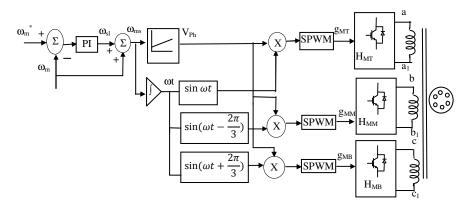

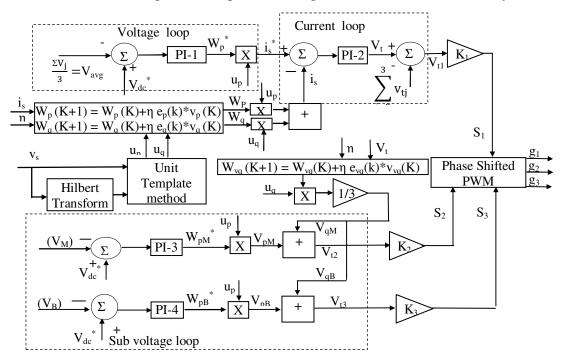

| Fig. 5.2  | Control blocks of proposed CCAR Configuration                                                                                     | 65 |

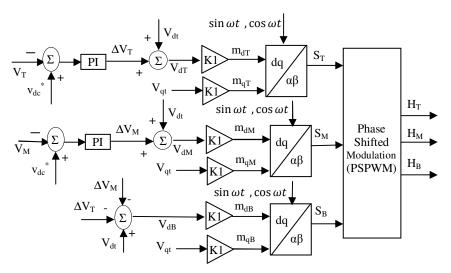

| Fig. 5.3  | Control blocks of proposed CCAR configuration for handling uneven losses across the H- bridges                                    | 66 |

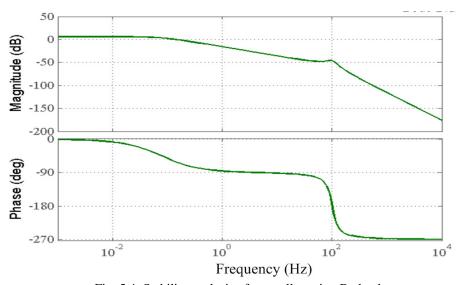

| Fig. 5.4  | Stability analysis of controller using Bode plot                                                                                  | 67 |

| Fig. 5.5  | Control blocks of V/f control of OEIM drive                                                                                       | 68 |

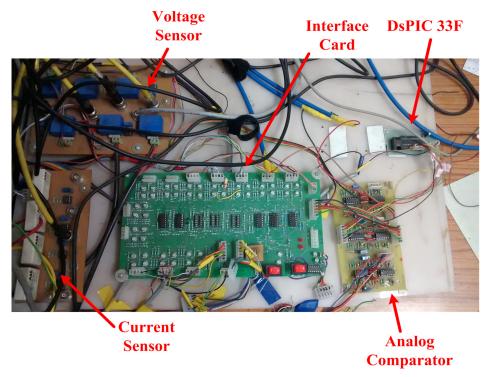

| Fig. 5.6  | PCB's of interfacing, DsPIC33f and control cards                                                                                  | 70 |

| Fig. 5.7  | Experimental hardware unit of cascaded multilevel converter/inverter                                                              | 71 |

| Fig. 5.8  | Open end winding induction motor with digital encoder and fan load                                                                | 72 |

| Fig. 5.9  | Experimental setup of multilevel system showing dSPACE and DSO's                                                                  | 72 |

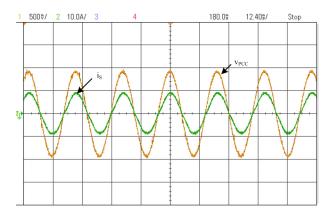

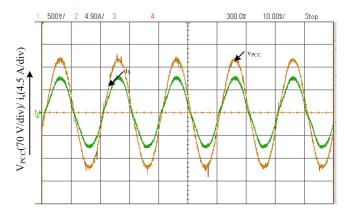

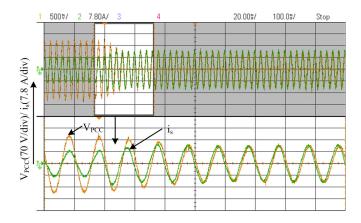

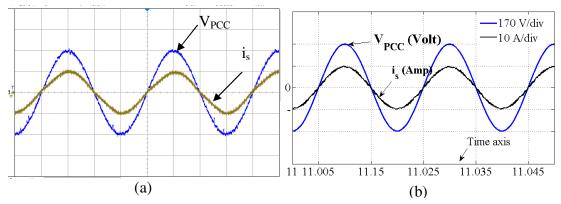

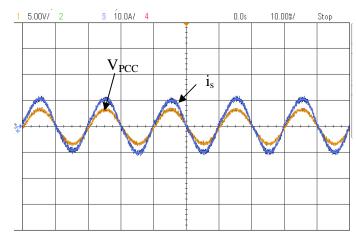

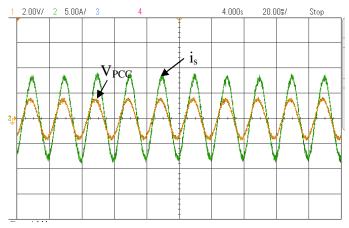

| Fig. 5.10 | (a) Experimental result showing source voltage (170 V/div), and source current (10 A/div)                                         | 73 |

|           | (b) Simulated source voltage, and source current.                                                                                 | 73 |

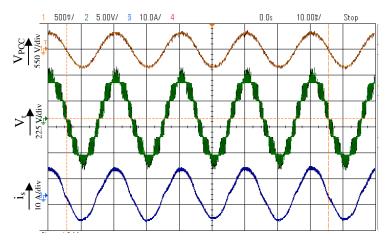

| Fig. 5.11 | (a) Experimental results showing terminal voltage $V_t$ and $\;DC$ link voltages $V_T,V_M$ , $V_B,Time\mbox{-}10$ ms/div          | 73 |

|           | (b) Simulated results showing terminal voltage $V_{t}$ and DC link voltages $V_{T},V_{M},V_{B}$                                   | 73 |

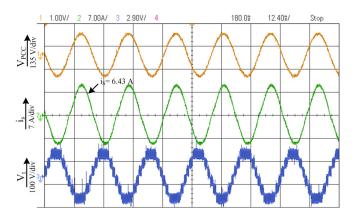

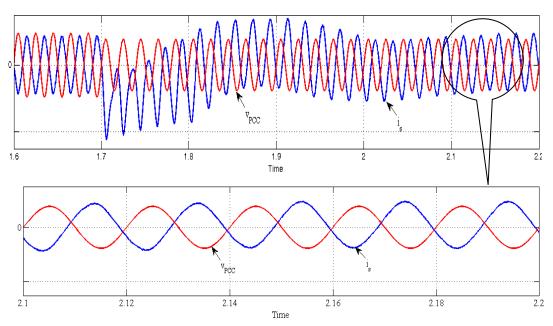

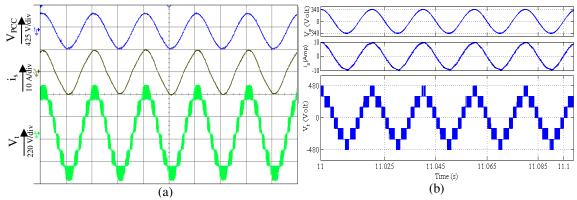

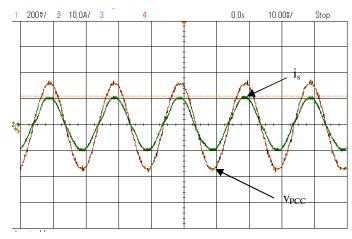

| Fig. 5.12 | (a) Measured zoomed source voltage ( $V_{pcc}$ ), source current ( $i_s$ ) and CCAR input voltage ( $V_t$ ), and time (10 ms/div) | 74 |

|           | (b) Simulated zoomed source voltage ( $V_{pcc}$ ), source current ( $i_s$ ) and CCAR input voltage ( $V_t$ )                      | 74 |

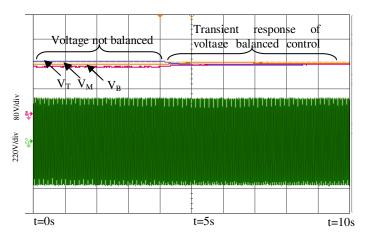

| Fig. 5.13 | Experimental results of DC link voltages $(V_T,  V_M  , V_B)$ and terminal voltage $(V_t)$ showing balanced control scheme        | 75 |

| Fig. 5.14 | Experimental result showing waveforms for                                                                                         |    |

|           | (a) Source current $(i_s)$ , DC link voltages $(V_T, V_M, V_B)$                                                                   | 75 |

|           | (b) LED's load currents ( $I_{R1},I_{R2},I_{R3}$ ) and Motor speed (in rpm)                                                       | 75 |

| Fig. 5.15 | Experimental results showing                                                                                                      |    |

|           | (a) Source voltage ( $V_{\text{pcc}}$ ), source current ( $i_s$ ) and CCAR input voltage ( $V_t$ )                                | 76 |

|           | (b) Source current $(i_s)$ and DC link voltages $(V_T, V_M, V_B)$ (c) motor currents $(i_a, i_b, i_c)$ , motor speed (rpm) under change in motor pump load with change in speed                                               | 76  |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

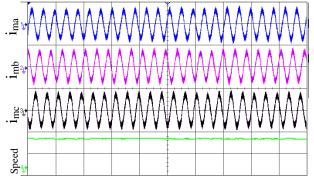

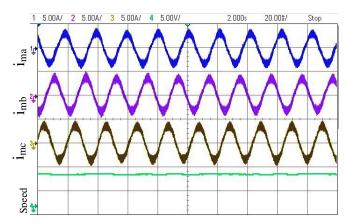

| Fig. 5.16 | Experimental results showing zoomed motor current $i_{ma}$ (5A/div), $i_{mb}$ (5A/div), $i_{mc}$ (5A/div) and speed (1000 rpm/div)                                                                                            | 78  |

| Fig. 5.17 | (a) Waveform showing one DC link voltage $V_{\text{M}}$ and passive load current $I_{\text{R2}}$                                                                                                                              | 78  |

|           | (b) DC link voltages $V_T$ , $V_M$ , $V_B$ measured from Fluke 345                                                                                                                                                            | 78  |

| Fig. 5.18 | (a) Waveform showing THD of source current $I_{R2}$                                                                                                                                                                           | 79  |

|           | (b) THD of CCAR terminal voltage $V_t$                                                                                                                                                                                        | 79  |

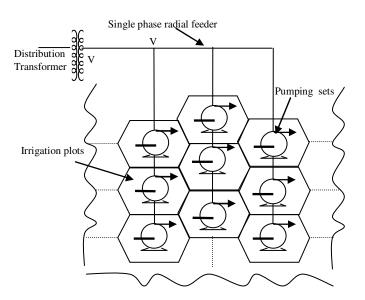

| Fig. 6.1  | Conventional system of pumping                                                                                                                                                                                                | 82  |

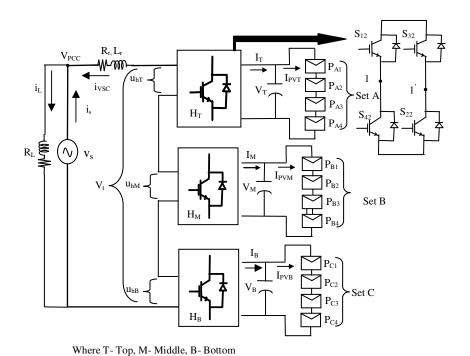

| Fig. 6.2  | Proposed system Configuration for SPL operation                                                                                                                                                                               | 83  |

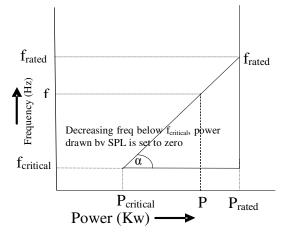

| Fig. 6.3  | Droop curve according to individual capacity of pump load                                                                                                                                                                     | 84  |

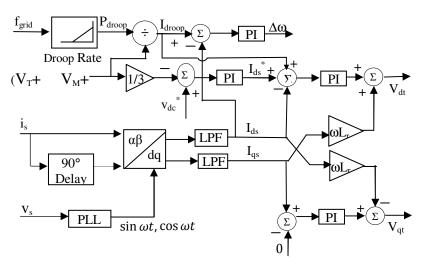

| Fig.6.4   | Control blocks of proposed CMAR+SPL Configuration                                                                                                                                                                             | 86  |

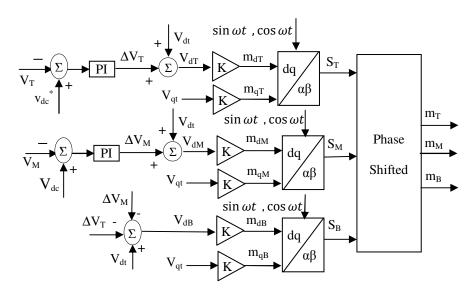

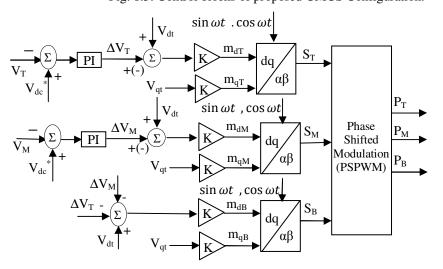

| Fig. 6.5  | Control blocks of proposed SPL+CMAR configuration for switching function generation for each H-bridge incorporating control block set for handling unbalanced loading                                                         | 87  |

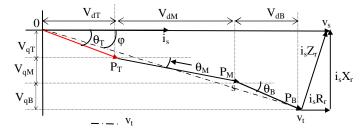

| Fig. 6.6  | Phasor representation of individual voltages in case of unbalanced loading                                                                                                                                                    | 89  |

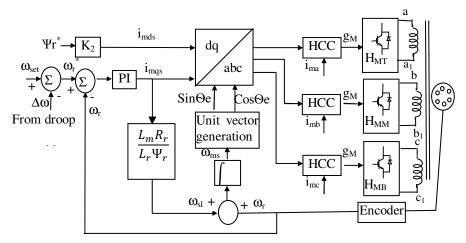

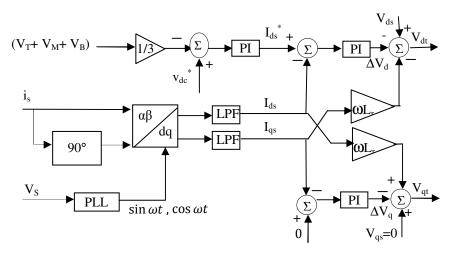

| Fig. 6.7  | Control blocks for Vector control of OEIM drive                                                                                                                                                                               | 92  |

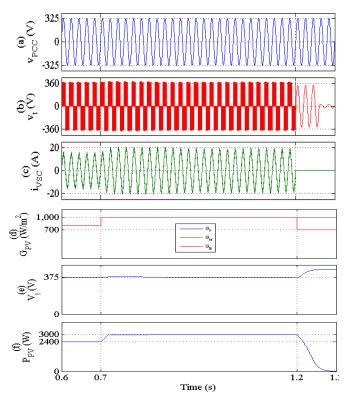

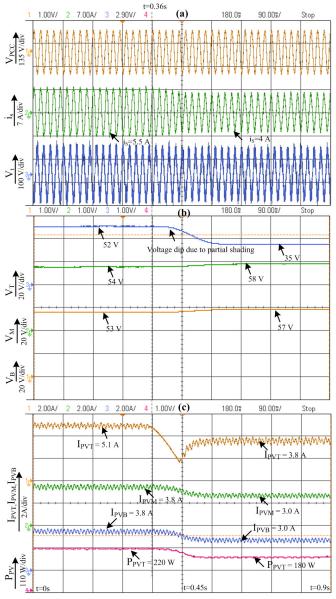

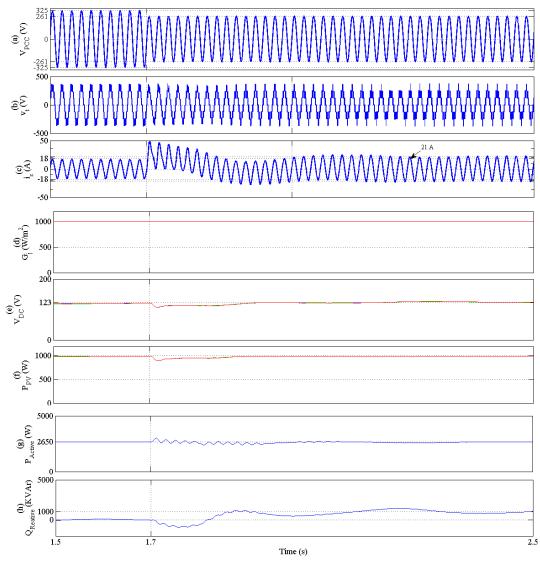

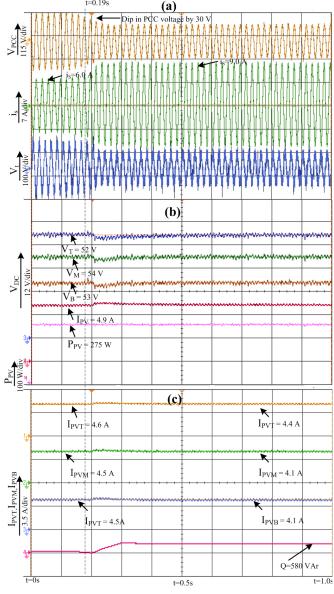

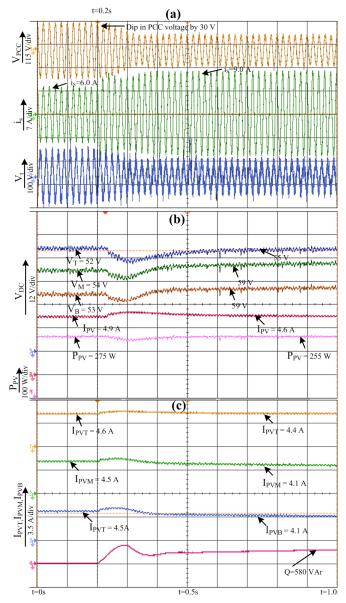

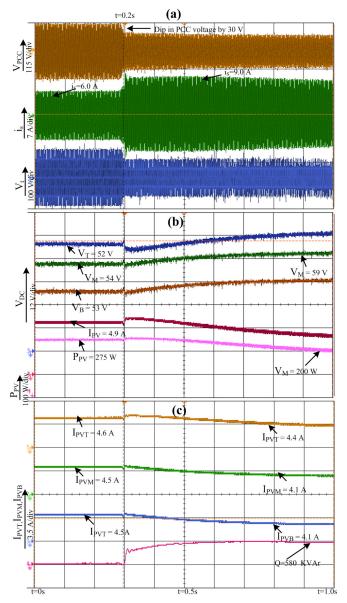

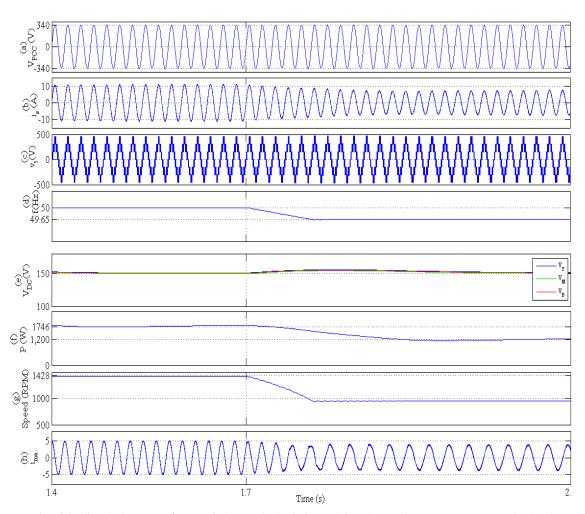

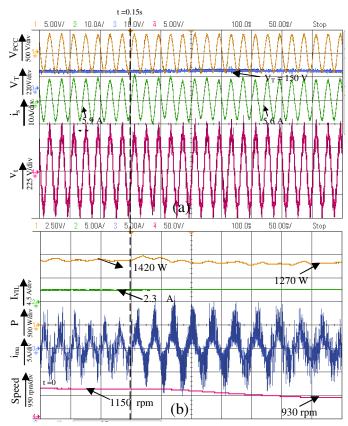

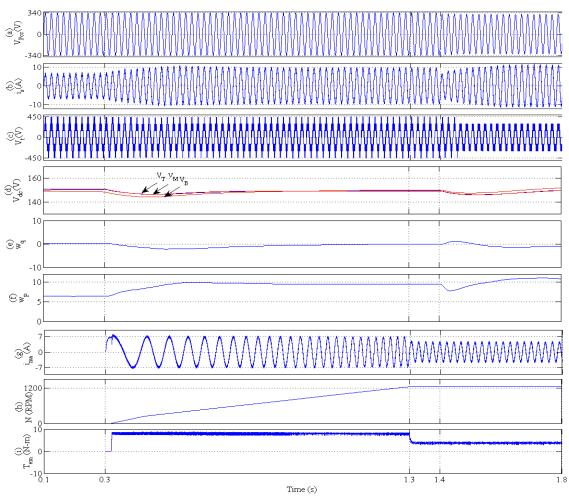

| Fig. 6.8  | Simulation waveforms of SPL unit depicting PCC voltage, Source current, Terminal voltage ( $V_t$ ), Grid frequency (Hz), DC link voltage, Power is drawn from grid by CMAR (P), motor Speed (RPM), Motor current ( $i_{ma}$ ) | 95  |

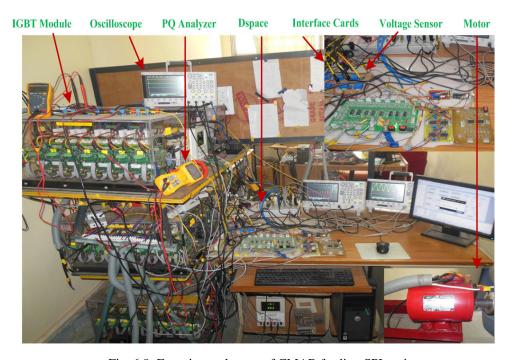

| Fig. 6.9  | Experimental setup of CMAR feeding SPL unit                                                                                                                                                                                   | 97  |

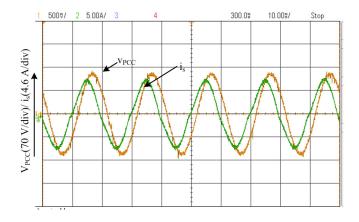

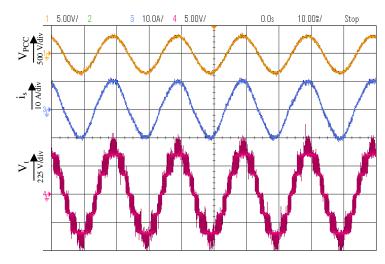

| Fig. 6.10 | Experimental result showing source voltage (500 V/div), and source current (10 A/div)                                                                                                                                         | 98  |

| Fig. 6.11 | Measured zoomed source voltage ( $V_{\text{pcc,}}$ ), source current ( $i_s$ ) and CMAR input voltage ( $V_t$ )                                                                                                               | 98  |

| Fig. 6.12 | Experimental results showing waveforms for DC link voltages, $(V_T,V_M,V_B)$ , terminal voltage and DC link load current- 1 A/div under balanced/unbalanced condition                                                         | 99  |

| Fig. 6.13 | Experimental results showing (a) source voltage $(V_{pcc})$ , source current $(i_s)$ and CMAR input voltage $(V_t)$ (b) DC link voltages $(V_T, V_M, V_B)$ (c) motor currents $(i_a, i_b, i_c)$ , motor speed                 | 100 |

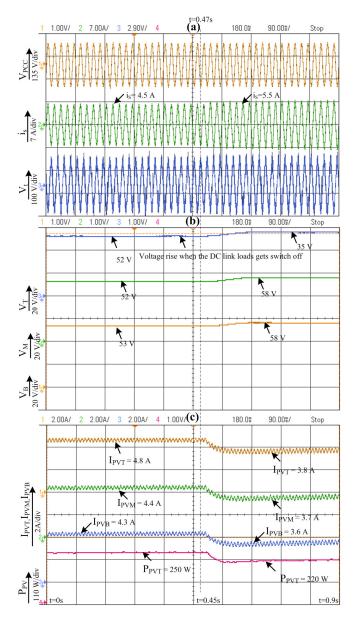

| Fig. 6.14 | Experimental results showing zoomed motor current $i_{\text{ma}}, i_{\text{mb}}, i_{\text{mc}}$ and speed                                                                                                                                                     | 101 |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Fig. 6.15 | Experimental result showing (a) source voltage $(V_{pcc})$ , DC link voltage, source current $(i_s)$ and CMAR terminal voltage $(V_t)$ (b) Power drawn by CMAR (P), VIL current $(I_{VIL})$ , motor current $(i_{ma})$ and speed                              | 101 |

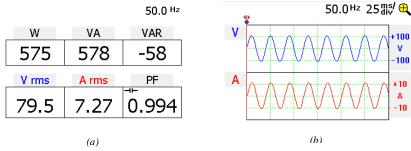

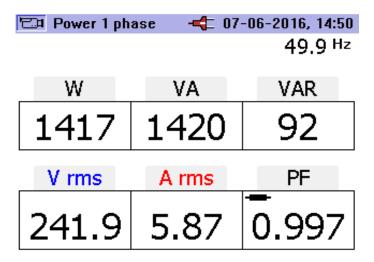

| Fig. 6.16 | Results of power qualuty analyzer FLUKE 345                                                                                                                                                                                                                   | 102 |

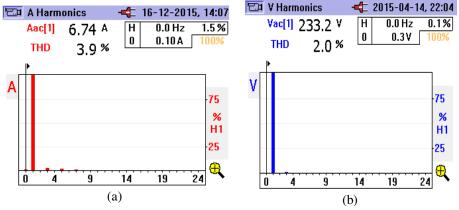

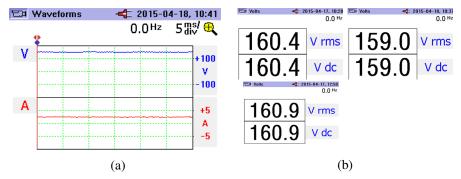

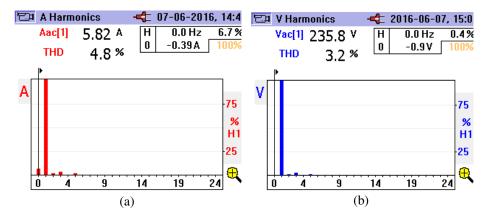

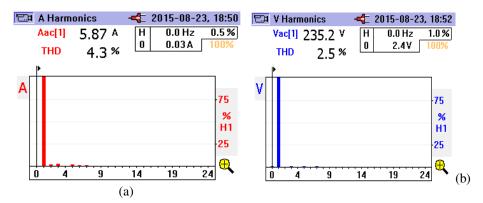

| Fig. 6.17 | (a) Waveform for THD of source current harmonics                                                                                                                                                                                                              | 102 |

|           | (b) THD of CMAR terminal voltage $V_t$ .                                                                                                                                                                                                                      | 102 |

| Fig. 7.1  | Block diagram representation of CMAR feeding Pump drive                                                                                                                                                                                                       | 106 |

| Fig. 7.2  | Adaline based control scheme for CMAR                                                                                                                                                                                                                         | 108 |

| Fig. 7.3  | Phasor representation of individual voltages in case of even/uneven losses                                                                                                                                                                                    | 110 |

| Fig. 7.4  | Phasor representation during transient operation                                                                                                                                                                                                              | 114 |

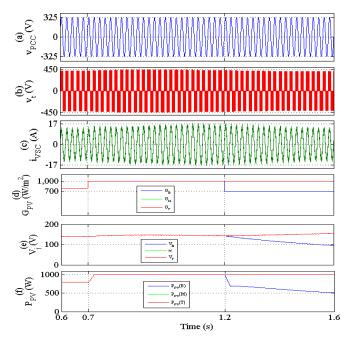

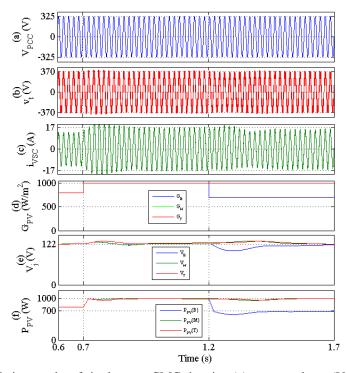

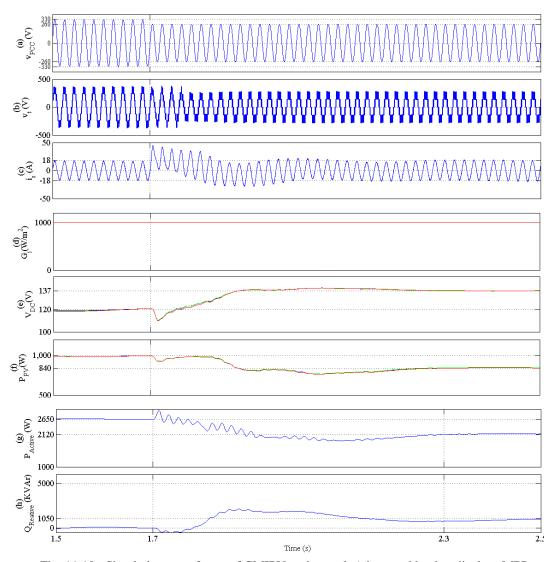

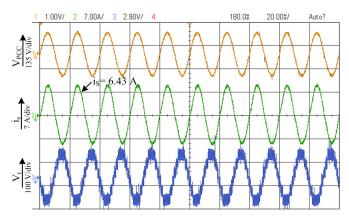

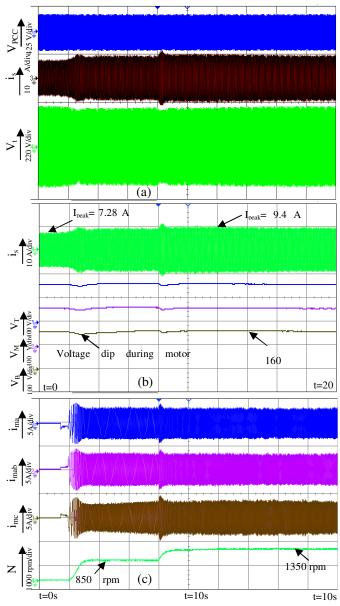

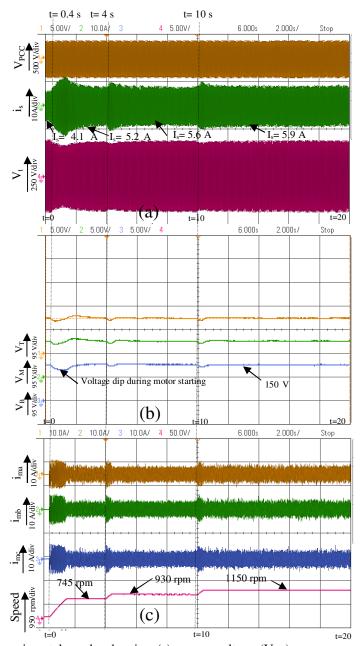

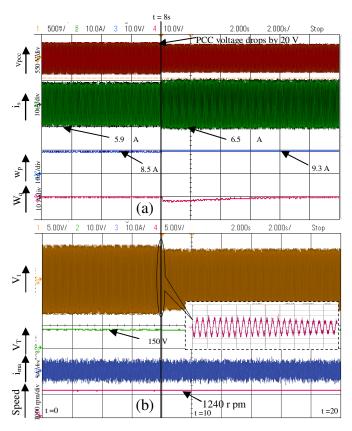

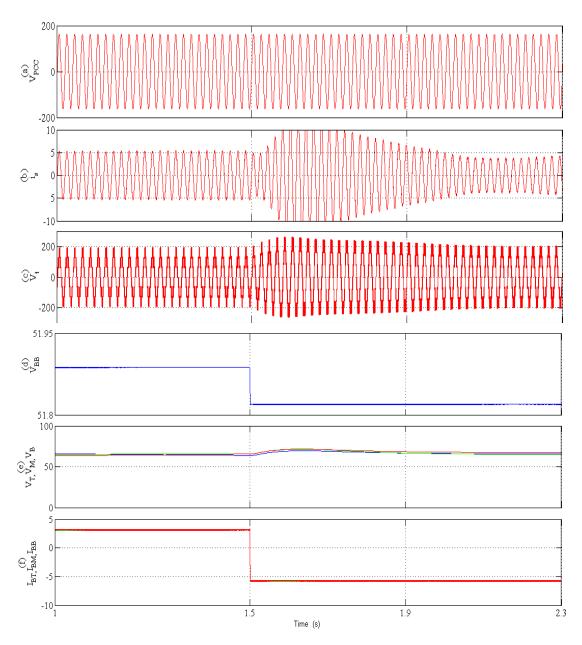

| Fig. 7.5  | Simulation waveforms of CMAR unit depicting PCC voltage ( $V_{PCC}$ ), source current, terminal voltage ( $V_t$ ), DC link voltages, weight components ( $W_p$ , $W_q$ ), speed (rpm), Motor current ( $i_{ma}$ ), Electromagnetic torque ( $T_{em}$ )        | 115 |

| Fig. 7.6  | Experimental result showing source voltage (200 V/div), and source current (10 A/div)                                                                                                                                                                         | 117 |

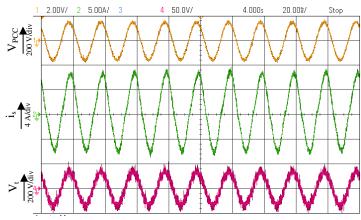

| Fig. 7.7  | Measured source voltage ( $V_{\text{pcc.}}$ ), CMAR input voltage ( $V_{\text{t}}$ ) and source current ( $i_{\text{s}}$ )                                                                                                                                    | 118 |

| Fig. 7.8  | Experimental results showing waveforms for DC link voltages, $(V_T,V_M,V_B)$ , terminal voltage                                                                                                                                                               | 118 |

| Fig. 7.9  | Experimental result of DC link voltages DC link voltages ( $V_T$ , $V_M$ , $V_B$ ) and terminal voltage ( $V_t$ ) showing balanced control scheme                                                                                                             | 119 |

| Fig. 7.10 | (a) Experimental result showing waveforms of PCC voltage ( $V_{PCC}$ ) source current ( $i_s$ ), Weights corresponding to real and reactive component ( $W_{ds}$ , $W_{qs}$ )                                                                                 | 120 |

|           | (b) Terminal voltage ( $V_t$ ), One dc link voltage ( $V_T$ ), motor current ( $i_{nna}$ ), Motor speed (rpm)                                                                                                                                                 | 120 |

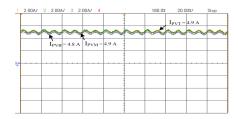

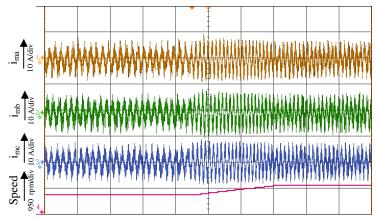

| Fig. 7.11 | Experimental results showing zoomed motor current $i_{\text{ma}}, i_{\text{mb}}, i_{\text{mc}}$ and speed (1000 rpm/div)                                                                                                                                      | 121 |

| Fig. 7.12 | Experimental result showing waveforms of PCC voltage (V <sub>PCC</sub> ) source current (i <sub>s</sub> ), Weights corresponding to real and reactive component (W <sub>st</sub> , W <sub>st</sub> ). Terminal voltage (V <sub>s</sub> ). One do link voltage | 122 |

|           | $(V_T)$ , motor current $(i_{ma})$ , Motor speed $(rpm)$                                                                                                                                                                                                          |     |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Fig. 7.13 | (a) Waveform showing source voltage and source current                                                                                                                                                                                                            | 123 |

|           | (b) Waveform showing DC link voltages and power demanded                                                                                                                                                                                                          | 123 |

| Fig. 7.14 | (a) Waveform for THD of source current                                                                                                                                                                                                                            | 123 |

|           | (b) Waveform for THD of CMAR terminal voltage $V_{t}$                                                                                                                                                                                                             | 123 |

| Fig. 8.1  | Block diagram representation for Multimode operation using CMCS                                                                                                                                                                                                   | 126 |

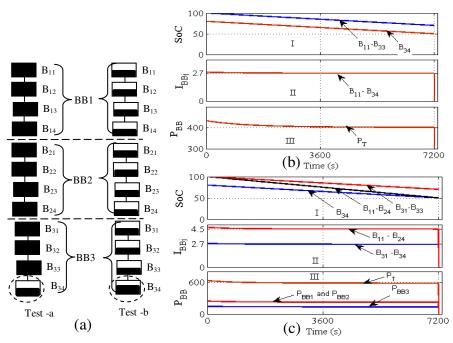

| Fig. 8.2  | (a) Battery stacks for G2V/V2G                                                                                                                                                                                                                                    | 128 |

|           | (b) Test - A centralized control for V2G                                                                                                                                                                                                                          | 128 |

|           | (c) Test – A CMCS based split control for V2G                                                                                                                                                                                                                     | 128 |

| Fig. 8.3  | (a) Phasor diagram for charging operation maintaining UPF                                                                                                                                                                                                         | 130 |

|           | (b) Phasor diagram for discharging operation maintaining UPF                                                                                                                                                                                                      | 130 |

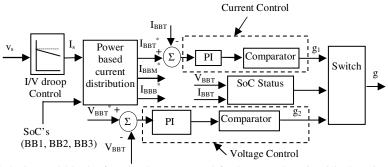

| Fig. 8.4  | Control blocks for I/V droop control for battery charging/discharging operation in CC and CV mode                                                                                                                                                                 | 131 |

| Fig. 8.5  | Control blocks of proposed CMCS Configuration                                                                                                                                                                                                                     | 135 |

| Fig. 8.6  | Control blocks of proposed CMCS configuration for even /uneven charging/discharging                                                                                                                                                                               | 135 |

| Fig. 8.7  | Phasor representation of individual voltages in case of unbalanced loading                                                                                                                                                                                        | 136 |

| Fig. 8.8  | Simulation waveforms of CMCS unit depicting PCC voltage in volt ( $V_{PCC}$ ), Source current in Amp, Terminal voltage in Volt ( $V_t$ ), Battery voltage in Volt ( $V_{BB}$ ), DC link voltages in volt ( $V_T$ ), Battery charging current in Amp ( $I_{BT}$ ). | 138 |

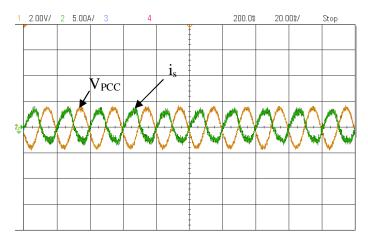

| Fig. 8.9  | Experimental result showing source voltage (200 V/div), and source current (4 A/div)                                                                                                                                                                              | 140 |

| Fig. 8.10 | Measured zoomed source voltage (V $_{\text{pcc,}}$ ), source current (i $_{\text{s}}$ ) and CMAR input voltage (V $_{\text{t}}$ )                                                                                                                                 | 140 |

| Fig. 8.11 | Experimental result showing source voltage (200 V/div), and source current (4 A/div) during discharging for V2G support                                                                                                                                           | 141 |

| Fig. 8.12 | Experimental result showing waveforms for change in battery voltage during discharging mode depicting - Battery currents ( $I_{BBT}$ , $I_{BBM}$ , $I_{BBB}$ ), Battery voltage ( $V_{BB}$ )                                                                      | 141 |

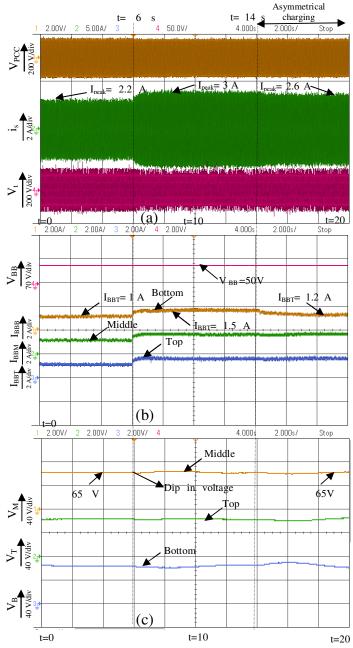

| Fig. 8.13 | Experimental results showing charging mode of operation (a)                                                                                                                                                                                                       | 142 |

|           | source voltage ( $V_{pcc}$ ), source current ( $I_s$ ) and CMCS input voltage ( $V_t$ ) (b) Battery currents ( $I_{BBT}$ , $I_{BBM}$ , $I_{BBB}$ ), (c) DC link voltages ( $V_T$ , $V_M$ , $V_B$ )                                                                                                                    |     |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Fig. 8.14 | Experimental results showing discharging mode of operation(V2G) support (a) source voltage ( $V_{pcc}$ ), source current ( $i_s$ ) and CMCS input voltage ( $V_t$ ) (b) Battery currents ( $I_{BBT}$ , $I_{BBM}$ , $I_{BBB}$ ), (c) DC link voltages ( $V_T$ , $V_M$ , $V_B$ )                                        | 144 |

| Fig. 8.15 | Experimental result showing zoomed waveforms for Battery currents ( $I_{BBT}$ , $I_{BBM}$ , $I_{BBB}$ ), Battery voltage ( $V_{BB}$ ) during discharging                                                                                                                                                              | 145 |

| Fig. 8.16 | Experimental result showing waveforms for step transition from charging to discharging mode                                                                                                                                                                                                                           | 146 |

|           | (a) DC link voltages (V <sub>T</sub> ,V <sub>M</sub> ,V <sub>B</sub> )                                                                                                                                                                                                                                                | 146 |

|           | (b) Battery currents ( $I_{BBT},I_{BBM},I_{BBB}$ ), Battery voltage ( $V_{BB})$                                                                                                                                                                                                                                       | 146 |

| Fig. 8.17 | (a) Waveform for THD of source voltage harmonics showing $3^{\rm rd}$ harmonic around 1.2% of fundamental                                                                                                                                                                                                             | 146 |

|           | (b) THD of source current harmonics showing $3^{\rm rd}$ harmonic around 4.4% of fundamental                                                                                                                                                                                                                          | 146 |

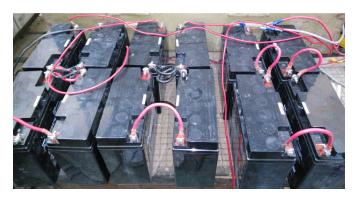

| Fig. 8.18 | Battery stacks used for experimental setup in CMCS.                                                                                                                                                                                                                                                                   | 147 |

| Fig. 9.1  | Block diagram representation of SSSVC                                                                                                                                                                                                                                                                                 | 149 |

| Fig. 9.2  | Flowchart for vehicle charging/discharging control of SSSVC unit.                                                                                                                                                                                                                                                     | 151 |

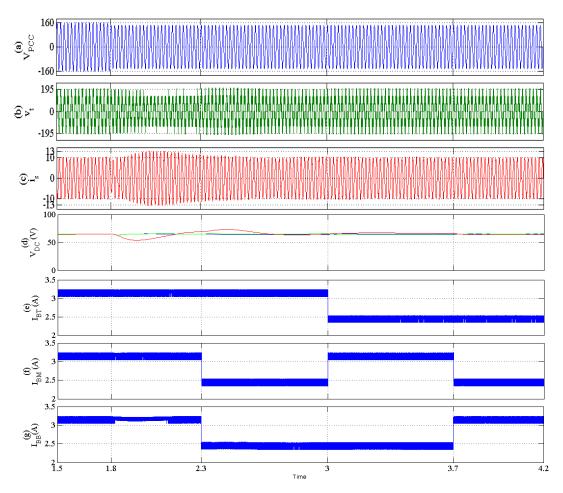

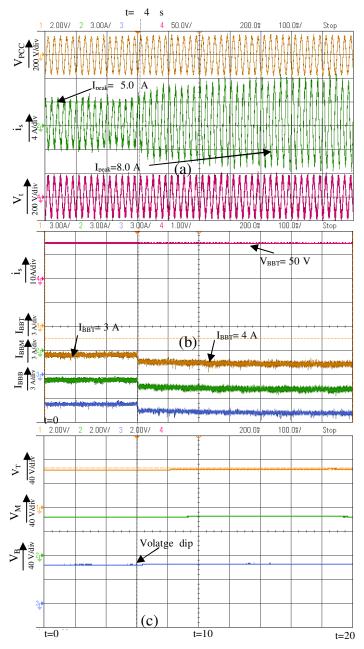

| Fig. 9.3  | Simulation waveforms of SSSVC unit depicting PCC voltage in volt ( $V_{PCC}$ ), Source current in Amp, Terminal voltage in Volt ( $V_{t}$ ), Battery voltage in Volt ( $V_{BB}$ ), DC link voltages in volt ( $V_{T}$ ), Battery charging current in Amp ( $I_{BT}$ ) under cyclic control                            | 153 |

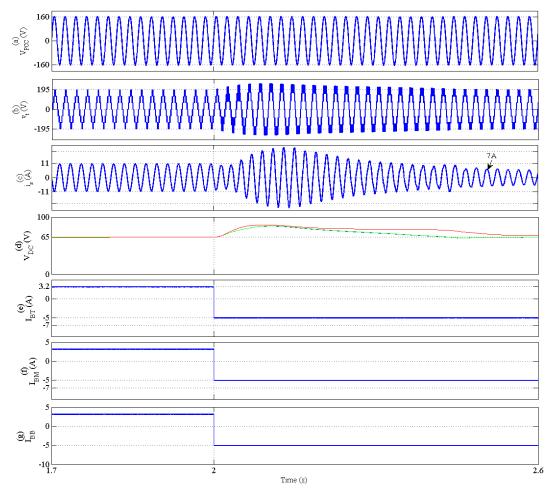

| Fig. 9.4  | Simulation waveforms of SSSVC unit depicting PCC voltage in volt ( $V_{PCC}$ ), Source current in mp, Terminal voltage in Volt ( $V_{t}$ ), Battery voltage in Volt ( $V_{BB}$ ), DC link voltages in volt ( $V_{T}$ ), Battery charging current in Amp ( $I_{BT}$ ) for transition from Charging to Discharging Mode | 154 |

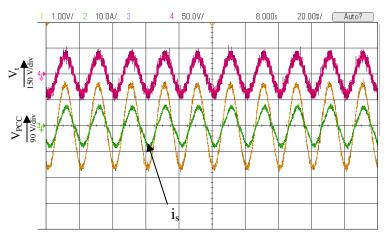

| Fig. 9.5  | Measured source voltage ( $V_{pcc.}$ ), terminal voltage ( $V_t$ ) and source current ( $i_s$ :10A/div)                                                                                                                                                                                                               | 156 |

| Fig. 9.6  | Experimental result showing waveforms for step transition from charging to discharging mode (a) DC link voltages $(V_{DC1}, V_{DC2}, V_{DC3})$ (b) Battery currents $(I_1,  I_2,  I_3)$                                                                                                                               | 157 |

| Fig. 9.7  | Experimental results showing (a) source voltage ( $V_{pcc}$ ), source current ( $i_s$ ) and terminal voltage ( $V_t$ ) (b) DC link voltages ( $V_{DC1}$ , $V_{DC2}$ , $V_{DC3}$ ) (c) Vehicle battery currents ( $I_1$ , $I_2$ , $I_3$ ) for cyclic control of SSSVC                                                  | 158 |

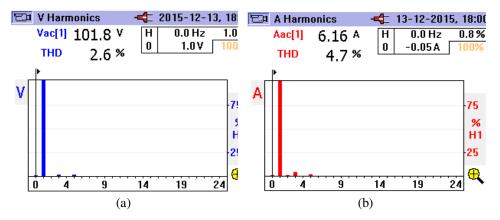

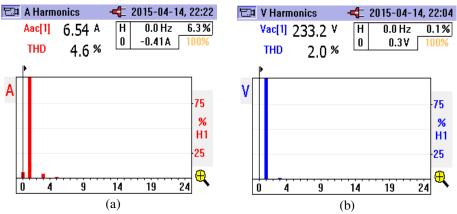

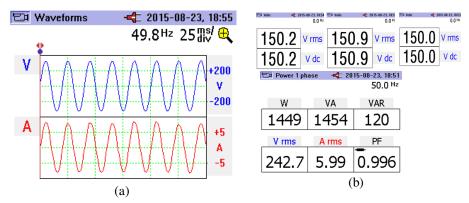

| Fig. 9.8   | (a) Waveform for THD of source voltage                                                                                                                                                                                                                                             | 159 |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|            | (b) THD of source current harmonics for SSSVC                                                                                                                                                                                                                                      | 159 |

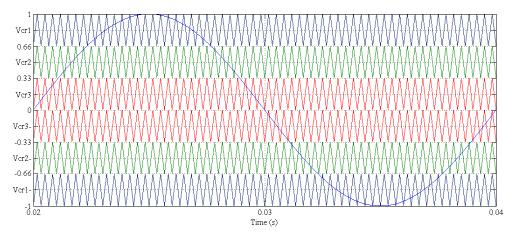

| Fig. 10.1  | Single phase single stage PV cascaded multilevel inverter                                                                                                                                                                                                                          | 161 |

| Fig. 10.2  | Conventional 2 level single stage single phase PV system                                                                                                                                                                                                                           | 161 |

| Fig. 10.3  | Conventional 2 level double stage single phase VSC – PV system                                                                                                                                                                                                                     | 162 |

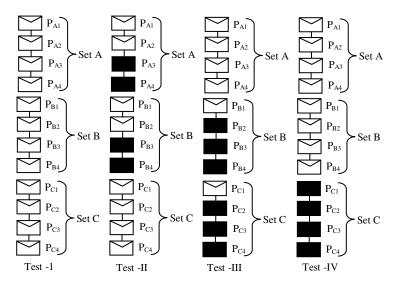

| Fig. 10.4  | PV panel arrangement for different shading condition                                                                                                                                                                                                                               | 163 |

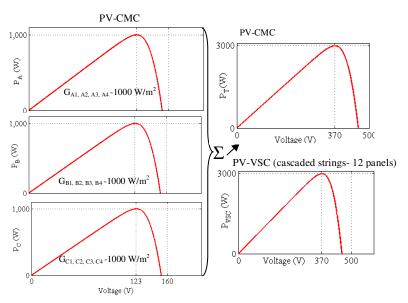

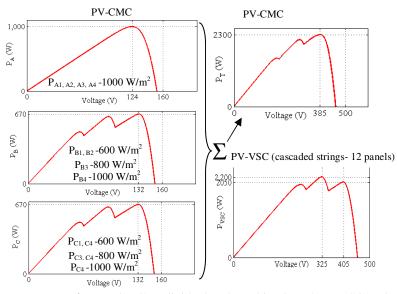

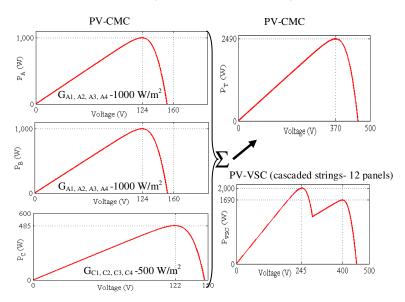

| Fig. 10.5  | P-V curves for PV-CMC(Individual and combined) and PV-VSC                                                                                                                                                                                                                          | 164 |

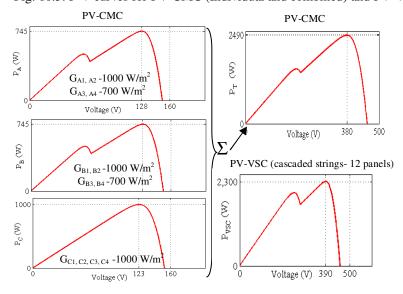

| Fig. 10.6  | P-V curves for PV-CMC(Individual and combined) and PV-VSC under shading                                                                                                                                                                                                            | 164 |

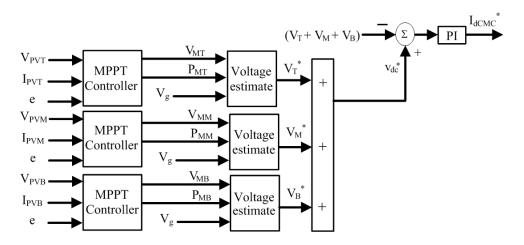

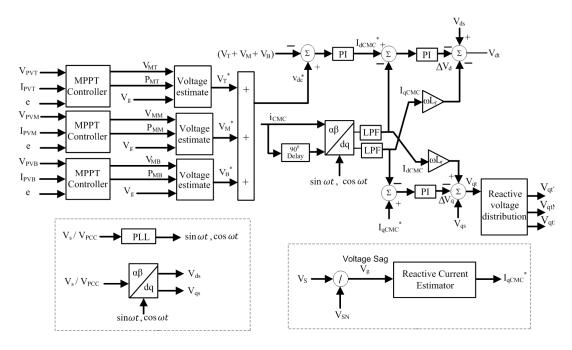

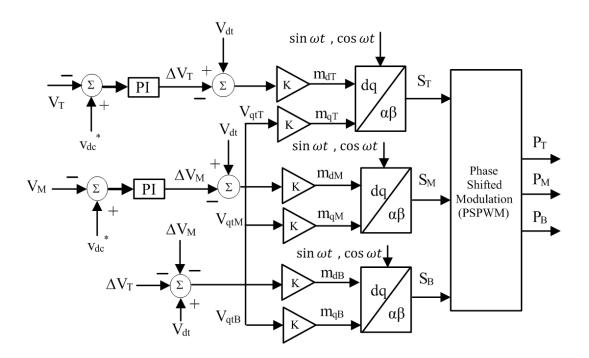

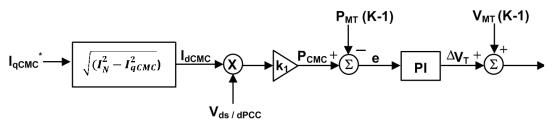

| Fig. 10.7  | P-V curves for PV-CMC(Individual and combined) and PV-VSC under shading                                                                                                                                                                                                            | 165 |